Phono Equalizer

初段パラ構成平衡入力アンプ

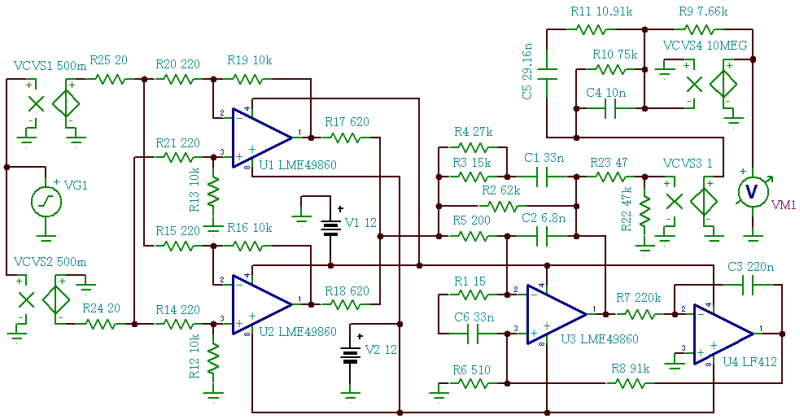

今回設計したのは下の回路です。電源は省略してありますが、正負の三端子レギュレータで各OP-AMPのVCCとVEEに±12Vを供給しています。

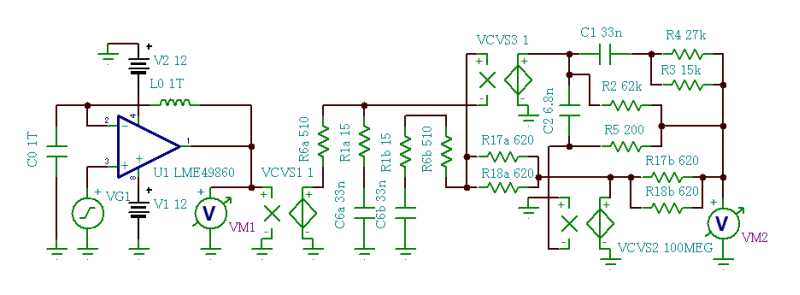

下の回路図はTINA-TIでのシミュレーション用のもので、入力はDL-103の直流抵抗40Ωと等価のバランス信号源を出力には逆RIAA特性となる回路を接続しています。 また各OP-AMPのVCCとVEEには±12Vの電圧源を接続しています。

初段のアンプは差動アンプをパラレル構成にして抵抗で加算しています。このサミング抵抗は次段反転NF-EQアンプの入力抵抗も兼ねています。

- ゲイン

- 初段アンプのゲインはトータルゲインを次段の反転NF型EQとどう配分するかによって決まります。 トータルゲインは一般のRIAAイコライザを34dB(50倍)とするとDL-103の出力をブーストするのに必要な24dBを加えた58dBが目安になります。

- R14,R15,R20,R21(=220Ω)

- これら差動増幅器の入力抵抗はDL-103の出力に対し2s-2pとなり、それぞれの抵抗値はDL-103の負荷抵抗に一致します。 DL-103の負荷抵抗の最小値は100Ωですから、抵抗値は少なくともこの値以上でなければなりません。

- R12,R13,R16,R19(=10kΩ)

- 前項の差動増幅器の入力抵抗とこれらの抵抗の比でアンプのゲインが決まります。

- R17,R18(=620Ω)

- 2個パラの初段アンプの出力を加算するための抵抗です。この抵抗は次段反転NF-EQアンプの入力抵抗も兼ねています。LM4562/LME49720の負荷に相当し600Ω以上とします。

- 安定性

- LM4562/LME49720のGB積は55MHzと広帯域です。ここでは位相補償はしておりませんが、初段アンプのゲインは30dB以上あるためゲイン交点の周波数は1MHz代で、GB積10MHzクラスのOPアンプをゲイン0dBの電圧バッファとして使うよりはるかに安定なはずです。初段アンプのLTspiceによる周波数特性のシミュレーションを下に示します。

- ゲイン

- 高域のダイナミック・レンジを最大限確保するためには20kHzで0dB以上、RIAA特性から1kHzでは最低20dBは必要です。

- R3,R4(=15kΩ//27kΩ),C1(=0.033µF)

- ターンオーバ(318µsec)の時定数です。(15kΩ//27kΩ)*0.033µF =318.2µsec 定数としては十分です。

- R2(=62kΩ)

- この抵抗とR17,R18で反転NF型EQのゲインがほぼ決まります。

- R5(=200Ω),C2(=6800pF)

- DCサーボを除いた残りのRIAAネットワーク素子です。これらR2,R3,R4,R5,C1,C2およびR17,R18で決まる極(pole)の時定数は 2984µsecと75.04µsecです。

- R6(=510Ω)

- この抵抗がU3(LM4562/LME49720)の非反転入力側の信号源抵抗、つまりバイアス電流による入力オフセット電圧をほぼ決定します。いくらDCサーボによって出力にオフセット電圧がでないとはいっても、積分器(LF412)の出力は有限値です。オフセットは極力小さくなるよう配慮します。ここで抵抗値の大きいR2とR8はネグって R6≒(R17//R18)+R5 とします。

- R7(=220kΩ),R8(=91kΩ),C3(=0.22µF)

- R2,R3,R4,R5,C1,C2およびR17,R18で決まる低域側の極(pole)2984µsec を3180µsecに移動させるには、三次方程式の数値解を求めること(詳細は省略)により、積分器の時定数を 9.52secにすればよいことが分かります。この結果から R7*C3*R8/R6=9.52sec となるように定数を決定します。220k*0.22µ*100k/510=9.49 なのでR7=220kΩ,C3=0.22µFなら R8の最適値は100kなのですが、DCサーボによるハイパスのfcが高めになったので、低域のレベルが下がり気味になり、これを補正するため 91kΩとしています。

- R1(=15Ω),C6(=0.1µF → 0.033〜0.01µF)

- このR1,C6とR6(=510Ω)がラグ・リードフィルタを形成します。極(pole)の周波数は fc=1/(2π(R1+R6)C6)=30.3kHz → 92kHz〜303kHz また、零(zero)の周波数は fc=1/(2πR1C6)=106kHz → 332kHz〜1.06MHz になります。またゲイン交点の周波数は GBW×R1/(R1+R6)=1.57MHz で、初段アンプのゲイン交点とほぼ同じ周波数に設定します。

反転NF型EQ

設計の基本部分は反転NF型RIAA-EQで説明しています。 ただしRIAAネットワークの定数は変更しています。

DCサーボ

設計の基本部分はDCサーボで説明しています。

位相補償

- 一巡ループゲイン

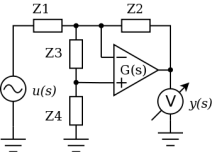

- 位相余裕を確認するために、TINA-TIを使って一巡ループのボード線図の作成を試みます。

上回路の伝達関数は

一巡ループゲインをH(s)とすると上の伝達関数から

ここで

, , ,

(ただしT1=2984µsec, T2=318.2µsec, T3=75.04µsec, a=200)とおくと、以下のように

«LME49720(OpenLoop) → ラグ・リードフィルタ → 逆RIAA+ラグ・リードフィルタのフィードバック・ループ»

の形に書き換えられます。

元の回路図のリファレンス番号と下の一巡ループシミュレーション用回路のリファレンス番号との対応を列挙します。

- R1(=15Ω) → R1, R11

- R6(=510Ω) → R6, R10

- R17=R18(=620Ω) → R12, R13, R14, R15

- C1(=0.1µ, 33n, 10nF) → C3, C4

- 逆RIAAフィルタ → E1, C1, C2, R2, R3, R4, R5, R14, R15

- G(s) → U1 (R8とR9でGain≤100dBに制限)