● 実験テーマ122

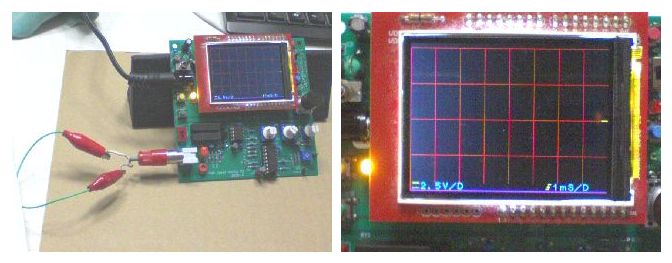

実験テーマ122:「PIC24FGCシリーズによる高速オシロの実験_4」

(2段階ATT回路を改善し10進DSWのみで切替られるようにしました。またKiCadで、_V2としてP板化しました。)

■ 2020.2.25

・「ATT回路の改善」をテーマに実験してみる。

<背景>

・2016/7の、JA1WBYさんのHPに、私の設計した高速オシロの、ATT回路改造記事がアップされた。

この時、JA1WBYさんが作られたP板と改造に使われた、フォトMOSリレーIC:AQW214を頂いていて手元にある。

テーマ121が一段落して次何にしようかと思っていたのだが、前々から気になっていた、JA1WBYさんの

記事を参考に私自身でも試してみようと思う。

・まずはこの部分の実験回路図を作成(前に作った治具基板があるので、それを改造しようと思う。)

そして実験が上手く行ったら、KiCad(10x8cmMaxのEagleではスペース的に厳しい。10x10cmで行く。)

で、_V2としてP板化しようと考えている。

この際、ロータリディップSWの位置を操作し易い位置にする。

(ユニバーサル製作の時は、改造に改造を重ねて作った為、QVGAの直近に位置している為非常に回しにくくなっている。)

あと、フォトMOSリレーICでなく、メカ接点のリレーを使うのが容量の点などから理想的なので、

秋月販売の逆電圧防止用ダイオード内蔵型の、リードリレー「SS1A05D」を使うことにした。

ドライブには、FETを使うのが簡単で良さそう。

尚、回路図は、このページ末尾にアップしましたので参照してください。

今回、1/200(10V/D)を追加しました。

また、回路動作については、回路図中の「ATT回路動作テーブル」を参照してください。

■ 2020.2.28

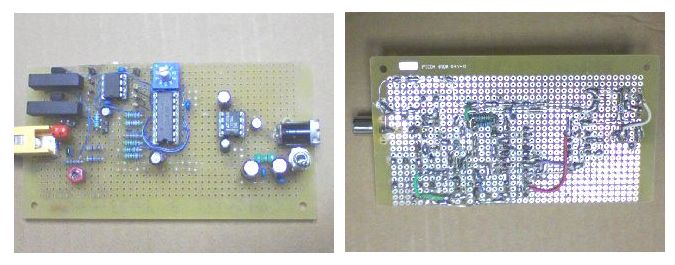

・治具基板の改造が済んだ。

■ 2020.2.29~ 2020.3.1

・動作確認開始

(1) 電源電圧チェック

① IC未実装(LTC1144のみ実装)

+5V→ 5.22V

-5V→ -5.22V

各ICソケット・リレーソケットピンに正しく電源供給されているか?→

OK

② IC全て実装

+5V→ 5.22V

-5V→ -5.02V

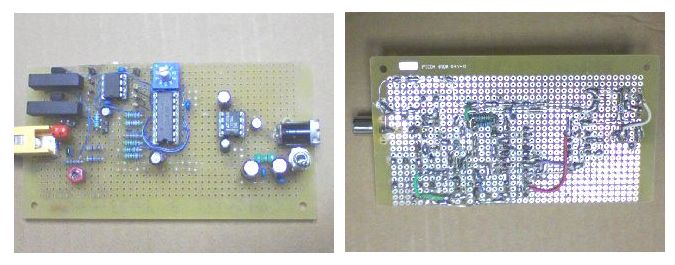

(2) ATT確度・F特確認(Easy FRA V4にて)

下写真の通リ、良さそうである。

尚、全てのレンジが画面中に収まらないので、0dB点をシフトし、10dBを0dBとして測定しました。

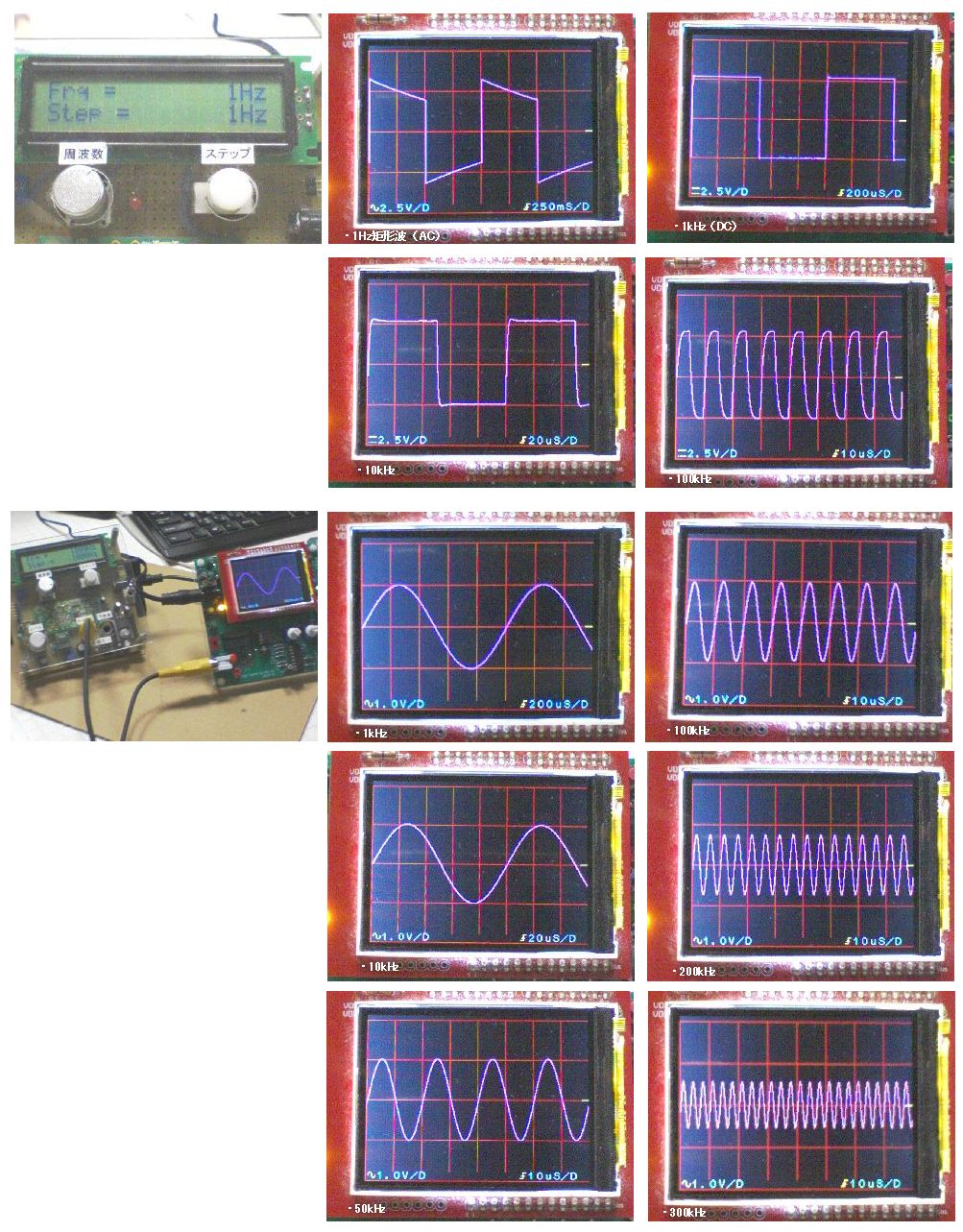

(3) 矩形波出力確認

下写真の通リ、良さそうである。

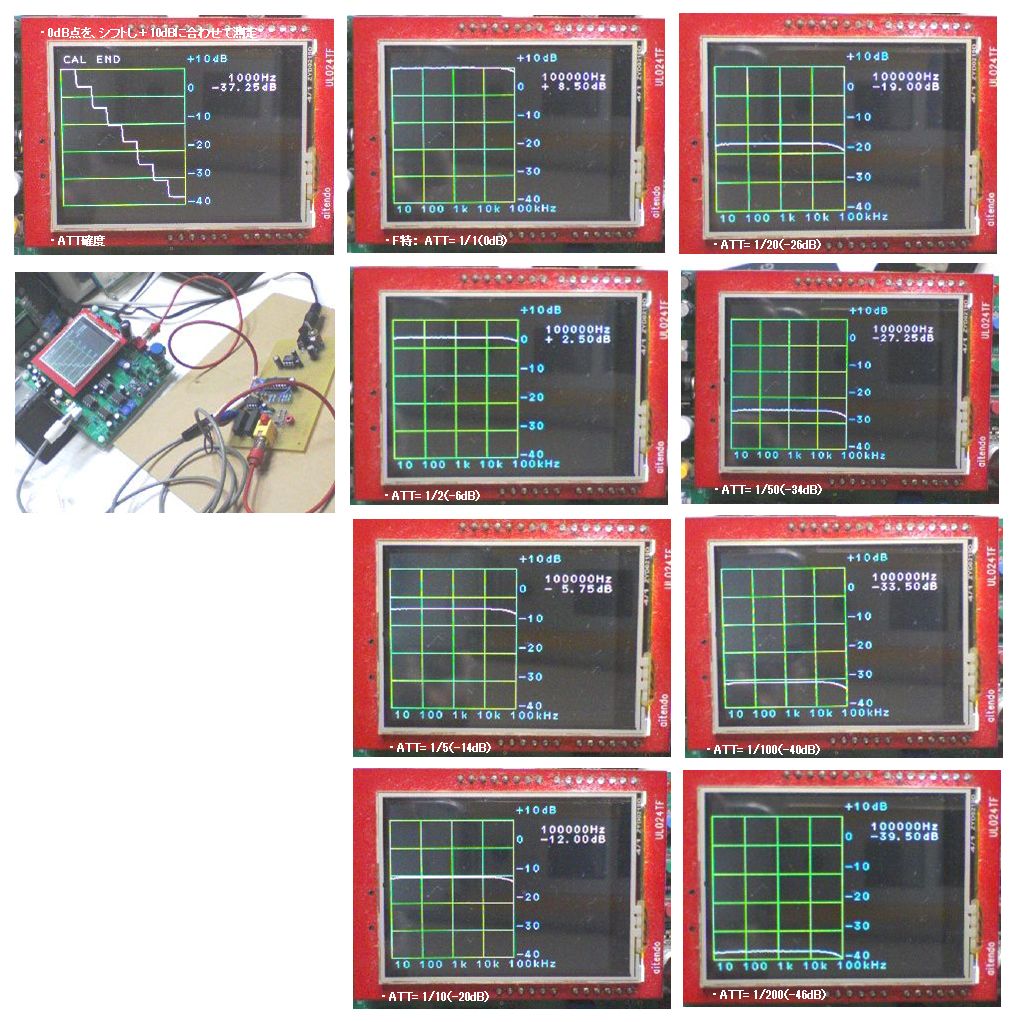

(4) サイン波入力でのATT確認

下写真の通リ、良さそうである。

■ 2020.3.4

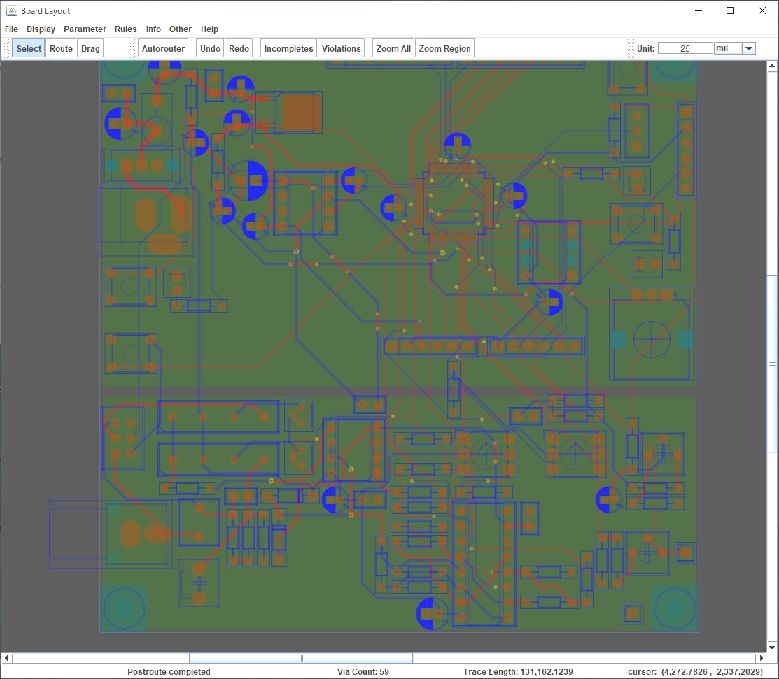

・「High_Speed_Oscillo_V2」プロジェクト開始。

KiCadにてP板設計。

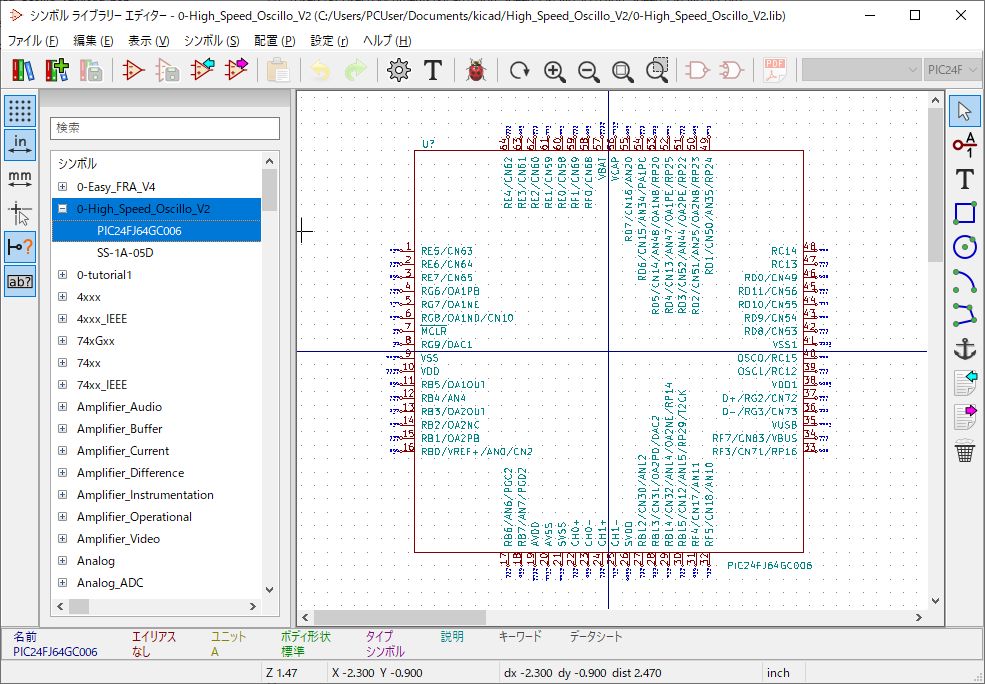

・KiCadを久々にいじる。

まずは、新規登録が必要か否か?を判断するために、ライブラリを覗いて、既成のパーツの中にあるかどうか探してみる。

(1) 新規部品と思われる部品

① PIC24FJ64GC006(64TQFP 0.5mmピッチ)

・KiCad標準既成だと、ライブラリ名:MCU_Microchip_PIC24の中だが、PIC24FV32KA304-IPTしかなかった。

多分、フットプリントはあるはずなので、シンボルのみ新規作成することにした。

→ フットプリントを調べた。 200308

Package_QFP- TQFP-64_10x10mm_P0.5mmが使える。

② MCP6022(DIP 8pin)

・KI-CAD標準既成だと、ライブラリ名:Amplifier Operationlの中だが、ずばりは無かった。

LM2904と同じピン番なのでコピーして、コンポーネント名を変更することにした。

フットプリントはあるはず。

→ フットプリントを調べた。 200308

8pinICソケット使用:D(幅方向のピン間ピッチ)= 300mil= 7.62mmタイプ→ 標準にあった。

Package_DIP-DIP-8_W7.62mm_Socket

③ TC4051BP(DIP 16pin)

・これはあったので、そのまま使える。

ライブラリ名:4xxx

シンボル名:4051

④ 10進ロータリーDIP SW:ERD210RSZ(DIP 6pin)秋月ツマミ付き

・これはあったので、そのまま使える。

ライブラリ名:Switch

シンボル名:SW_Coded_SH-7010(コパル電子の型番)

・フットプリントは要調査

→ 既成標準に互換寸法の有り、コピーして使用:Button_Switch_THT- Nidec_Copal_SH-7010C 追記:200315

<追記:200327>

→ SH-7010(コパル電子):body外形寸法xy=7.3x7.1mm/ 取付けピッチxy:7.62±5mm(2.54x3) x 5.08mm(2.54x2)

ERD210RSZ(秋月ツマミ付き):body外形寸法xy=10x10mm/ 取付けピッチxy:7.62±5mm(2.54x3) x 5.08mm(2.54x2)

上記の通リ、取付けピッチは同じだが、コパル電子の方が外形が、やや小さい。配置する時、周辺部品との位置関係に注意

⑤ 16進ロータリーDIP SW:ERD216RSZ(DIP 6pin)秋月ツマミ付き

・これはあったので、そのまま使える。

ライブラリ名:Switch

シンボル名:SW_Coded_SH-7050(コパル電子の型番)

・フットプリントは要調査

→ 既成標準に互換寸法の有り、コピーして使用:Button_Switch_THT- Nidec_Copal_SH-7010C 追記:200315

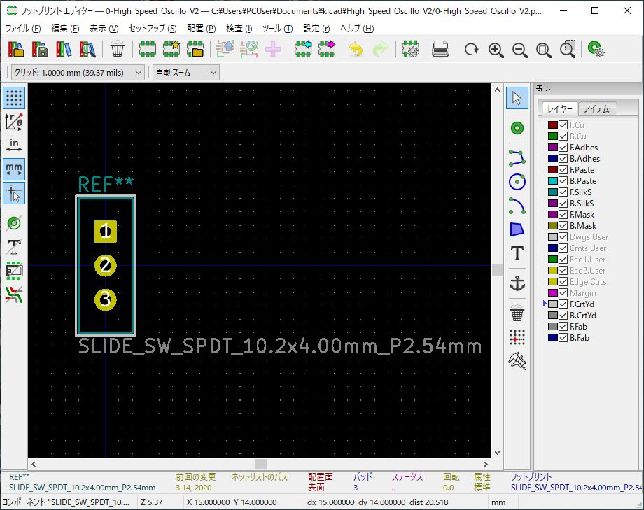

⑥ スライドSW:SS12SDP2 "日開" 1回路 2接点 マルツ販売(赤)

・Easy_FRA_V4ライブラり(自作)の中にあるので使える。

→ シンボル名:SLIDE_SW_SPDT(1回路2接点)

フットプリント名:SLIDE_SW_SPDT_10.2x4.00mm_P2.54mm

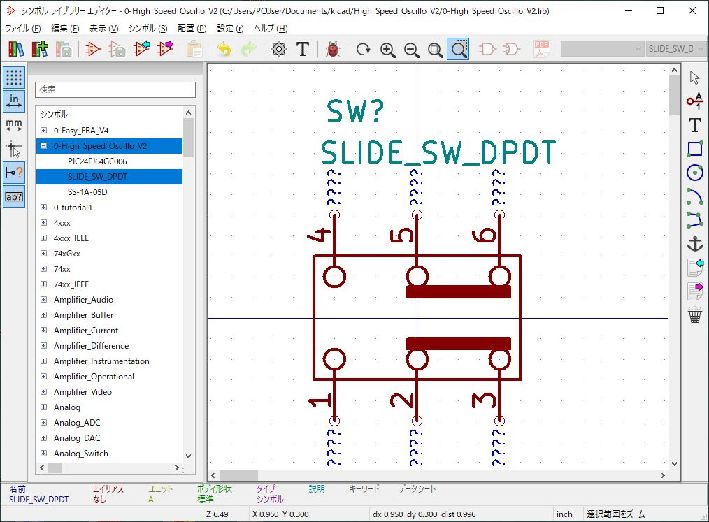

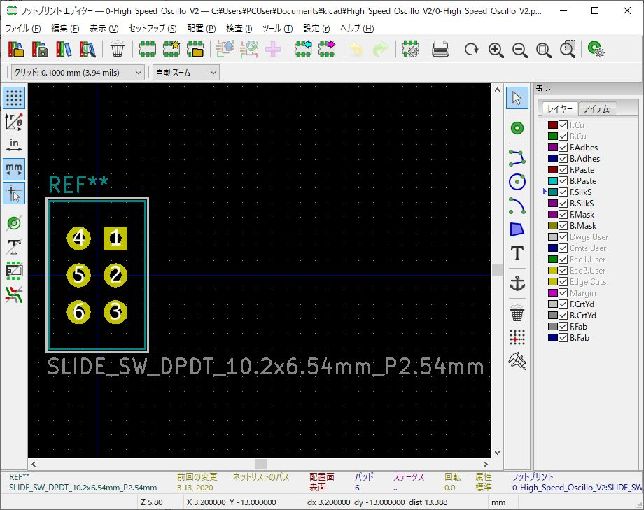

⑦ スライドSW:SS22SDP2 "日開" 2回路 2接点 マルツ販売(赤)

・無いので新規作成

→ シンボル名:SLIDE_SW_DPDT(2回路2接点・ちなみに、接点の'T'はN.OとN.Cを持つトランスファ接点を意味する。)

フットプリント名:SLIDE_SW_DPDT_10.2x6.54mm_P2.54mm

(実際のプットプリント上の寸法は、グリッドの設定の関係で、10.2x6.6mmにした。)

⑧ フィルムコンデンサ:1u63V PCMT36771105(367シリーズ・CODE=7) マルツ販売

・シンボル既成有り。

フットプリントのみ新規作成(あるいは既成自作ので合うのがあるか?)

→ 標準既成に有り:Capacitor_THT- C_Rect_L7.5mm_W6.5mm_P5.00mm 追記:200315

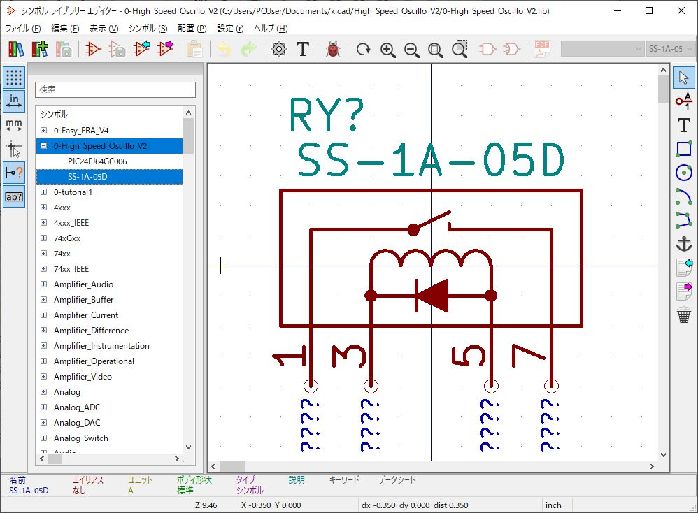

➈ リードリレー:1回路 メーク接点:SS-1A-05D

・新規作成

既成だと、

ライブラリ名:Relay

シンボル名:DIPxx-1Axx-12xD(ダイオード付)

が近いが、ピン配列等気に入らないので新規作成。

⑩ インダクタ:AL0510-220K(22uH 1.8A) 縦実装

・シンボルは既成にあり。

フットプリントは、Easy_FRA_V4の時、使った330uHのものをコピーして使える。

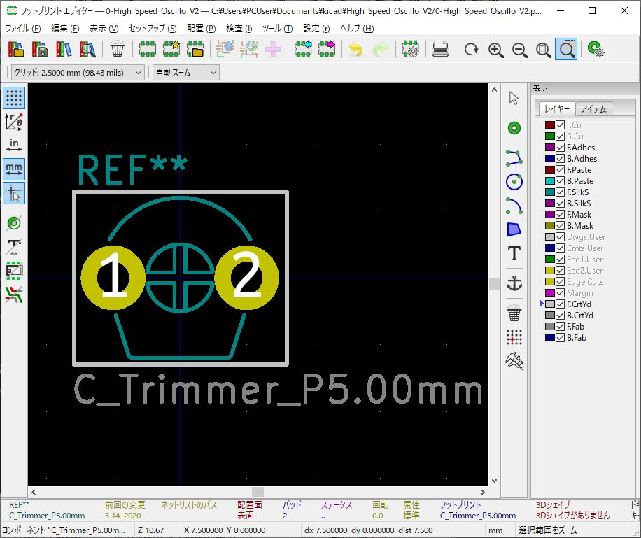

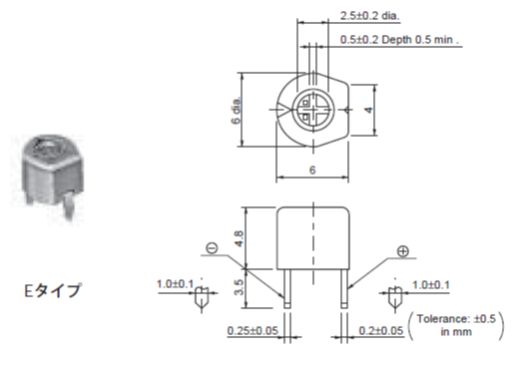

⑪ セラミック・トリマ:20p TZ03R200E169B00 "村田製作所"

・シンボルは既成にあり。

・フットプリントは無いので新規作成

⑫ ダイオード:1N4148

・シンボルは既成にあり。

・既成のフットプリント名:D_DO-35_SOD27_P7.62mm_Horizontalが使える。

⑬ プログラマブルクリスタルオシレータIC:SG8002DC-8MHz-PCB "EPSON(秋月の型番)"

・シンボル既成にあり。

・フットプリントはPackage_DIP-DIP-8_W7.62mm_Socketが使える。

⑭ Nch FET:2N7000 秋月販売 TO-92

・シンボル既成にあり。

・フットプリントは既成:Package_TO_SOT_THT-TO-92が使える。

■ 2020.3.7

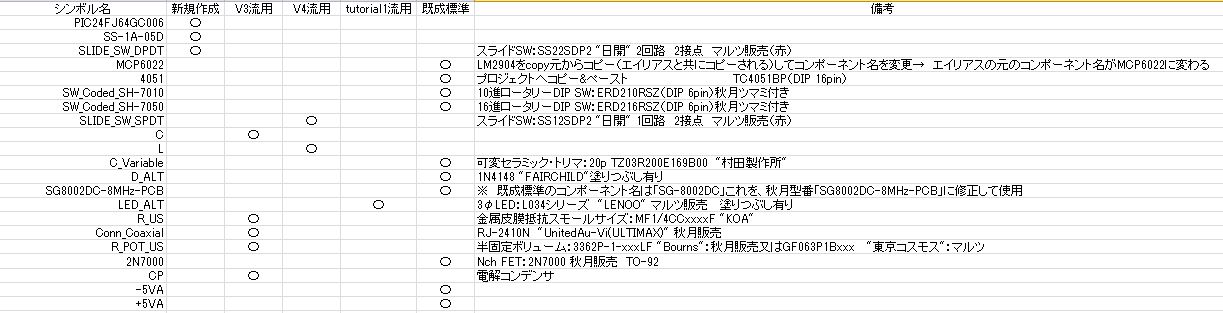

・新規もの以外のパーツについては、Easy_FRA_V4プロジェクトの物を利用するので、

High_Speed_Oscillo_V2プロジェクトに組み込む。

→ Easy_FRA_V3プロジェクトの物も利用するので組込んだ。200311 追記

・今日は、PIC24FJ64GC006のシンボル作成作業から行うことにした。

これと、SS-1A-05Dまでシンボル作成終了

■ 2020.3.8

・スライドSW:SS22SDP2のシンボル作成終了。

シンボル名:SLIDE_SW_DPDTで保存した。

・これで新規のシンボル作成は済んだ。

■ 2020.3.9

・新規もの以外のパーツについては、Easy_FRA_V4プロジェクトのものを利用するので、

既に、High_Speed_Oscillo_V2プロジェクトに組み込んだ、0-Easy_FRA_V4.libと0-Easy_FRA_V4.prettyフォルダ内

のパーツを使えばよい。

・新規物と、流用・修正して使う物の区別を明確にするために、Excelで登録パーツ一覧表を作成した。

■ 2020.3.13

・新規フットプリント作成

以下の3点

↑ ↑ ↑

※ このシルク、外形ラインの方向が間違っていました。

5月1日の記事を参照してください。

■ 2020.3.17

・回路図作成

今回は、2枚にしないと収まり切れそうにないが・・・

KiCadは複数枚の回路図を書くことが可能(無料)

複数枚の回路図作成の方法をマニュアル+WEB検索等で

ざっと調べてみたが、何となくは理解出来たが面倒くさそうなのと、ページ間の飛び先の指示の仕方が特殊。

1枚でもギリギリ書けそうな感触もあるので、まずはシンボルを置いて試してみる。

駄目そうだったら、2枚書きにする予定。

→ ざっと置いてみたが、何とかギリギリ入りそうなので書き出してみる。

■ 2020.3.20

・回路図作成 アノテーションまで終了

・ここで、転記ミスが無いかチェック→ ポテンショの、CW位置逆等ミス有り修正した。

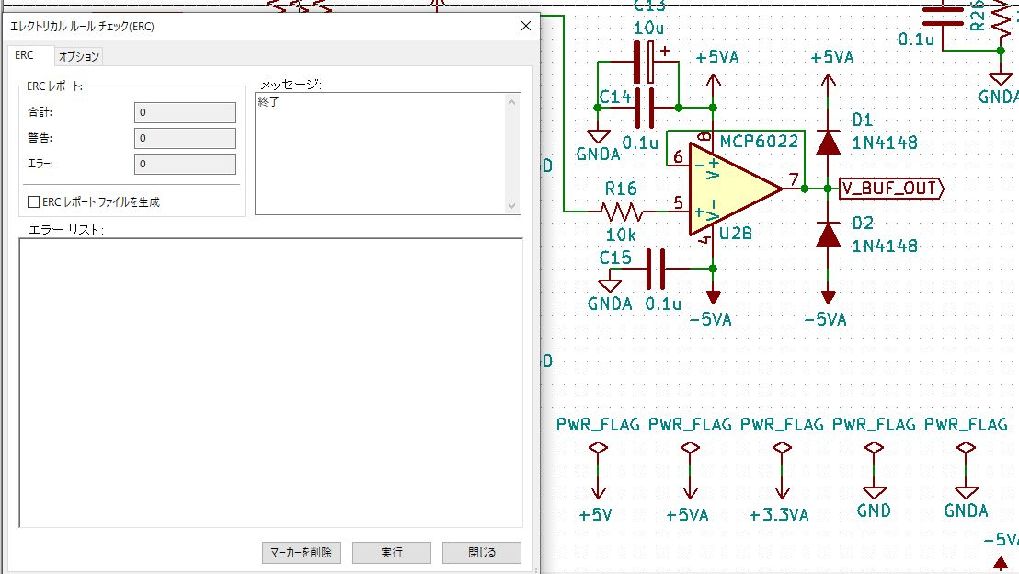

・ERCチェック

→ エラー(5) ピン間の衝突問題(3端子REGの電源出力ピンと、3.3Vフラグ(電源出力ピンに設定されている)

だが、これはネットには無関係で問題ないので、3.3Vフラグは削除した。

これで、ERCエラー0になる。

※ 追記:N.Isii記

そもそも、POWER FLAG(このシンボルのピンの電気的特性は電源出力ピンになっている。)

は、ERCのために、パッシブ・ピン(コネクタピンからの外部電源供給とか、抵抗・コイルを介しての電源供給)

から供給されているシンボル(↑シンボル)を、電源供給シンボルと認識させるだけのものと考えられる。

なので、3端子レギュレータ等の電源出ピンに接続されている↑シンボルに対しては、POWER FLAGと

接続する必要はないと考える。

この辺、明確に説明されているサイトは見当たらなかったので自分で考察してみた。

・フットプリントとシンボルの割付け(「CvPcbの実行」)

■ 2020.3.20

・続フットプリントとシンボルの割付け

何とか割付けた。

こちらを参照のこと→ フットプリント割付け結果リスト1/2_200322

フットプリント割付け結果リスト2/2_200325

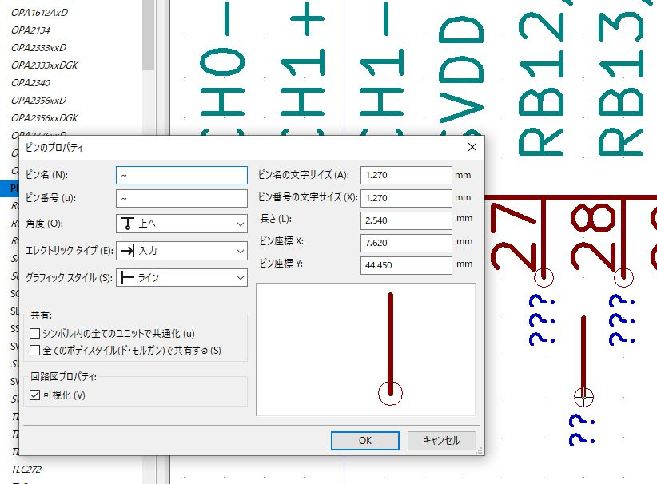

<作業途中で気付いたことメモ>

・時々左ペイン(ライブラリ名が列挙されている)を選択しても、右ペインにフットプリント・リストが表示

されない事があった。

その時は、一度、[OK]をクリックして「CvPcbの実行」を終了して再度、「CvPcbの実行」を実行

してライブラリの再読み込みをすると解消される。

・上記の現象が、最後に2つ残ったパーツに起きたが、上記の再読み込みをやっても何故か解消できなかった。

その2つは、下記の通リ、回路図上の当該シンボルのプロパティを開いてフットプリント項目に

直接入力して対処した。今のところエラーも出ず割付けられているようである。

① PIC24FJ64GC006(64TQFP 0.5mmピッチ)

→ 0-High_Speed_Oscillo_V2:TQFP-64_10x10mm_P0.5mm ←

何故かこのパーツは「CvPCB」で割付けが出来なかったのでこのテキストを回路図上の当該シンボルのプロパティダイアログ

の中の、フットプリントのフィールドに直接入力して割付けた。 200321

② プログラマブルクリスタルオシレータIC:SG8002DC-8MHz-PCB "EPSON(秋月の型番)"

※ 何故か「CvPCB」で最後に残ったこのパーツは「CvPCB」で割付けが出来なかったので

このテキストを回路図上の当該シンボルのプロパティダイアログの中の、フットプリントのフィールドに直接入力して割付けた。

→ 0-Easy_FRA_V3:DIP-8_W7.62mm_Socket 200321

・BOM LIST(部品表)作成

以前使用したweb上(https://www.usagi1975.com/06ju172022/)で、

KiCadのBOMを入力すると、見易いEXCELファイルの部品表に変換してくれるサイトに繋がらなくなったので新たな方法を調べてみた。

<作成方法を調べてみた:Eeschemaにて>

① 「部品表を生成」をクリック

② 最初に開いた時には、プラグインは登録されてないので、[プラグインを追加]をクリック

③ C:\Program Files\KiCad\bin\のディレクトリが開くので、scriptingフォルダをクリック

④ そのフォルダ下の、pluginsフォルダをクリック

⑤ bom2csv(XLSスタイルシート)をダブルクリック

⑥ ダイアログの、[BOMプラグイン]から、bom2csvを選択してクリック

⑦ ダイアログの、コマンドライン項目に以下のコマンドが表示されている。

[xsltproc -o "%O" "C:\Program Files\KiCad\bin\scripting\plugins\bom2csv.xsl" "%I"]

↑- 出力ファイル名 ↑- 入力ファイル名

⑧ %Oを、High_Speed_Oscillo_V2_BOM.csv(任意の名前でよい)に、

%Iを、High_Speed_Oscillo_V2.xml(中間ネットリストであるプロジェクト名.xml)に変更する。

プロジェクト名.xmlが存在するパスを実際に使っているパス:C:\Users\PCUser\Documents\kicad\High_Speed_Oscillo_V2

に変更する。

また出力側のファイル名もディレクトリ付で指定する。

最初ディレクトリ無しではエラーが出たのでそうしてみた。

つまり以下のようにコマンド入力(ダイアログのコマンドライン欄に直接入力した。下記をコピー&ペーストすると何故か

High_Speed_Oscillo_V2_BOM.csv"“C:¥Program Files¥KiCad¥bin¥scripting¥pluginsの、" "のスペースが無くなってしまったので)

すればよいのかな・・・

xsltproc -o "C:\Users\PCUser\Documents\kicad\High_Speed_Oscillo_V2\High_Speed_Oscillo_V2_BOM.csv"“C:¥Program Files¥KiCad¥bin¥scripting¥plugins¥bom2csv.xsl"

"

C:\Users\PCUser\Documents\kicad\High_Speed_Oscillo_V2¥High_Speed_Oscillo_V2.xml"

↑

➈ [生成]をクリック

⑩ 無事に部品表(BOM)が生成されると「成功」が表示される。

↑------これでやってみたがエラーが出る。

コマンドエラー。リターンコード 4

エラーメッセージ:

warning: failed to load external entity "“C:/Program"

cannot parse “C:\Program

<Google翻訳を基に訳した>

警告:外部の実体 "" C:/ Program "のロードに失敗しました

C:\ Programを解析できません

⑪ 部品表(BOM)がプロジェクトフォルダ内に生成されていることを確認する。

■ 2020.3.22

・昨日のエラー回避できず。

小坂氏のQ&Aサイトで、以下の成功例が書いてあった。

1.私のところで正しく動いたログを下に示しますので各項を比較照査してください。

実行条件

・Windows10(64bit)

・KiCad5.0.2 / デフォルト設定でインストール

・プロジェクトフォルダのパス:C:¥Users¥admin¥Documents¥tutorial1¥

・プロジェクトファイル名:tutorial1.pro

.

コマンドライン欄

xsltproc -o “%O.csv” “C:¥Program Files¥KiCad¥bin¥scripting¥plugins¥bom2grouped_csv.xsl” “%I”

プラグイン情報欄(実行結果のログ)

「コマンドラインで実行:

xsltproc -o “C:/Users/admin/Documents/tutorial1/tutorial1.csv” “C:¥Program Files¥KiCad¥bin¥scripting¥plugins¥bom2grouped_csv.xsl”

“

C:¥Users¥admin¥Documents¥tutorial1¥tutorial1.xml”

成功 」

・ちょっと追ってみたが基本的な誤りはないような感じで判らず仕舞い。

・今、Eeschemaの「BOM生成」を開くと、このフォルダにアクセスできない旨の警告ダイアログ

が出るが無視して一応は入れる状態にはなる。(しかし昨日までは出てなかった。)

Program Fileディレクトリ下の、KiCadフォルダのプロパティ-セキュリティtagを見るとアクセス許可の対象が何故か、

ALL APPLICATION PACKAGES になってる。(結果的にこれで正しかった)

User(PCUser-PC\Users)の項目を編集して

フルコントロールと、変更の許可のチェックboxにチェックマークを追加してに変えてみた。

→ これでも同じなので元に戻した。

読取りと実行

フォルダの内容の一覧表示

読取り

の3つのみにチェックマークに戻した。

bomは諦めた。

netリストの頭に、コンポーネント情報があるので、それを参照すればよい。

また、フットプリントの割付け時の画面のキャプチャを取れば、それが部品表代わりににるので

そうすることにした。

→ <net生成について調べてみた:Eeschema説明書.pdfより抜粋>

Eeschema はいくつかのネットリストのフォーマットをサポートしています。

• Pcbnew フォーマット(プリント配線)。

• OrCAD PCB2 フォーマット(プリント配線)。

• CADSTAR フォーマット(プリント配線)。

• 様々なシミュレータ用Spice フォーマット(Spice フォーマットは他のシミュレータにも使用されます)。

① 「NET」ツールを選択し、ネットリスト作成ダイアログを開きます。

② Pcbnew を選択

③ [生成]クリック

・未だ諦めきれないので、さらに別のサイトではどうやっているのか・・・

「やってみよう準備室」サイトより

次のコマンドでもよさそうなので試してみた。

これは、具体的なパスを明示しているのは、変換スクリプトファイルだけで

出力先は、%O.csv 入力先は、%Iとすればよいようば感じです。

xsltproc -o "%O.csv" "C:\Program Files\KiCad\lib\kicad\plugins\bom2csv.xsl" "%I"

→ これでも駄目だった。

そもそもBOMメニューを開く時からの問題のようだが、(MPLAB Xの時のようなファイルアクセス権の問題)

はっきりした原因解らず。保留にして先に進めることにした。

→ さらに調べてみた。

C:\Program Files\KiCad

KiCadフォルダを右クリックして、[セキュリティ]タブをクリック

[詳細設定]をクリック

名前: C:\Program Files\KiCad

所有者:Adminstrators (PCUser-PC\Adminstrators)

アクセス許可タブの、許可されているユーザー名は個人名(User(PCUser-PC\Users))

になっていてアクセス:読取りと実行になっているので問題ないと思われるのだが???

もしかしたらアクセス:フルコントロールにしないと駄目なのか??→ 以前やってたが駄目だった。

両者の違いは何なのか????

とりあえずあぶないので保留。

■ 2020.3.23

・BOMの件、解らず仕舞いだが、手探りしている内に、Excelで直接、XMLファイルを読込んでセーブ出来ることを発見した。

普通に「名前を付けて保存」で「High_Speed_Oscillo_V2.xml」を開くと、三択で開く方法を

聞いてくるので、一番上の、「XMLファイルとして開く」にチェックマークし[OK]をクリック

すると、青と白背景の項目が交互に並んだリストが表示される。

何やら、知りたい項目以外の余計なものもあったので、そこのセルは削除編集してセーブした。

これで、部品表といて十分使えそうである。

・NETリストの目視チェックを行う。→ 下記処理してチェックOK

① チェック途中で、SW10(READY)の向きが逆(電気的には問題ないが見た目よくない)なのに

気が付いた。→ ②のついでに直した。

② (net (code 9) (name "Net-(SW3-Pad1)") // TIME/DIV DIP SW

(node (ref U3) (pin ~))← 何故か、PIC-27pinに、ダブルで何も(信号名・ピン番)入力してないピンが重複している??

(node (ref U3) (pin 27))

(node (ref SW3) (pin 1)))

ERCではエラーはでなかったが。

修正済:シンボル修正して保存→ 念のため回路図も(何も修正しないで)上書き保存で、

再度net生成→ 当該netを確認したところ、直っていた。

あと念のため、フットプリント割り付けリストも開いて再チェックしOK確認後セーブした。

■ 2020.3.24

・基板レイアウト設計に入る前に、GNDとGNDAの分離・部品配置をラフ書きで検討中に

回路部品のテキスト入力が不足していることに気が付く。

→ SW8:HOLD

SW9:SLOPE

を追加修正した。

NETとフットプリント割付けには関係ないので、回路図のみ保存した。

・基板サイズは、10x10cmで進める。

GNDとGNDAの分離は、Easy_FRA_V4方式で上下に素直に分割(多少変わるかも・・)

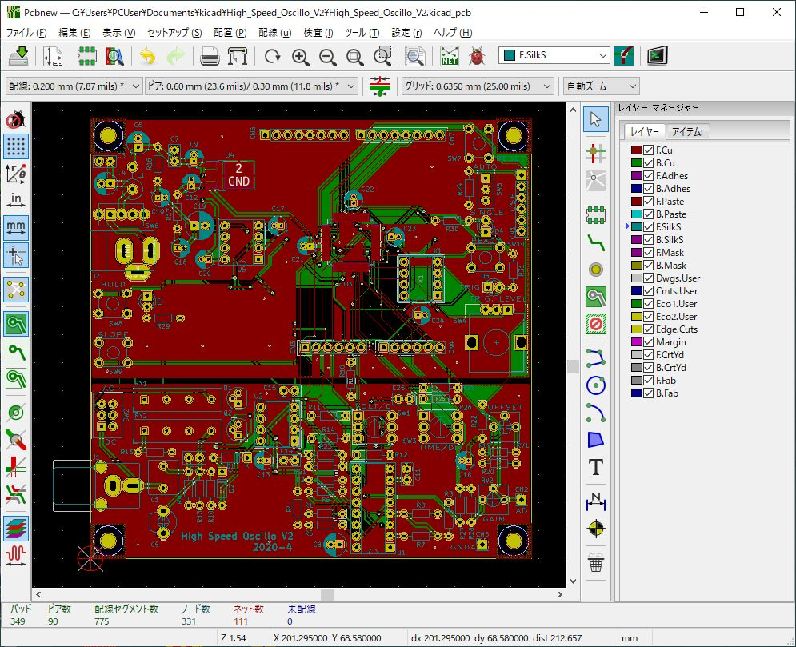

・基板レイアウト設計:PcbNew 開始

① 基板外形レイヤは、Edge.Cut

② 作業原点設定

PCBサイズ:100x100mm

作業原点:(99.06, 154.94)を、リセットして相対座標:dx,dy=(0,0)とする。

尚この位置は、図枠中央やや左下であればOK

※ 原点マークにカーソルを合わせ、スペースキーを押して、dx,dy=(0,0)に設定する作業はボードを開く度に必要。

③ デザイン・ルール設定は、FUSION PCB仕様に準拠

④ 外形線を引く:100x100mm

■ 2020.3.25

・取り付け穴 4個置く。

<PcbNew画面で気が付いた事>

・画面下の「座標表示バー」の右横には、左右ツールバーで選択したツールの機能が表示されているようだ。

例えば、右ツールバーの「ICアイコン」を選ぶと「フットプリントを追加」と表示される。

何故か、取付け穴配置作業中に、「重複した1アイテム」と表示されたのが気になって調べてみたのだが・・・

どうも左下に取付け穴を置いた時は出てないが、それをコピーした時点で出てるだけのようだ。(重複した1アイテム)

※ CTRL+Dによるコピーはしないで、毎回、「フットプリントを追加」ツールによる作業を繰返せばこのメッセージは出ないので

次回からはそうすることにした。

・禁止帯設定(部品面・半田面共)

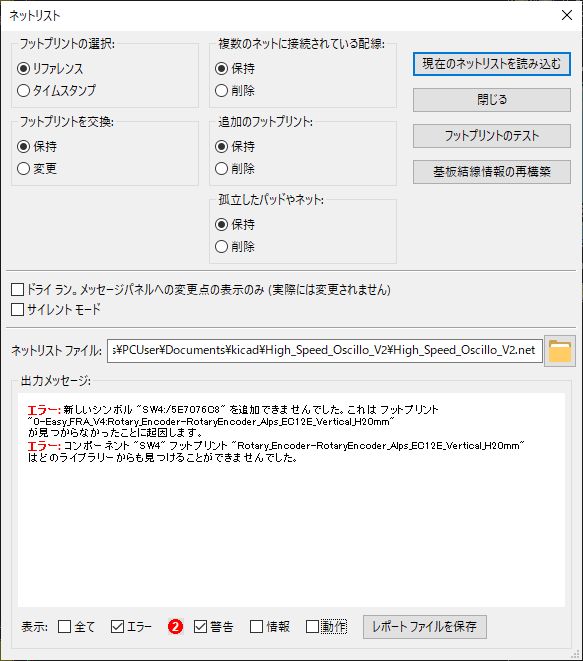

<ネットリスト読込作業の前に気が付いた!!>

・ロータリエンコーダ:SW4:EC12E2420801のフットプリントだが、

これが割付けの段階で、Potentiometer_Alps_RK09L_Single_Vertical

に割付けられていたことに気が付く。

これは、Easy_FRA_V4の時も同じミスをして、シンボルとフットプリントのピン番が合わないエラー

がネットリスト読込時に出ていた。

Alps_RK09L_Single_Verticalは、ボリュームのフットプリントで、形は同じだが、KI-CAD標準の、REシンボルとは

ピン番が異なる。

→ REのフットプリント(標準)のピン番:A-C-Bに対し、標準シンボルのピン番:1,2,3。

※ これの対処方法

① フットプリントを標準の→ Rotary_Encoder-RotaryEncoder_Alps_EC12E_Vertical_H20mmに割付け直す。

② この修正は何故か、CvPCBではできなかった経緯がある。

(V4にあるはずの、RotaryEncoder_Alps_EC12E_Vertical_H20mmが見当たらない?)

そこで、回路図上のSW4:REシンボルを右クリック→ プロパティ編集で、フットプリント・フィルド定数の変更を行う。

→ 0-Easy_FRA_V4:Rotary_Encoder-RotaryEncoder_Alps_EC12E_Vertical_H20mm にする。

③ ここでCvPCBに戻ると、RotaryEncoder_Alps_EC12E_Vertical_H20mmに置き換わっているので保存。

④ この状態で、ネットリスト再生成

⑤ BOMも再生成

尚、④⑤の後、チェックはしないで先に進む。パターン引き段階で判るので。

・NET LIST読込みで次の、2つのエラー発生

下記は、NET LIST上でのその部分抜粋を示す。

(comp (ref SW4)

(value EC12E2420801)

(footprint 0-Easy_FRA_V4:Rotary_Encoder-RotaryEncoder_Alps_EC12E_Vertical_H20mm)

(libsource (lib 0-Easy_FRA_V4) (part Rotary_Encoder) (description ""))

(sheetpath (names /) (tstamps /))

(tstamp 5E7076C8))

5E7076C8とはテンポラリ番号で、型番:EC12E2420801のロータリエンコーダを差す。

※ NET LIST読込みでエラーが出ているが、コンポーネントの塊は表示されている。

しかし、当然ながら、SW4:Rotary_Encoder-RotaryEncoder_Alps_EC12Eは表示されてない。

※ 原因が解った。

回路図上で、当該部品のプロパティのフィルド定数の変更をする時に、

ライブラリ名(カテゴリ):Rotary_Encoder-も一緒に入力してしまったのが原因。

RotaryEncoder_Alps_EC12E_Vertical_H20mm

だけで良かった。

これで、SW4:Rotary_Encoder-RotaryEncoder_Alps_EC12Eも表示された。

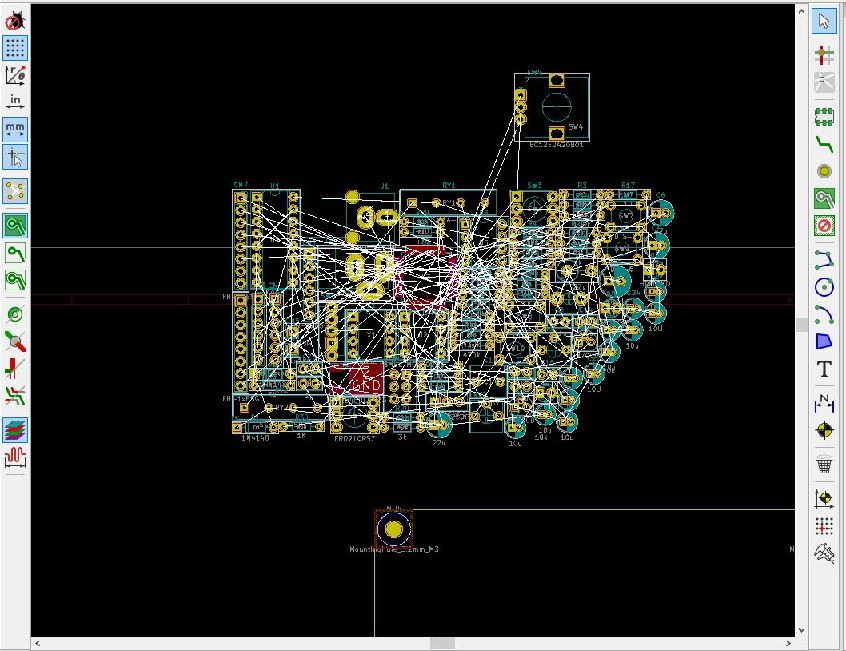

■ 2020.3.26

・基板レイアウト設計:PcbNew 続き

部品配置。まずは、FIX部品の、QVGAコネクタ:CN3,4,6,7

Easy_FRA_V4同様、コネクタ全体を選択し、コネクタの1pin位置を、編集(E)で、プロパティダイアログを開き、

X, Yの絶対座標にdx,dyの相対座標を、X, Yの絶対座標に変換して手入力することにした。(位置は_4と同じにしておく。)

変換式は、以下(各定数は、作業原点の、相対座標)

X= dx + 99.06

Y= 154.94 - dy

この式によって計算すると、入力する絶対座標は、以下になる。

CN3:(147.74 , 107.07)

CN4:(165.52 , 107.07)

CN6:(138.66 , 58.81)

CN7:(160.44 , 58.81)

・他部品の暫定配置を行う。

■ 2020.3.27

・他部品の暫定配置終了した。

・QVGA含め、部品位置の詳細確認を行う。

原寸大でボード図をプリントアウトして、現物を置きながら確認。

→ QVGAフットプリントOKを確認。

暫定位置パーツも概ね良さそう。

ロータリーDIP SW近傍の、抵抗は若干上に移動した方が良いかな。

あと、右サイドの、SLIDE SW・タクトSW類も若干右に寄せた方が、操作性が良くなるかな。

■ 2020.3.28

・クリアランス確保のため以下の作業を行う。

① DIP SW1を上に1グリッド移動

② DIP SW1についてくるR11,14も上に1グリッド移動

③ DIP SW4を上に1グリッド移動

④ DIP SW1についてくるR25,26を上に2グリッド移動

⑤ RV1を上に1グリッド移動

・右サイドの、SLIDE SW・タクトSW類も若干右に寄せる。これはパターン引きながら様子見。

■ 2020.3.29

・配線する前に、部品定数の非表示 ,部品番号の移動をして整理しておく。この方が引きやすくなる。

「値」と「非表示テキスト」のチェックを外す。

・ベタ生成作業

GND領域にある、GNDAネットをGNDA領域に手配線してからベタ生成する。

※ ベタ生成作業の時、パターンとベタ間のクリアランスが無くなって表示される時があった。 200329 追記

その時は、ベタ領域のラインをクリックしてダイアログを出し、再度クリアランスが、0.35mmになっていることを確認して

OKをクリックすると、進捗バーが一瞬表示されて再セットされ正常なクリアランスに戻る。

この症状でなくても(例えば、GNDAネット同志なのにベタにした時そのネットが残る現象)同じ操作で直る。200331 追記

・P_ON_SW:SW6回転させた。

ONのレバー位置を、Easy_FRA_V4と同じにした。(横置き)

これはベタには影響しない。

・電源ラインを引き始めたが、途中で部品面の、GNDベタとパターン間のクリアランスが無いこと

に気が付いた。

→ 基板上部、部品面のベタ設定の時に、GNDAとしてしまっていた。

これにより、3端子レギュレータの2pinのgndフィンが、GNDとフローティングになって見えて

しまってた。(エアーワイヤになっていた)

・DC5V入力:J2→ LPF→ +5V・+5VAの供給元→ U6:3.3VReg→ +3.3V・+3.3VAの供給元 ブロックの配線終了

■ 2020.3.30

・電源ライン配線続行

① C21反転→ PIC-10pin側に、+ピンを合わせる。

② X1縦置きに修正。これのパスコン:C24も下中央に移動→ X1出力ピン⇔PIC-39pinを極力短くする為

③ +3.3Vネット配線暫定終了

④ +5Vネット配線暫定終了

⑤ +3.3VAネット配線暫定終了

⑥ +5VAネット配線暫定終了 (U2パスコンC14若干移動)

⑦ -5VAネット配線暫定終了(U5CAP:C17回転)

これで電源ライン全て終了(但し暫定)

いや未だあった。

GNDA領域にある、スライドSW2の、DC/AC識別信号接点側の、GND(デジタル)

これは、GND領域にある直近のタクトSW、SW9の、GNDに引くことにした。

もう一つあった。

配置の都合(操作しやすい並び)で、TIME/DIV DIP SW3のコモンが、GNDA領域に配置されているので

ここを、GNDA領域にある近傍の、R18(GND-GNDA接続点ショートR)のGNDネットと接続する必要がある。

この後、アナログブロックの配線を一部行った。

■ 2020.3.31

・アナログライン配線続行→ 一応だが暫定終了

・オートルータ

20分位かかったが、一応コンプリートになったようだが、PCBNewにインポートしようとしたら、sesファイルを開く

ためのダイアログが表示されたが、プロジェクト配下におのファイルは存在しなかった。

ここで[開く]をクリックしたら、以下のエラーダイアログが表示された。

「基板は破損しているかも知れません。保存しないで下さい。

問題点を修正してやり直してください 」

[OK]をクリックして抜けた。(保存はしてない。)

→ やにオートルータを実行していた時間が長かったのが気になる。(Easy_FRA_V4時も10分位かかったが)

→ もう一度トライしてみる。駆動中のpcの状況が重かったのかもしれないので・・・

それでもだめだったら、デジタル部の簡単に配線出来るところは、予め手配線をしといて

からオートルータをかけてみる。

※ 原因そうなのが解った。

Freeroltarのグリッド設定が、デフォルトの[um](たぶんマイクロミリ)になっていた。

24umになっていた。単位まで気が回らなかった。

24milに修正して再トライしてみる。

あと自動配線終了後,メニューバー「File」→「Export Specctra…」と進みます。

これをやってなかった。(これは致命的だった・・)

→ 25milに修正して再トライ

オートルータコンプリートになった。約20分かかった。

ここで気が付いた。

① デジタル領域のベタGNDに繋がってないネットが、2箇所ほど存在していた。

U3-9:gndピン・U3-41:gndピン

→ gndピンパッドから線を引き出してその先にランドを用意しないとベタに接続出来ないようだ。

② U3-56:VCAPピン- C22:10uプラスピン手配線忘れ

※ これら修正してから再度オートルータを掛けないと駄目→ 再度オートルータを掛けてみた。

25分位掛かったがやっとコンプリート

・マージして見てみたが、gndピンがベタから浮いている新たな個所と同じ個所が1箇所ずつ存在していた。

こう事は_Easy_FRA_V4の時にもあった。(QFP周辺)

パターンを移動して島の面積を増やしたり、ビア打ちして解決している。

・一度気入らない引き回しを整理しながら、再度ベタ表示して様子を見る予定

※ 現状のボードファイルのバックアップを取ってからセーブ

・ピン間1本のところは、アナログ部でも安全(クリアランス)を見て、0.2mm幅を使用。

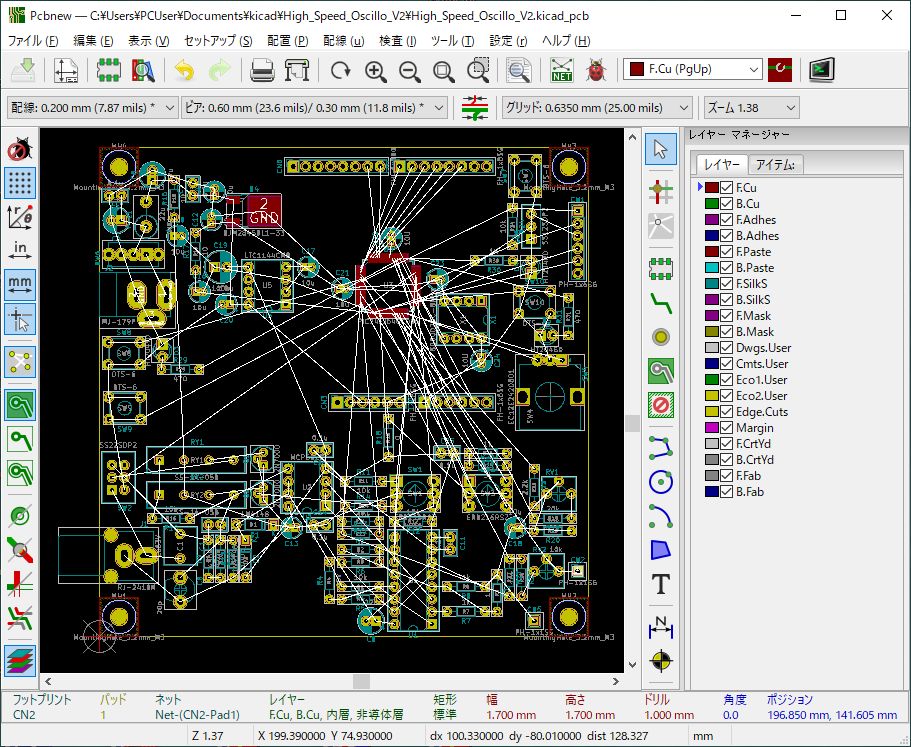

■ 2020.4.1

・オートルータ後、気に入らないライン手直し

5点ほど直す。

・ベタGND部にエアーワイヤが、4箇所(昨日まで判っているGNDネット2箇所+今回判ったGNDAネット1箇所+GNDネット1箇所)

残っているのを処理

→ 3箇所のビア打ちで良くなる。

これで未配線:0

・ベタの隙間を極力無くすために、SW5からのパターンを移動

→ わずかしか広がらなかったが、この方のが素直な流れなので、このままにしておく。

・ビア打ち実施

使用ビア直径=0.6mm(23.6mil)/ビアドリル=0.3mm(15.75mil)

→

この追加のビア打ちで、ベタの隙間(島を出来るだけ多く)だいぶ無くなる。

・配線とビアのクリーンアップ(必要のないもの・違反するものの削除)

必ずベタ表示の状態で行う。さもないと、追加したビアとネットが削除されてしまう。

→

配線とビアのクリーンアップ実施したが、特にメッセージ無し・ボード上の変化も見当たらなかった。

・DRC→OK(1発OK)

・TEXTの挿入とシルク最終整理

TRIG MODE SWを置く時に、レバー上でAUTO位置にしたかったが、逆に置いてしまったことに気が付く。

■ 2020.4.2

・TRIG MODE SWのレバー上でAUTO位置の件だが、この修正はネットには無関係。

ネットは正しく、部品の置く向きが180°反転しているだけなので、反転させ

再配線・再ベタ生成・再DRCすればOKなのでリスクはない。

→ 修正後DRCもエラー無しOK

※ これでようやく、KiCadでのボード設計は終了

・アーカイブの保存

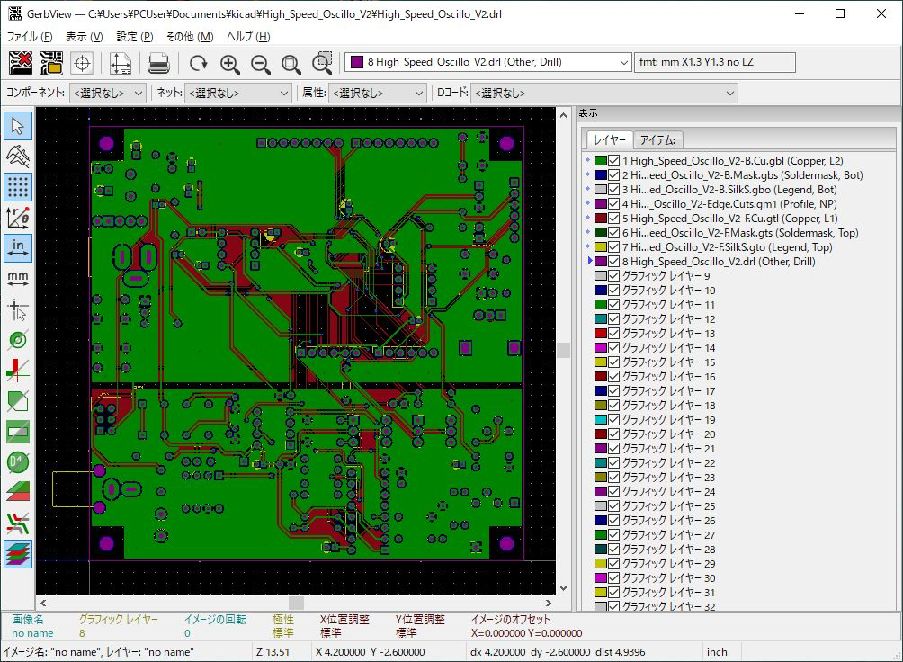

・ガーバー生成作業

※ ここまでやった後に気が付いた。

PICの裏(部品面)にベタが無い。

PICの裏(部品面)にビア打ちを追加することにした。

DRCもOK

以下に、KiCadでの最終ボード状態を示した。

・再アーカイブの保存

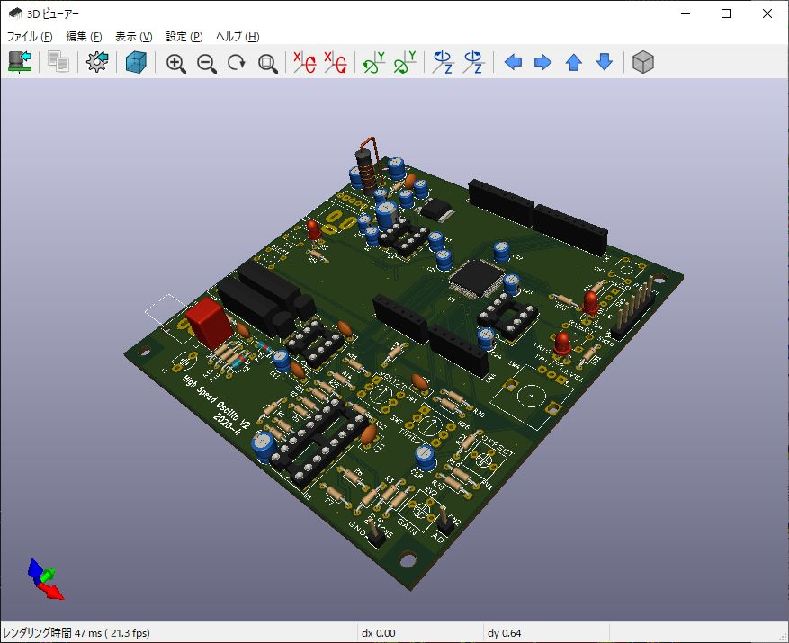

・3Dビューワ確認

・ガーバー確認作業

KiCadの、GervViewrにて確認

・FusionPCB発注作業

FusionPCBのファイル名に変更後、

何時ものgerbvにて確認しようと思ったが、アプリにレイヤファイルを読込まそうとすると、アプリが強制終了しまう。

Easy_FRA_V4のファイルでも同じだった。

どうも、_V4の時から、このアプリが使えなくなったようだ。

過去のドキュメントにもこのアプリのキャプチャ画像は見当たらなかった。

覚えが無いが、たぶん、WIN10の更新が原因していると思われる。

→ 追記:200402 20:50

gerbvファイル(gerbv project file)は、各プロジェクト・フォルダ内の、FusionPCB向けガーバデータ_xxxxxxフォルダに保存してある。

確認したら、Easy_FRA_V3は、gerbvファイルが保存されていたが、Easy_FRA_V4は保存されてなかった。

※ FusionPCBの、ガーバビューワでは問題無しなので、そろそろ発注に取り掛かる。

■ 2020.4.3

・FusionPCB発注作業→ 済

100x100 10枚の場合、入力はデフォルトのままで良い。

送料込み:2778円

・部品手配

調整・チェックのために自作ユニバーサル版高速オシロを使うので、ここからの部品取りは出来ない。

手配用の部品表を作成した。

■ 2020.4.4

・秋月分:3030円

マルツ分:2139円

振込手続済

・基板製造進捗:ご注文は確認済み、データ審査中

■ 2020.4.5

・基板製造進捗無し

どうも、4/4~4/6まで、清明節で、Seedは休業のようだ。

■ 2020.4.8

・基板製造進捗無し

工場は稼働しているようだが・・・遅れているのか?

P板到着待ち状態。

・Fusion PCB HPより:OCSの至急連絡により、4月9日から19日まで配送サービスが一時停止されることになります。

OCS:国際輸送、海外生活サポートの株式会社OCS

→ OCSとは、Fusion PCBが提携している運送会社の内の1つで、一番格安の運送会社のこと。

なので、DHLを選択している私には関係無し。

■ 2020.4.9

・底アクリル板製作済

・ソフトVUP変更+HEX準備済

■ 2020.4.10

・WEB上では進捗「審査中」で変わらずだが??

■ 2020.4.11

・WEB上では進捗詳細:「審査中」で変わらずだが??

大きな流れチャートでは「4/3:ご注文は確認済み、生産プロセスに入りました。」になっている・・・

Easy_FRA_V4の時は、このプロセスから、出荷まで約6日掛かっている。

4/6まで中国は「清明節」で、Seeedは休業だったので、4/7から作業開始として、4/14位の出荷になるのかなあ・・・

→ 16:00確認したら進捗有:10%→ 20%(やっと本当に生産中になった。)

アイテム詳細:

審査完了:4/11 11:08:22

生産中 :4/11 11:08:22

これで行くと、4/18位の出荷になるのかなあ・・・

■ 2020.4.18

・やっと進捗ステータスが「製造済:100%」になった。出荷は未だだが・・・

■ 2020.4.21

・進捗変化無し。

seeed HPより「DHLの連絡により、4月20~ 21日は配送停止で、22日からサービスを再開することになりました。」

さらに遅れそうである。

■ 2020.4.23

・ようやく進捗ステータスが、「出荷済」になった。

「2020-04-23

11:30:52 ご注文は梱包され、すぐに出荷されます。」

「2020-04-23

11:30:56 ご注文は出荷されました。すぐに配送状況を更新いたします。」

■ 2020.4.28

・何故か進捗ステータスが、「処理保留中」:TOKYO-JAPAN:11:04 で止まっている。

( 「DHL施設へ到着 TOKYO JAPAN:TOKYO-JAPAN:06:27)

→ DHLへの問合せtel番号:0120-39-2580 平日 8:00~20:00 月~金

8:30 繋がらない

しょうがないのでメールにて問い合わせた。

「進捗ステータスが、「処理保留中」:TOKYO-JAPAN:11:04 で止まっているのは何故ですか?

荷物は既に都内に着いていて移動中の段階でしょうか?」

・荷物の配達予定は、4/30(木) 当日中になっているが・・・

・心配は無用だった。

予定より早く今日中に届くようである。 進捗が「配達中」10:23 になった。

・夕刻:17時位にDHLの配達員が届けに来たようだが移動中で不在だったため携帯にメール入った。

「再配達依頼してください」とのこと。

帰宅して不在票を見ると「再配達、住所変更はこちらから」という欄があり、QRコードが貼りついていた。

この読取り方法が思い出せなかったので、直にDHLホームページより、PCにて再配達依頼を掛けた。

最短で、4月30日ということだったので「4月30日 9:00~13:00」で依頼を出しておいた。

今迄と不在票の様式が変わっているようだ。

今迄は、不在になると即「佐川急便」に業務が移り、追跡もDHL

HPでは出来なくなるのだが・・・

今回は上記のように違っていた。

しかし当日中に何も連絡しなければ自動的に「佐川急便」に移行になるようだが・・・

■ 2020.4.29

・ちょっと気になってQRコードの読み取りを再度行ってみた。

携帯のカメラアプリのメニューの中に「バーコード」というのがあり、さらにサブメニューの中に「URLの内容を表示」というのがあったので、

URLを確認してみた。

→「https://ondemand.dhl.com/jp」だった。

早速PCでどんなページか確認してみた。

昨日は、あせっていて適当に操作して、辿り着いたページが、どんなだったかうる覚えだったが・・

昨日見たページと同じだった。

このページの「ログインせずに配達を指定」から変更した。

昨日の配達日変更依頼でよかったようだ。

まあ元々が、4月30日

当日中の予定だったので良しとしよう。

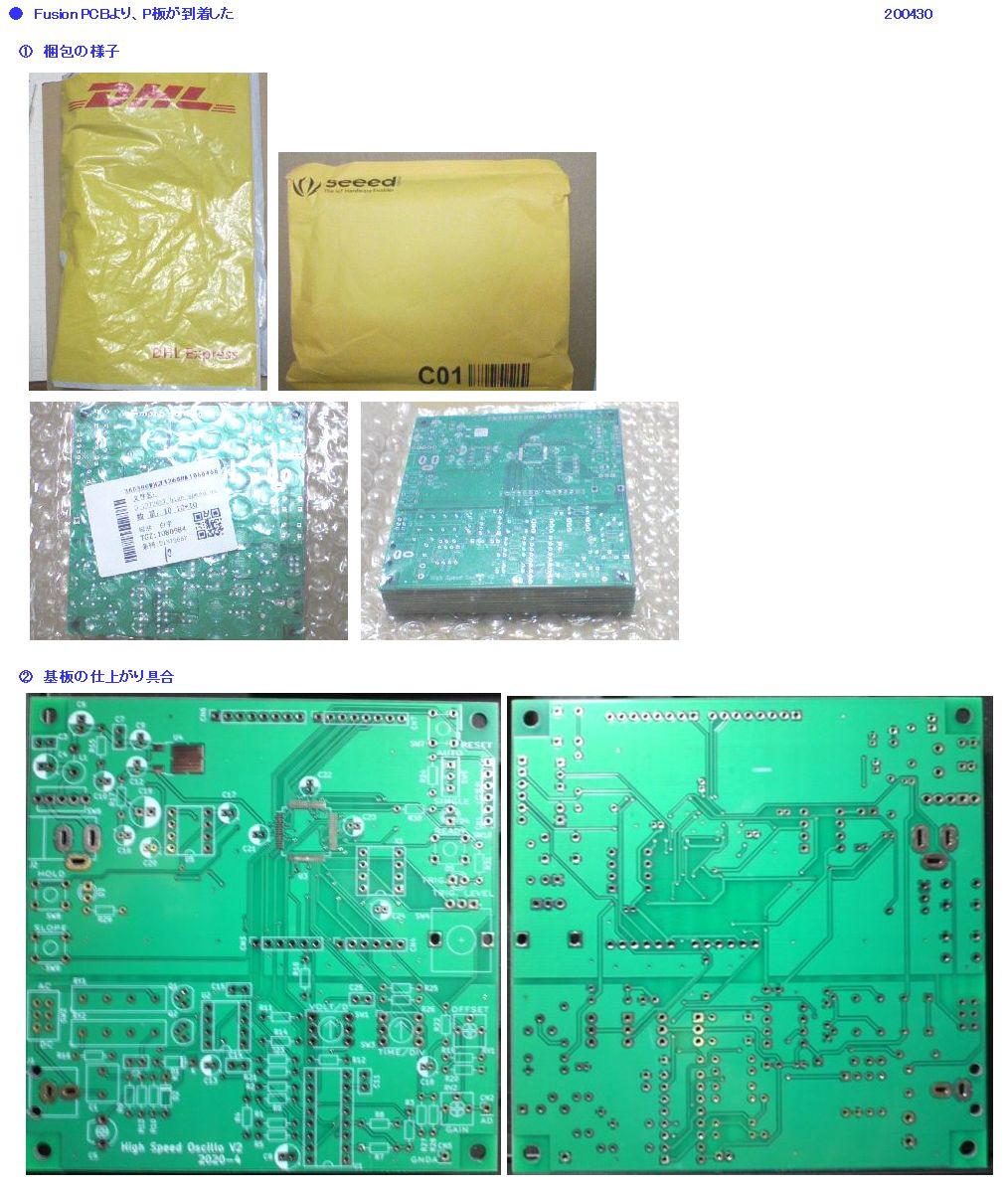

■ 2020.4.30

・11:30 ようやくDHLの配達員により、P板が届いた。

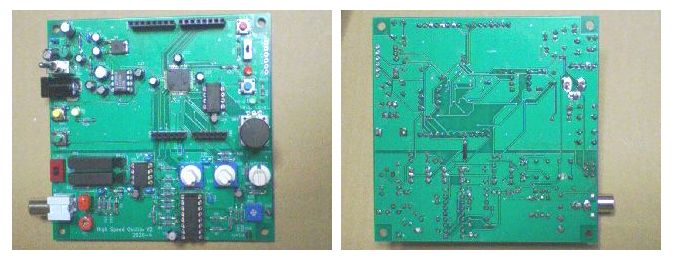

・見た目、問題無さそうです。シルクも割と綺麗でした。

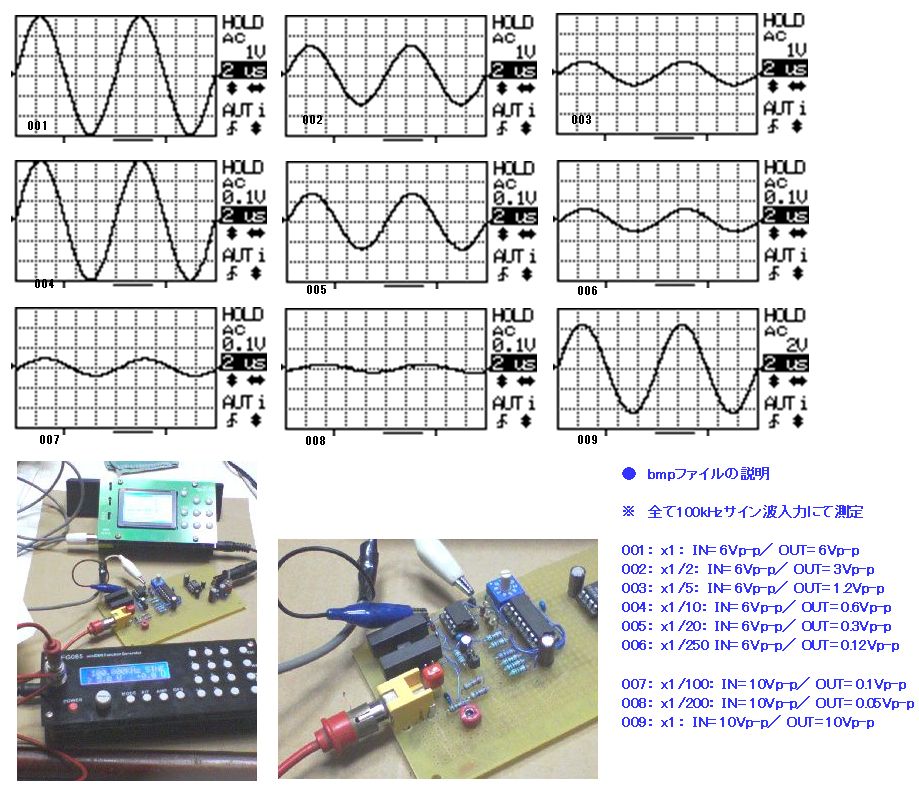

■ 2020.5.2

・部品実装開始。

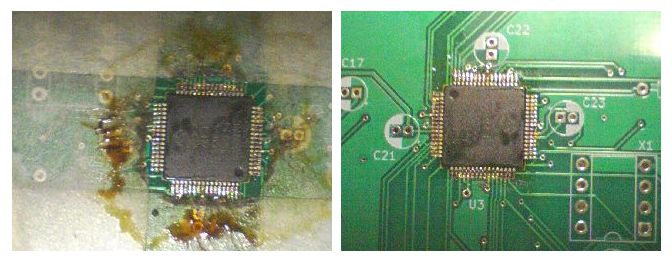

まずは難関の、TQFP-64のハンダ付けから。

たまにしか多ピン・峡間ピッチ(0.5mm)のデバイスのハンダ付けは、しないので毎回ながら不安感があるが、

何とか無事に作業が終了した。(無事かどうかは火を入れてみないと判らないが・・目視では、大丈夫そう。)

・実装に際して、設計時、使おうと思っていた物(型番)と異なる型番の物を実装した部品があります。

それは、日開の赤い小型スライドSW:SS12SDP(TRIG

MODEの切替えSW)なのだが、

SS12SDP2のフットプリントを割付ける時、Easy_FRA_V4で使用したフットプリント:SS12D01G4(秋月)

に割付けてしまった。

日開の赤い小型スライドSW:SS12SDPは縦方向の寸法が他の物と比べて多少長いので、実装すると、

機能シルク文字の、"AUTO"と、"SINGLE"が殆ど隠れてしまう。

手持ちに、縦方向の寸法が短か目の、aitendoの"SS12D00G5"があったのでこれを実装することにした。

これは、レバーも長目なので、操作性も良くなってGOOD!!

(これと同じような寸法の、秋月で購入した、"SS12D1G4"もあったが、レバー多少短か目なので却下した。)

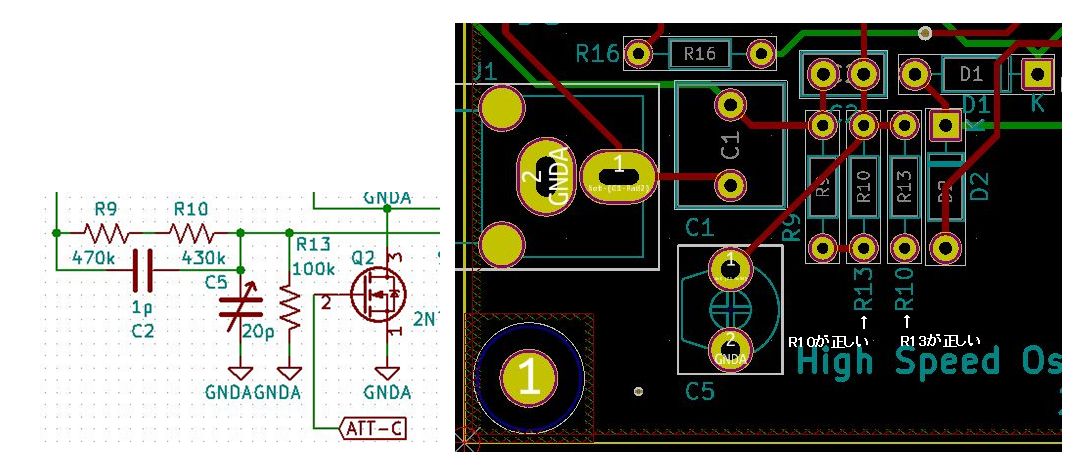

・あとミスとしては、C5のトリマコンデンサのシルクミスがあった。

ランドに対してシルクの方向が間違っていた。以下の写真を見てください。

実装には問題無いのでそのまま実装した。

実装すれば、殆どシルクは隠れるので見た目には目立たない。

・部品実装が完了した。

・動作チェック開始。

(1) ショートチェック(PIC以外の、IC+LCD未実装)

+5V-G: OK

+5VA-G: OK

-5VA-G: OK

+3.3V-G: OK

+3.3VA-G: OK

(2) 電源チェック-1(PIC他、U5:LTC1144CN8/

X1:SG802DC-8MHzのみ実装)

+5V : 5.21V

+5VA : 5.10V

-5VA : -5.20V

+3.3V : 3.28V

+3.3VA: 3.27V

(3) PICkit3にてデバイス認識~ HEX書込み→ OK

(4) 電源チェック-2(LCD以外の全てのIC実装)

+5V : 5.20V

+5VA : 5.07V

-5VA : -5.01V

+3.3V : 3.28V

+3.3VA: 3.27V

(5) LCDを実装して動作チェック開始

・最初は、大雑把にチェック。

ショートプラグで、オシロ入力を、0Vにして動作確認したが、まずは駄目。

レンジ表示とトリガレベル可変表示は大方OKだが、OFFSET

VRを回しても、ADC入力(テストピン:CN2)が、0Vで変化しない。

なので、輝線が、最下位ラインに張付いて動かない。

■ 2020.5.3

・昨日の問題追及。

① ADC入力(PIC内部終段OPアンプ出力)とGNDAはショートしてない事を確認。

② OFFSET VRでの可変範囲を確認してみた。

1.07V~ 1.5V~ 2.13Vで、OKだった。

③ PIC内部OP1-+ピンのバイアス電圧が、0.75V(これはVCC=3Vの場合の理論値)か確認してみた。

実測してみたら何と、2.45V?

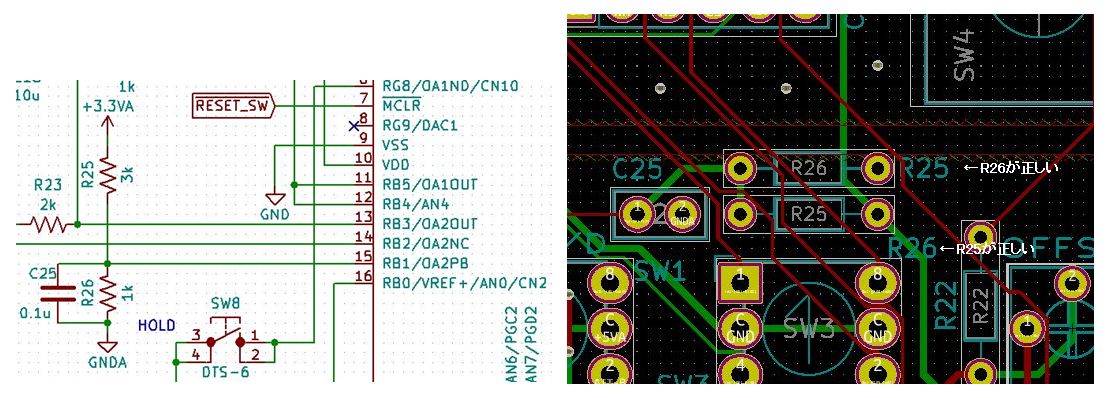

分圧抵抗の、R25=3k, R26=1kが回路図では正しいのだが、ボード上でシルク整理の時、R番シルクを逆に置いて

しまLたようでテレコになっている。

→ ここを修正したら、0.8V(VCC=3.3Vなので少し高くて正解)にはなったが、未だ駄目。

今度は、最上位ラインに張付いた。

④ この時の、ADC入力は前とは逆で、3.22Vに張付いている。

⑤ 調査中に何故か自然に良くなった。

OFFSET VRで正常に輝線がシフトする。

どうもPICのAVCCピンのハンダ付けがちょい見た目は付いている様に見えるのだが、ルーペで拡大してよく見ると

ハンダが薄くて接触が悪いように見える。

またこのピンをカッターの先などでこじると少し動いたような感触があった。

接触不良の可能性が高いので、ハンダ盛り修正を行った。

・良くなったので先に進む。

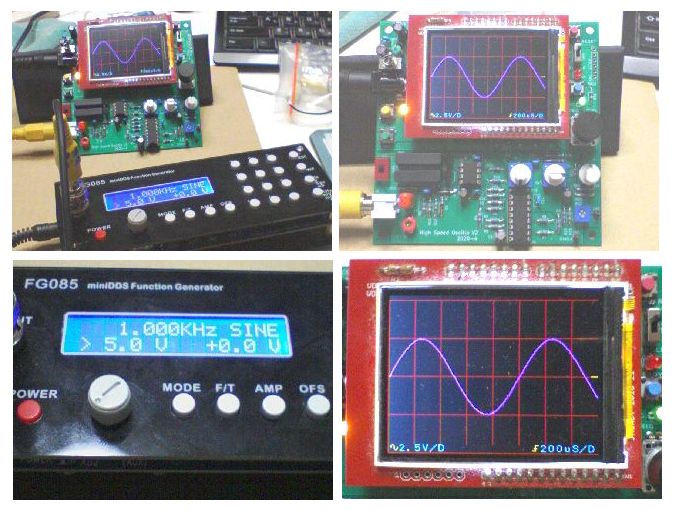

今度は、オシロ入力に、5Vp-p 1kHzサイン波を入力してみる。

オシロのレンジは、2.5V/D・200uS/D

何故かサチって表示される。時間軸は正しい。(写真は撮らなかった)

→ これもボード上でのシルクが逆になっていて定数がテレコのなっていたのが原因だった

入力1/10ATTの、R10:430k・R13:100kのところ、シルクが逆で、R10:100k・R13:430kになっていた。

そのため殆ど減衰無しになぅていた。

・これを修正し正常動作を確認した。

■ 2020.5.4

・矩形波入力による、DCモードの確認を行った。

トリマコンデンサ:TCを回して、オーバーシュート・アンダーシュートが出来るだけ無くなる点に合わせるのだが、回しても

殆ど変化しない。(最終的には、サイン波の帯域が出来るだけ取れる様に調整するつもり。)

これは、回路図ミスが原因だった。

ACモード時はOKなのだが、AC/DC切替え用スライドSW部の回路図に誤りがありました。

このページ末尾にアップした回路図に朱書きで書かれていますので参照してください。

この誤りにより、DCモード時に限り。前置1/10ATT+TCによる高域補正回路がスルーされ、レンジに関係なく常に、

ATT=1/1になって、TCも効かない状態になっていた。

早速リワク修正(カット・スタラップ各1箇所)を行った。

・これでもTCによる矩形波の波形変化の度合いは少なかった。

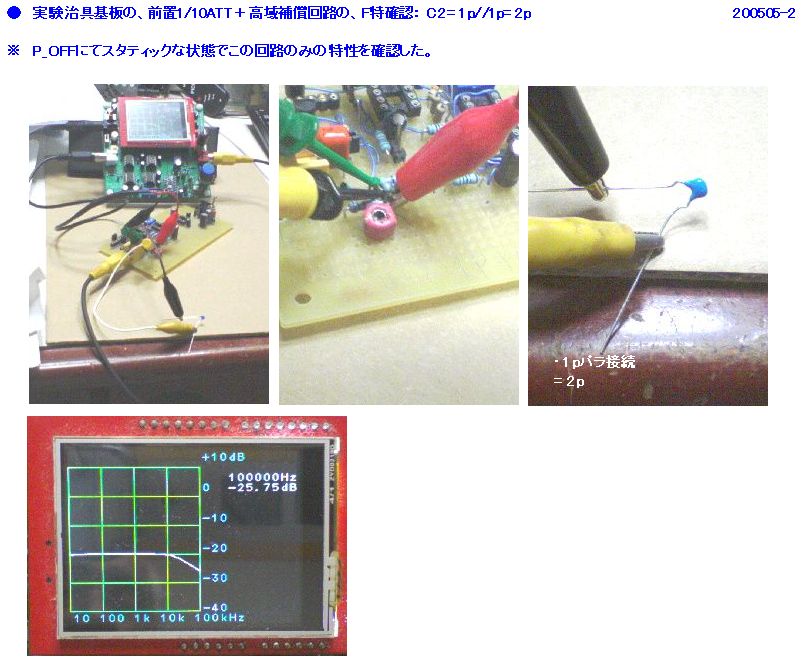

そこで現状の、前置1/10ATT+TCによる高域補正回路部の、F特を取ってみた。

高域特性が良くない。

30kHz近辺から落ち始めている。

矩形波の立上りにもろ影響していると考える。

■ 2020.5.5

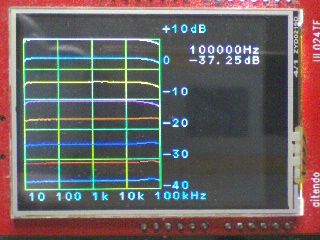

・これは、AC(サイン波)入力でも、前置1/10ATT+TC部が有効になる、1V/D(ATT-26dB)以上のレンジに効いてくるはず。

そこで、最近マルチ描画に対応したソフトにVUPした、Easy_FEA_V4a(更新したソフトは、ここに有ります。)で確認してみた。

案の定であった。

オレンジ色のライン以降が、1V/D以下のレンジです。

・前から気になっている事がある。

それは、この実験の参考にしている、JA1WBYさんの記事である。

JA1WBYさんは、リレーでなく、フォトMOSリレーICを使用している。

そして高域補償C=100pでも、極端に高域が上昇しピークが出来ている。(前置ATT1/10のF特)

この原因は、おそらく、接点として使っているMOS FETの出力容量の影響と考えられる。

この出力容量は、もう一つの補償コンデンサ:C2=1pに対して直列に効いてくるものと考えられる。

メカ接点の場合は容量が無視できるため、高域は徐々になだらかに減衰する。

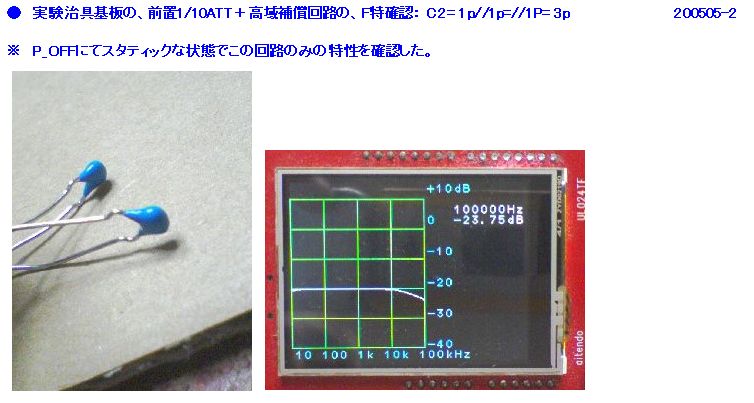

なので、C2=1pを徐々に増やしていけば、高域が上昇してくるのではと考えた。

そこで前作った実験基板にて容量を増やしながら実験をしてみた。

色々試したのを以下に示します。

・外付けCを大き目の容量:15Pにし、C2=

1p//15p= 16pとした場合、JA1WBYさんが測定されたグラフと同じような高域の

極端な上昇(ピーク)が見られた。

自分の考えは、あながち間違いではないようだ。

C2= 1p//1p//1p= 3pにした図では、だいぶ高域の減衰が、なだらかになってきた。

■ 2020.5.6

・↑↑↑ーこの状態で、入力ATT回路部のバッファ(MCP6022)出力:U2A-1pinまでの、各電圧レンジに於けるF特を測定してみた。

トータルでは変わるはずなので。

・2個パラ:計3pにすると、1V/D以上のレンジ(前置1/10+TC高域補償回路が効くレンジ)で、高域が、100kHzまで

フラット近くになるが、50k~上で、+1dBほどピークが生ずるのがちょっと気になる。

・この状態(2個パラ:計3p)TC=20pを少しずつ回してみた。

高域が少しだが動き出し、良さげな感じになる。

これでやってみる。

・クリップで引き延ばして、2p(1p + 1p)を外付け実験していたが、これだと時々、若干だがAC誘導を受けてオシロ画面上の波形表示

が乱れる(少しブヨブヨの誘導が乗った波形になる)事があるので、C12=1pの基板裏側(ハンダ面)に直接、1pを2個パラに

ハンダ付けした。

・計3pになるが、これは秋月に在庫(積層セラミック50V 3p 10本入り)があるので注文しておいた。

後で、C12を3pに交換する予定。(200508 交換済)

・SINGLE

TRIG.モードの確認を、簡単に行った。

写真は、3.3V電源の、P_ONからの立上りを観測したところです。このターゲットのではなく別のターゲットのものです。

良いようである。

■ 2020.5.7

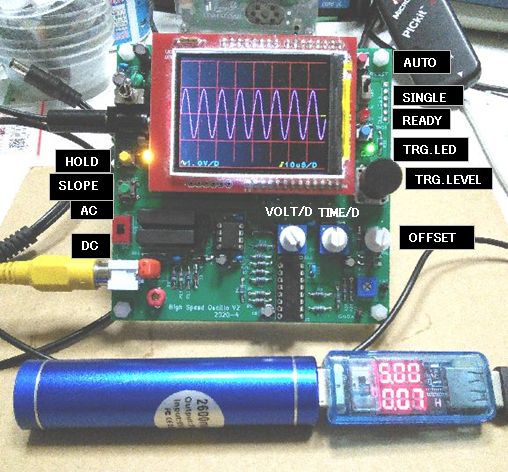

・今日は、サンプル波形取りをしてみました。

ユニバーサルで作った、1号機と同等の波形が得られたので良しとしました。

■ 2020.5.8

・稼働時の電源電圧と消費電流を取ってなかったので取ってみました。

消費電流は、70mAほどでした。(リレー1個が常にONしているので、それだけで約30mA流れています。)

<稼働時の電源電圧>

+5V : 5.18V

+5VA : 5.06V

-5VA : -4.95V

+3.3V : 3.28V

+3.3VA: 3.24V

<回路図>

・こちらからどうぞ→ 高速オシロ用入力ATT改善実験回路

High_Speed_Oscillo_V2

回路図 → 回路図を更新。(朱書きで修正部を示しました。またPIC内蔵OPアンプとの接続模様を補足しました。):200510

<最終ソース>

・こちらから、どうぞ→ High_Speed_Oscillo_V2.c

※ この他に、QVGA液晶ライブラリと、フォントデータ(ヘッダファイル)が必要ですが、

それは、テーマ72のと同様なので、そちらを参照してください。