・とりあえず水魚堂で回路図を書きながらハード構想をまとめてみる。

● 実験テーマ111

「Easy_FRA_V4 P板設計と実験」 (KiCadで、Easy_FRA_V4基板を設計し、動作確認まで行いました。)

※ 2018.12.28

→ 1回目の更新です。

POR問題の調査を、しました。

どうも、PICの不具合のようです。操作上問題無いので、交換はしないことにしました。

12月27日の記事を参照してください。

※ 2020.5.13

→ 2回目の更新です。

ソフトを更新し「Easy_FRA_V4a」としました。

マルチ描画に対応し最大8chまでのマルチ描画が可能になりました。

このページ末尾に、ソースをアップしましたので参照してください。

■ 2018.10.28

<Easy_FRA_V4計画・構想>

・CAL/MESモード切替SW追加

・CAL時は、DDSオシレータとして使えるようにする。

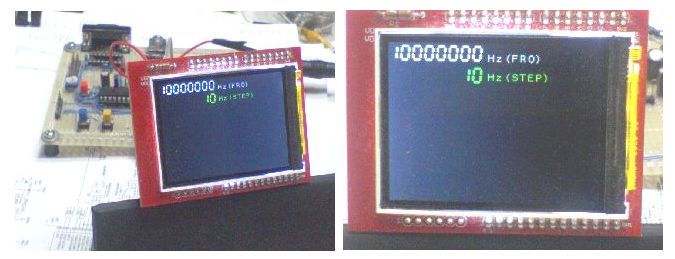

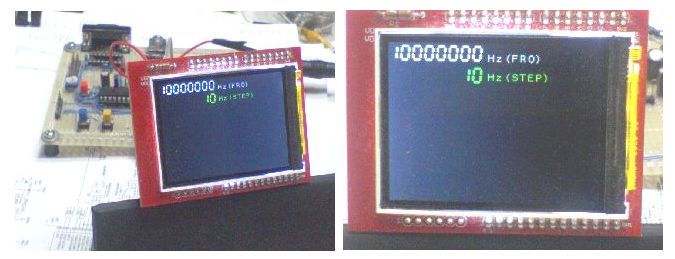

→ スルー:1Hz〜10MHz/LPF有効:1Hz〜300kHzなので、FRQと、STEPを、QVGAに表示しないといけない。

通常のキャラクタでは文字が小さすぎて体裁が悪いので、前やった、7SEG表示の大きい文字にしてみる。

まずは、PIC24Fでこれの単体実験をしてみる。

実験テーマ104で、PIC32MXを使用してこの実験をしているので、これをPIC24Fにそのまま移植してみる。

ただ、5桁MAX表示の関数なので、これを8桁MAXに変更してみる。

・CALモード(DDSモード)

P_ONで、DDSモードになる。

QVGAに、以下を表示。

FRQ:xxxxxxxxxHz

STEP: xHz

・カットオフ:Fc/10の、周波数にセットし、START SWを押すと、CALスタートする。

LEVELボリュームで、同周波数でのスイープが終わるまでに、0dBラインに合わせる。

・途中での、STOPは無しで、中断は、RESET SWによる簡単なものにする。

・全スイープが終了すると、START SW

読込み待ちになる。これを繰返す。

・MES(計測)モード

CALモードから、MESモードに切替えると、計測モードになる。

① "START TEST"表示

② START SW ON待ち

③ START SWを押すと、DDSスイープがスタートし、通常の測定画面にて、F特描画が始まる。

④ 途中の中断は、RESET SWによる。

・MPUは、ポート数の多い、TQFP44の、PIC24FJ64GA004

を使用。

■ 2018.10.29

・PIC24Fにそのまま移植は上手く行く。

・5桁MAX表示の関数なので、これを8桁MAXに変更→ これも上手く行く。

→ ソースは以下です。

PIC24F_QVGA_7SEG_DISP_TEST.c

colorlcd_libPIC24FVH_v2.c

colorlcd_libPIC24FVH_v2.h

ASCII12dot.h

・とりあえず水魚堂で回路図を書きながらハード構想をまとめてみる。

■ 2018.10.30

・ハード構想ほぼまとまる。

■ 2018.10.31

・ハード構想ほぼまとまる。

・5桁MAX表示の関数なので、これを8桁MAXに変更、上手く行ったが7segで表示を動かすところまでやってみる。

本番に備えてDDSモード(7segで表示)のデモソフトを作ってみる。

→ ソースは以下です。(メインソースのみ異なり、他ライブラリは、10/29のものと同じです。)

QVGA_7SEG_DISP_AD9833_TEST.c

→ hex準備出来た。

→ 動作チェックもOK!!

■ 2018.11.01

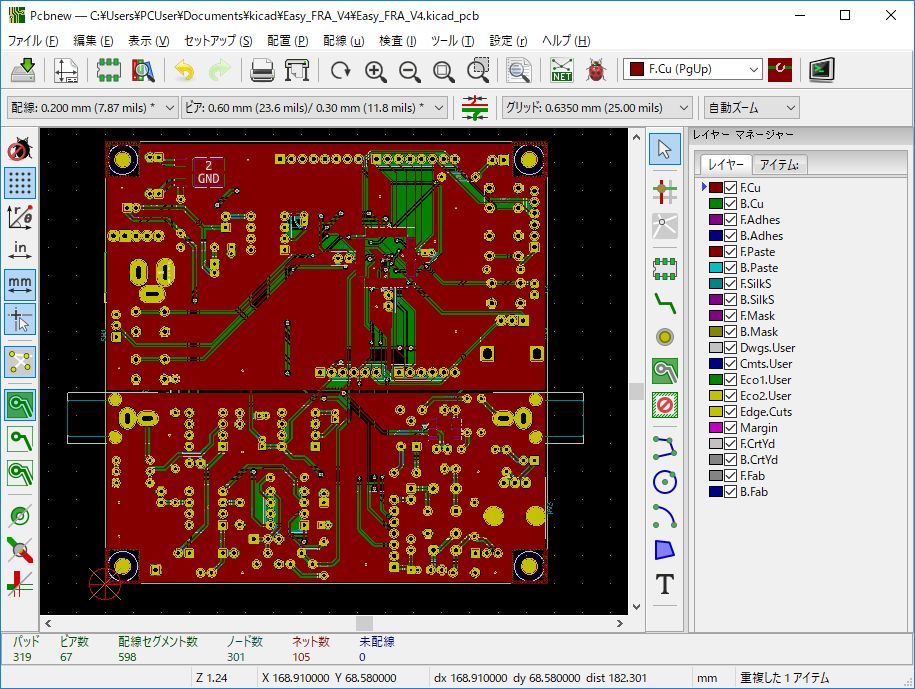

・KiCadにて、P板設計に入る。

・とりあえずは今判っている範囲で、新規パーツの、シンボル・フットプリント作りから入ることに。

<主な新規パーツ>

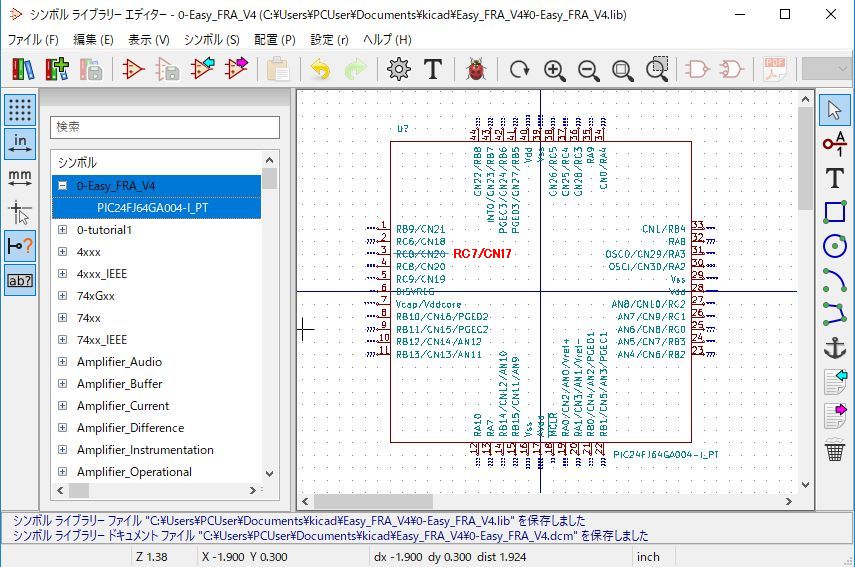

① PIC24FJ64GA004-I/PT→ 秋月通販コード I-02522

② GAOHOU_AD9833

③ Rエンコーダ:EC12E2420801→ 秋月通販コード P-06357

④ LMH6723

⑤ RCAジャック:RJ-2410N→ 秋月通販コード C-02386

・プロジェクト名を決めないといけない。

プロジェクト名:「Easy_FRA_V4」とする。→新規作成

プロジェクト・フットプリント・ライブラリ名:「0-Easy_FRA_V4.pretty」とする。

プロジェクト・シンボル・ライブラリ名:「0-Easy_FRA_V4.lib」とする。

ここに作成。

① PIC24FJ64GA004-I/PT→ 秋月通販コード I-02522

・標準にはシンボル無かった。

MCU-Microchip_PIC24 - PIC24FV・・・・しかない。

新規作成することにした。

シンボル名:PIC24FJ64GA004-I_PT

<追記:181119>

・ボード手配終了後、シンボルミス発覚

3pin= RC8/CN20は、4pinとダブル→ RC7/CN17が正解(朱書き部分参照)

もうボード手配済なので、このプロジェクトでは直さないことにした。

直すと、フットプリント割付け+ネットリスト+読込をやり直すので、リスク大。

次回何かのプロジェクトの時、シンボル名を、「PIC24FJ64GA004」と、異なる名前にして修正することにした。

フットプリントは標準に有り→ Pakage_QFP-TQFP44_10x10mm_P0.8mm 181103

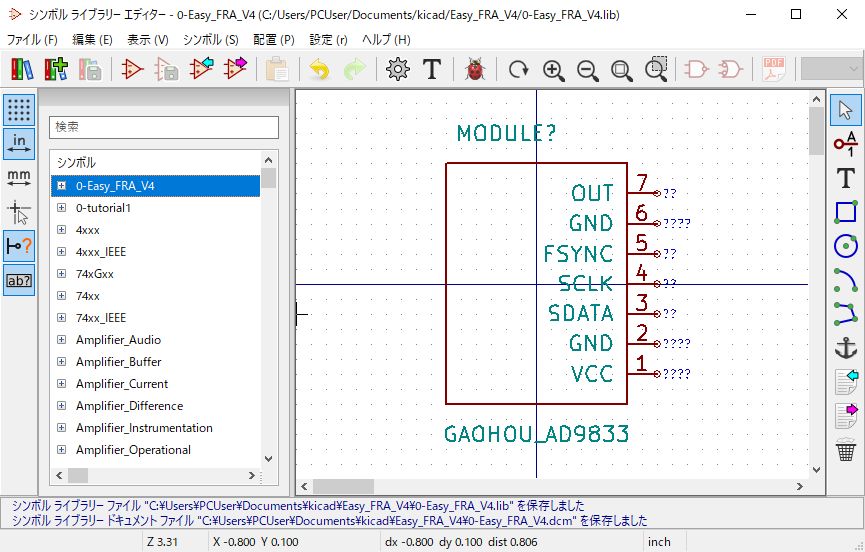

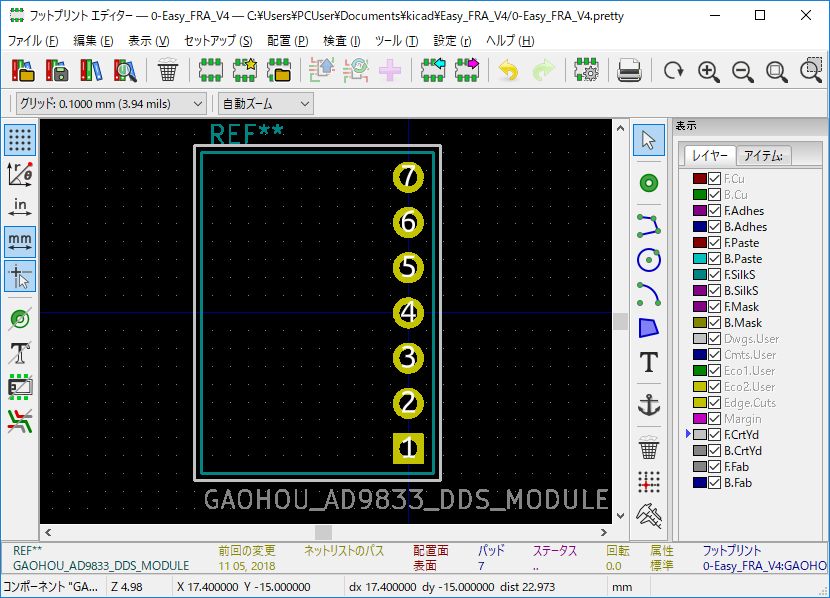

② シンボル名:GAOHOU_AD9833 181105[済]

フットプリント名:GAOHOU_AD9833_DDS_MODULE

③ Rエンコーダ:EC12E2420801→ 秋月通販コード P-06357

標準シンボル有り、そのまま使用。ガイド穴2つは、シンボルに入れず、フットプリントの時、padを置けばよい。

Device - Rotary_Encoder

フットプリントは標準に有り→ Rotary_Encoder-RotaryEncoder_Alps_EC12E_Vertical_H20mm 181103

これは。MP(マウント・ホール)が角パッド・長穴スルーで、ベースからシャフト先端までの高さが20mm(フットプリントには関係無いが・・)

のタイプ。

■ 2018.11.02

・続き。

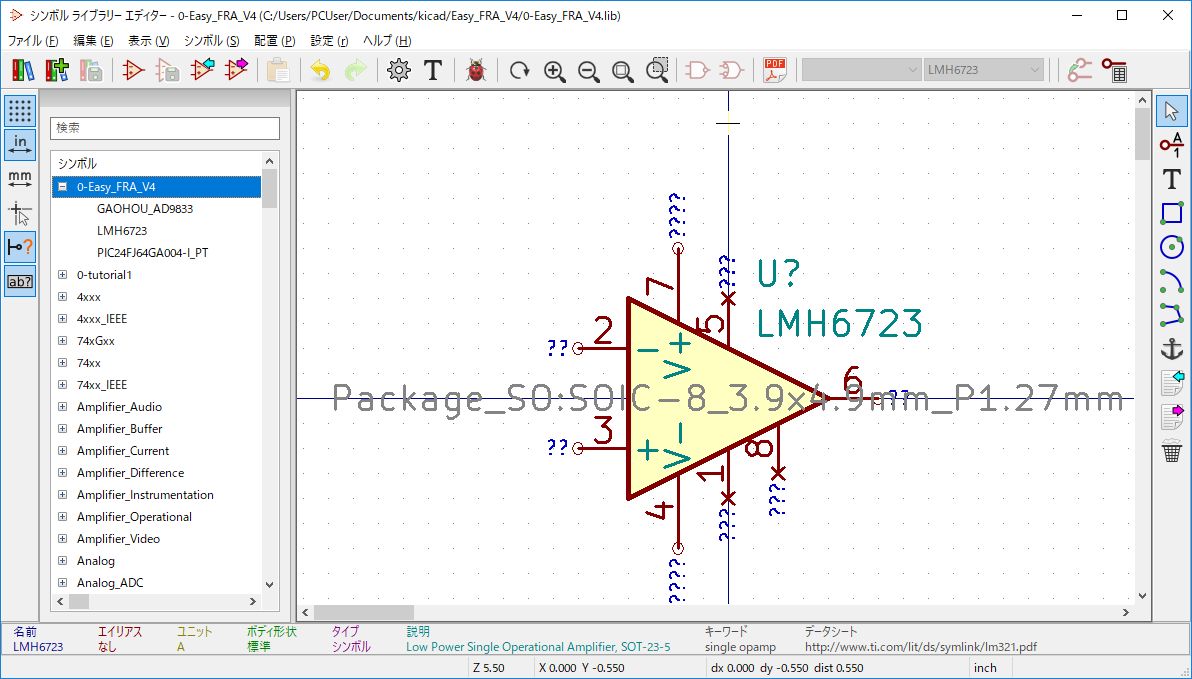

④ LMH6723

8pin SOIC 1.27ピッチ

1パッケージ・1ユニットでピン番違いが標準シンボルにあったので→ Amplifier Operational-LM321

これをコピー・修正して使うことにした。

パッケージは標準に有り、そのまま使う。→ Package_SO-SOIC-8_3.9x4.9mm_P1.27mm

<その手順>

① 最初にKiCad の初期画面からコンポーネント ライブラリ エディタを選択する。

② ライブラリの選択ダイアログで、LM321を選択し右クリック→ 「シンボルをコピー」

③ 「0-Easy_FRA_V4」右クリック→ 「シンボルを貼付けで、プロジェクト・シンボル・ライブラリへコピー

④ コンポーネント名を右クリックして、[編集]をクリック

⑤ パッケージ名を、「Package_SO:SOIC-8_3.9x4.9mm_P1.27mm」へ変更

⑥ ピン番変更・追加NCピン

■ 2018.11.03

・続き。

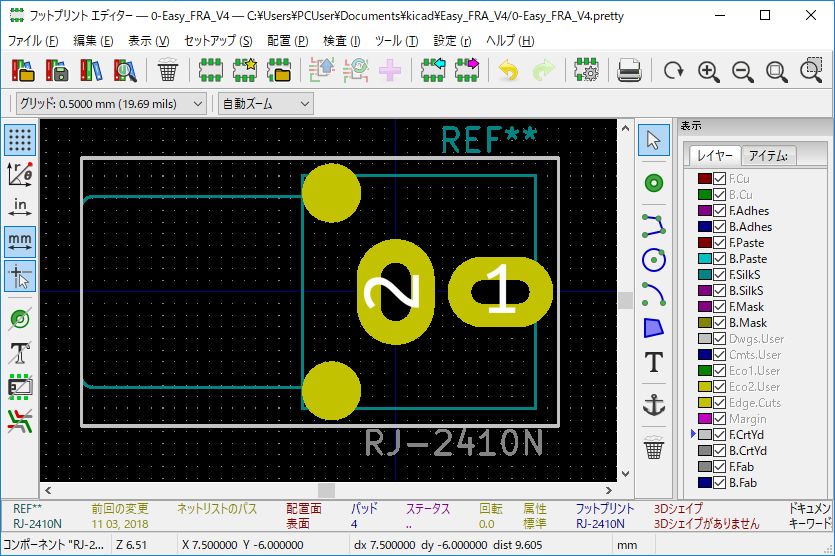

⑤ RCAジャック:RJ-2410N→ 秋月通販コード C-02386

シンボルは標準に有り→ Connector-Conn_Coaxial

フットプリントは標準に無し、新規作成することにした。→ フットプリント名:RJ-2410N

角のRの描き方は、ややこしい。

円弧描画だが、R=0.5にし、適当に1/4(270°)の円弧にして描画後、Rコマンドで回転させ

正規の位置に移動する。

機構穴(バカ穴)の追加

パッド形状のところで、[NTPH(メッキなし貫通穴)、機構穴]を指定し、穴サイズとパッドサイズ

を同じにすればよいはず。

プレビューで見ると、ベタの円になっているが? 置いてみた時、確認ということで先に進める。

■ 2018.11.04

・DDS AMPのレベル調整VR:RK09Lの、フットプリントは、標準にあったので、それを使用。

Potentiomater_THT-Potentiomater_Alps_RK09L_Single_Vertical

・主なパーツ以外で調査が必要なパーツ

① インダクタ

標準のシンボルを使う。→Device- L

フットプリントは、リードタイプで縦実装のものを標準から選んで使う予定。

■ 2018.11.05

・続き。

① インダクタ

標準のシンボルを使う。→Device- L

フットプリントは、リードタイプで縦実装のものを標準から選んで使う。

・330uH:秋月マイクロ・インダクタ[AL0510-331K] "Core Mastor Enterprise"

→ Inductor_THT-L_Axial_L14mm_D4.5mm_P5.08mm_Vertical_Fastron_LACC // ちなみに、Fastron_LACCは、メーカー名と型番で、これと互換有り

(データシート寸法:L14max, D5max,リード径=0.6φ) |- 代理店:マウサー日本

・22uH:秋月マイクロ・インダクタ[AL0307-220K]

→ Inductor_THT-L_Axial_L6.6mm_D2.7mm_P2.54mm_Vertical_Vishay_IM-2 // ちなみに、Vishay_IM-2は、メーカー名と型番で、これと互換有り

(データシート寸法:L8max, D3max,リード径=0.55φ)

■ 2018.11.06

・続き。

② 積層セラミック・コンデンサー

標準のシンボルを使う。→Device- C

フットプリントは、標準から選んで使う。

・50V1000p:秋月[RD15N102J1HL2L-10] "Supertech Electronic"

→ Capacitor_THT-C_Disc_D3.8mm_W2.6mm_P2.50mm

(データシート寸法:L4max, T2.2max,P2.54リード径=0.5φ)

・50V470p:秋月[RPE2C1H471J2K1A01B] "村田" 手持ち有

→ Capacitor_THT-C_Disc_D5.0mm_W2.5mm_P5.00mm

(データシート寸法:L5max, T2.5max,P5リード径=0.5φ)

・25V10u:秋月[RDEC71E106K2K1C03B] "村田"

→ Capacitor_THT-C_Disc_D5.0mm_W2.5mm_P5.00mm(上と同じでOK)

(データシート寸法:L5.5max, T3.15max,P5リード径=0.5φ)

③ 電解コンデンサー

・16V470u:秋月[16WXA470MEFC8X9] "ルビコン"

→ Capacitor_THT-CP_Radial_D8.0mm_P3.50mm

(データシート寸法:D8max, P3.5リード径=0.6φ)

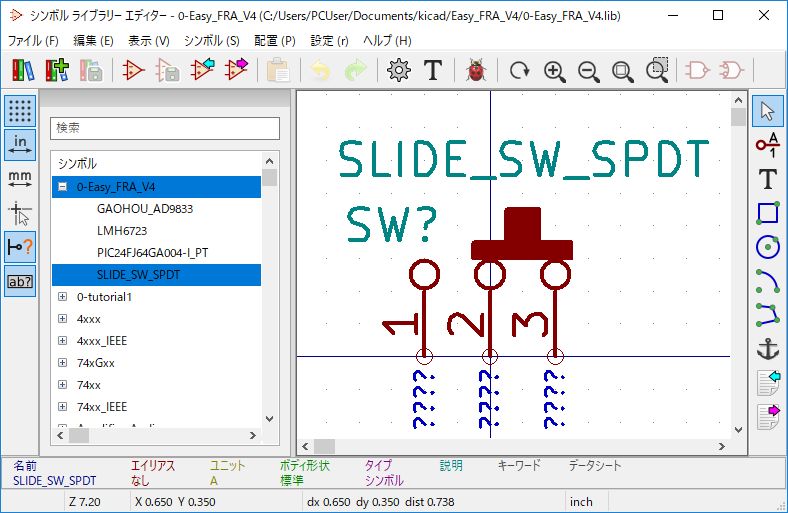

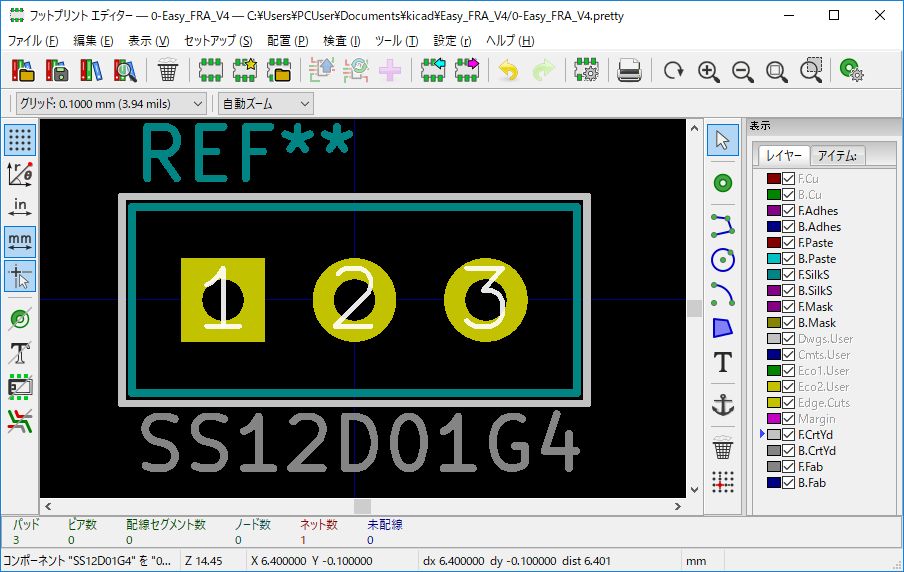

④ スライドSW

・秋月[SS12D01G4]

標準にシンボル無し。新規作成→ SLIDE_SW_SPDT

標準にフットプリント無し。有るのは、SPSTタイプのみ、新規作成→ SS12D01G4

⑤ LED

以下標準を使う。

シンボル:Device-LED_ALT

フットプリント:LED-THT - LED_D3.0mm

⑥ +5VA→ 標準シンボル使用:power - +5VA 尚、-5VAは直接接続する予定。

・新規ものはこれで終了。

これ以外のパーツについては、_V3プロジェクトのものを利用するので、以下の手順で、_V4プロジェクトに

組み込む。(この作業は今回初めて)

<小坂氏pdfより>

13.12. 他のプロジェクトで利用する。

① 利用先のプロジェクトのフォルダ配下に0-tutorial1.libと0-tutorial1.prettyをコピーします

② 回路図エディタEeschemaからメニューバー「設定」→「シンボルライブラリを管理」と進

み,0-tutorial1.libをプロジェクトに組み込みます。

③ レイアウトエディタPcbNewからはメニューバー「設定」→「フットプリントライブラリを

管理」と進み,0-tutorial1.prettyをプロジェクトに組み込みます。

■ 2018.11.07

・回路図作成準備完了。

・回路図作成開始

■ 2018.11.08

・続回路図作成 アノテーションまで終了

・ここで、転記ミスが無いかチェック→ 一部NG修正しOK

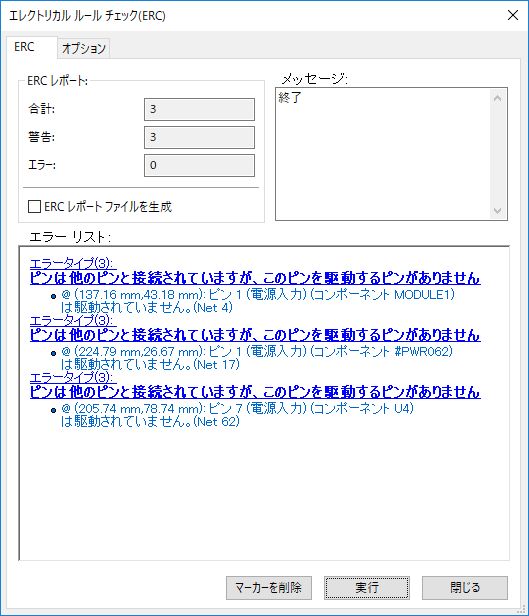

・ERCチェック

警告3点(全て「ピンは他のピンと接続されてますが、このピンを駆動するピンがありません」)

① MODULE1-VCCピン→ コイルを介しての、VCC接続の為、警告が出ているだけなので承認

② LMH6723-VCCピン→ 抵抗を介しての、5V接続の為、警告が出ているだけなので承認

③ AD8307-VCCピン→ 抵抗を介しての、5V接続の為、警告が出ているだけなので承認

■ 2018.11.09

・フットプリント割付け終了

・ネットリスト生成終了

・部品表作成

WEBで良いものを見つけた。→ Scratchpad@usagi1975.com

「Kicad Simple BOM Generator」

Kicadで生成された、BOM(XMLファイル)をネット上で動くソフトで開くと、エクセル表に

変換してくれてダウンロードできる。

個々の部品の数量を確認できるので便利。

■ 2018.11.10

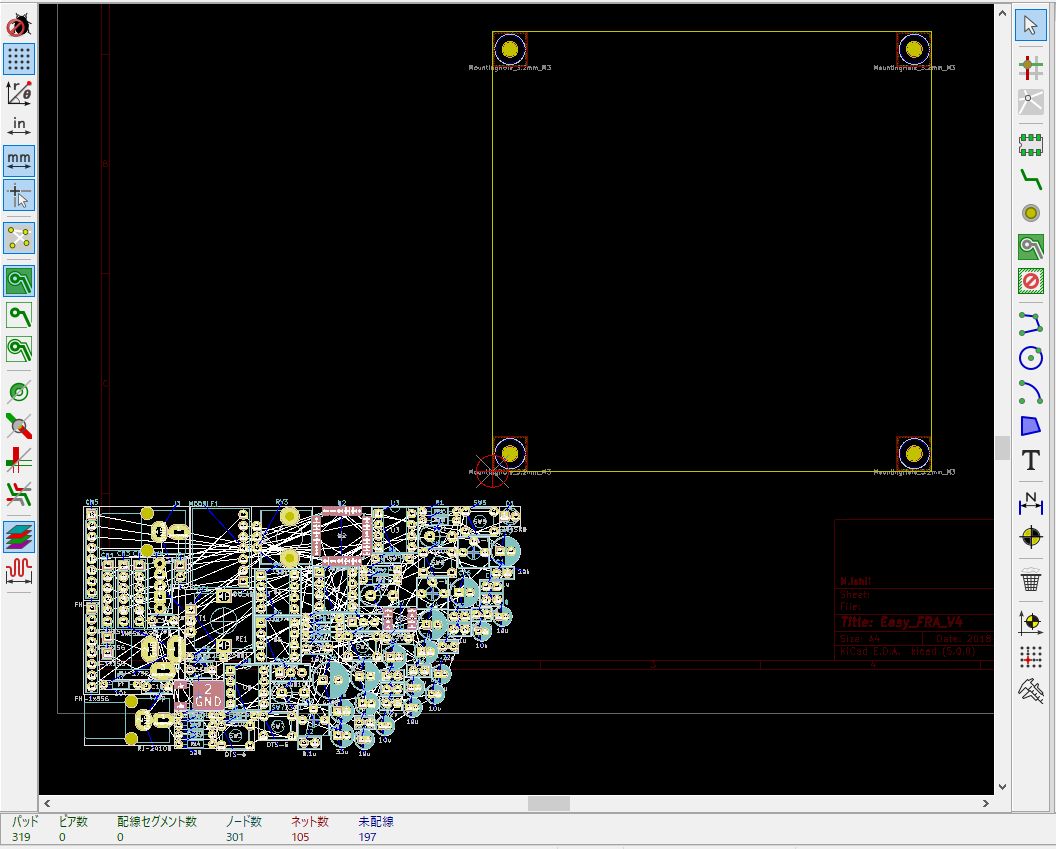

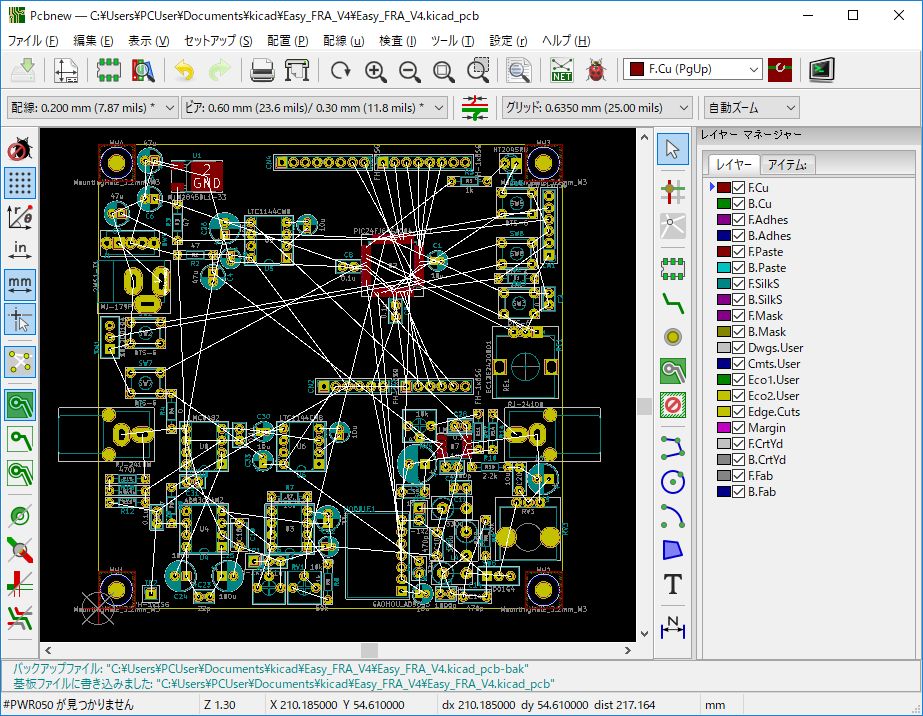

・基板レイアウト設計:PcbNew 開始

① 基板外形レイヤは、Edge.Cut

② 作業原点設定

PCBサイズ:100x100mm

作業原点:(99.06, 154.94)を、リセットして相対座標:dx,dy=(0,0)とする。

尚この位置は、図枠中央やや左下であればOK

③ デザイン・ルール設定は、毎回必要。

FUSION PCBに準拠

④ 取り付け穴 4個置く

最初に、左下指定位置に一個置く。

この状態で、ホールを、CTRL+Dでコピーして、残り3個を指定位置に配置

一個一個、ホールを選択(ポインタで囲んで選ぶ)し、Eを入力すると、フットプリントのダイアログが開くので、リファレンス欄の、

編集]をクリック

フットプリントテキストのプロパティダイアログが開くので、リファレンス:MH*(それぞれ、*=1, 2, 3,4)

と入力し、非表示にチェックマークして[OK]

フットプリントのダイアログに戻るので、フットプリントのロックにチェックマークを入れて設定終了(それぞれ行う)

⑤ 禁止帯設定

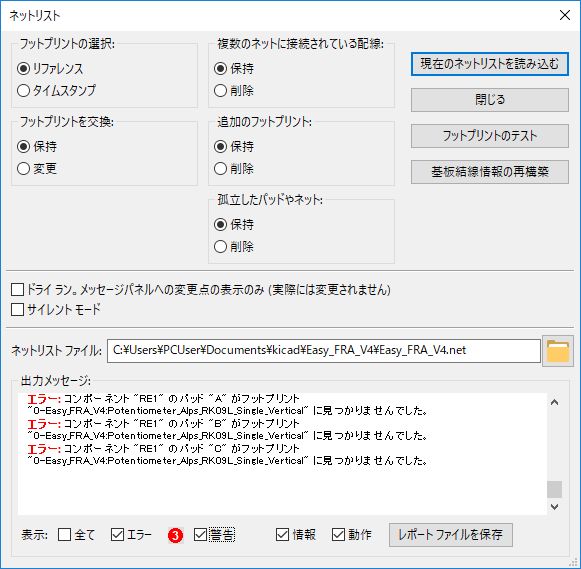

・ネットリストを読込んだが、エラー3点発生

REのフットプリント(標準)のピン番:A-C-Bが、標準シンボルのピン番:1,2,3と合っていなかった。

いやそうではない。

フットプリント割付けの段階でミスしてた。

REと、RV3(RK09L)は形が似ている。

REのフットプリントも、RK09Lに割りついていた。

この修正は何故か、CvPCBではできなかった。(V4にあるはずの、RotaryEncoder_Alps_EC12E_Vertical_H20mmが見当たらない?)

そこで、回路図上のREシンボルを右クリック→ プロパティ編集で、フットプリント・フィルド定数の変更を行う。

ここでCvPCBに戻ると、RotaryEncoder_Alps_EC12E_Vertical_H20mmに置き換わっているので保存。

この状態で、ネットリスト再生成

BOMも再生成

⑥ やっとのことで、ネットリストを読込み成功

■ 2018.11.11

・基板レイアウト設計:PcbNew 続き

⑦ 部品配置。まずは、fix部品の、QVGAコネクタ:CN2-5

今回は、コネクタの1pin位置を、編集(E)で、プロパティダイアログを開き、X, Yの絶対座標に

dx,dyの相対座標を、X, Yの絶対座標に変換して手入力することにした。

変換式は、以下(各定数は、作業原点の、相対座標)

X= dx + 99.06

Y= 154.94 - dy

この式によって計算すると、入力する絶対座標は、以下になる。

CN2:(147.74 , 107.07)

CN3:(165.52 , 107.07)

CN4:(138.66 , 58.81)

CN5:(160.44 , 58.81)

■ 2018.11.12

・基板レイアウト設計:PcbNew 続き

⑧ 部品配置続行

途中で、NETミス発覚

C22-2pin +5Vは誤り→ GNDAに修正(回路図に戻って修正後、ネットリスト再生成→ PcbNewで再読み込み)

修正済

部品配置暫定終了

・QVGAの、フットプリント確認

■ 2018.11.13

・ベタ生成作業

この作業に入る前に、またまたネットミス発覚。

大元の、+3.3VAのグランドが、GNDになっていた。→ 回路図上でGNDAに修正し、フォワードアノテーションする。

GND領域にある、GNDAネットをGNDA領域に手配線してからベタ生成する。

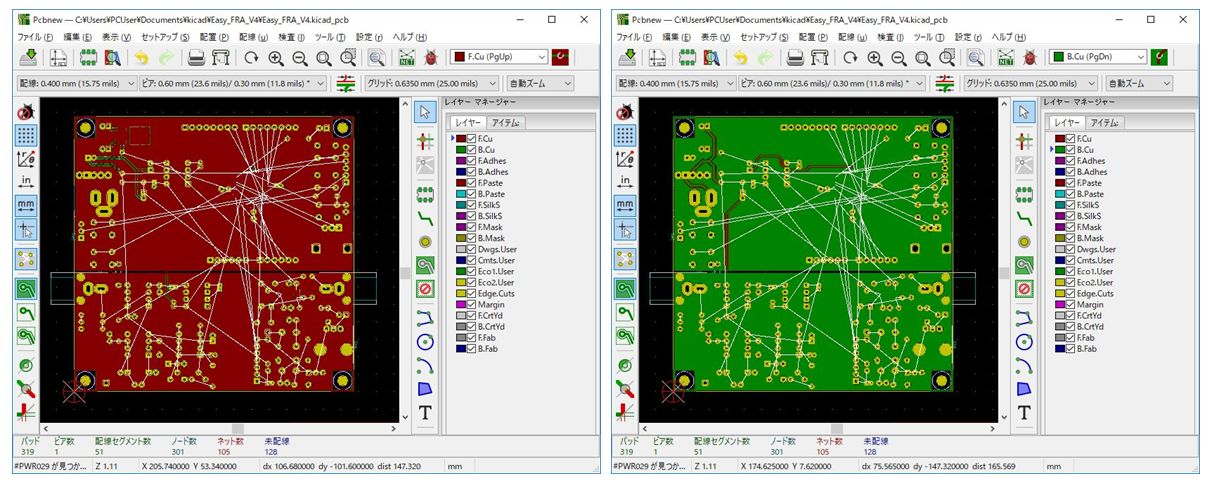

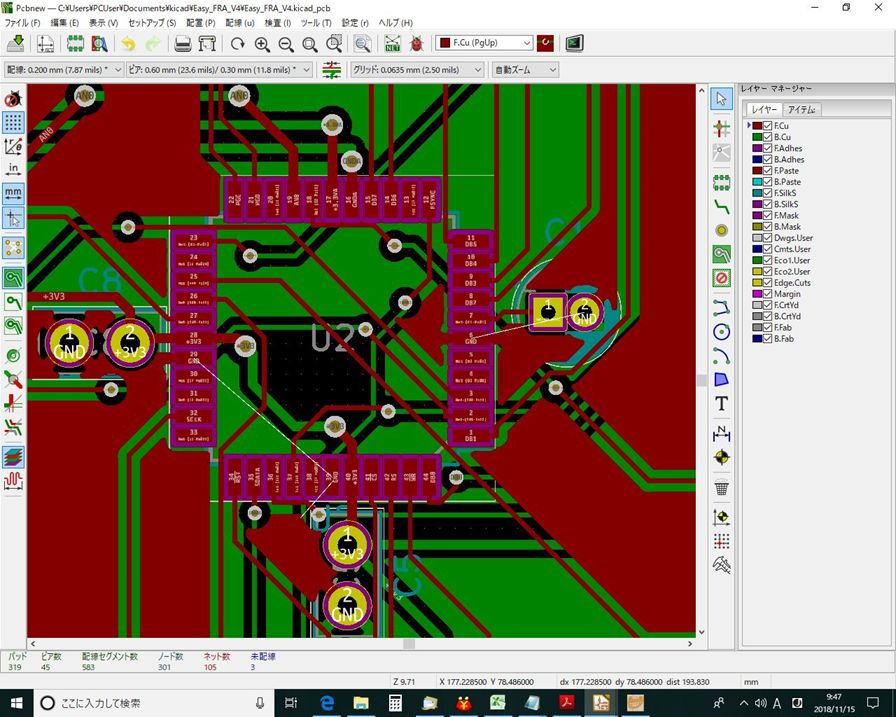

■ 2018.11.14〜 2018.11.15

・電源ライン終了

・アナログライン終了

・オートルータ 10分位掛かったがコンプリート

・セッションファイルマージ後、DDSモジュールのGNDがベタから浮いている事にきずき修正

・オートルータで不自然な流れになっていたSDATAライン手直し再度オートルータコンプリート

・再オートルータ後セッションファイルマージ

・オートルータ後、気に入らないライン手直し

181115

・未配線発覚

未配線3箇所:GNDピンがベタから浮いている

未配線3箇所修正:TQFP_GNDピン付近のパターン移動し島を広くしそこにビア打ち。

他数か所ビア打ち。

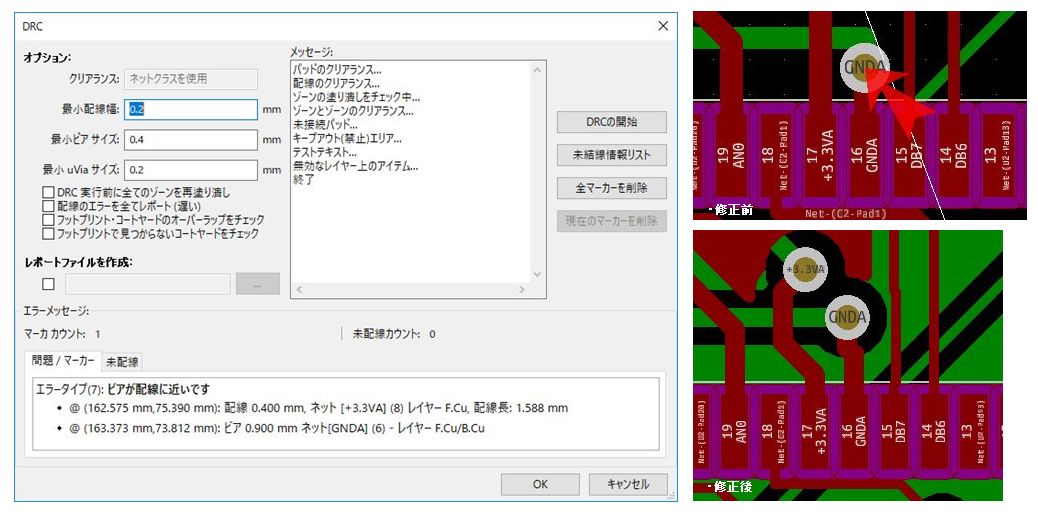

・DRC_1箇修正でOKになる

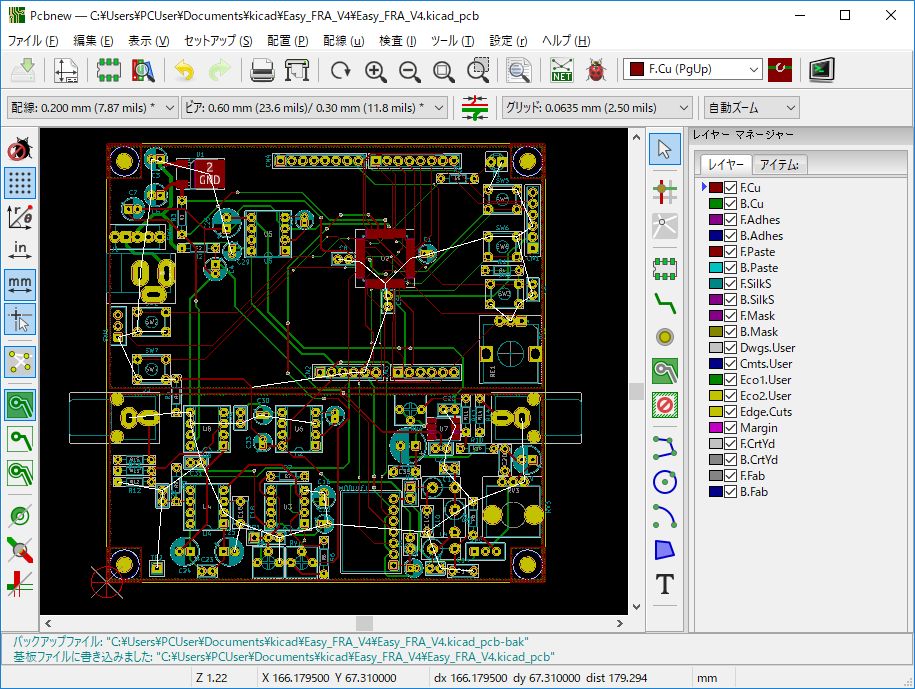

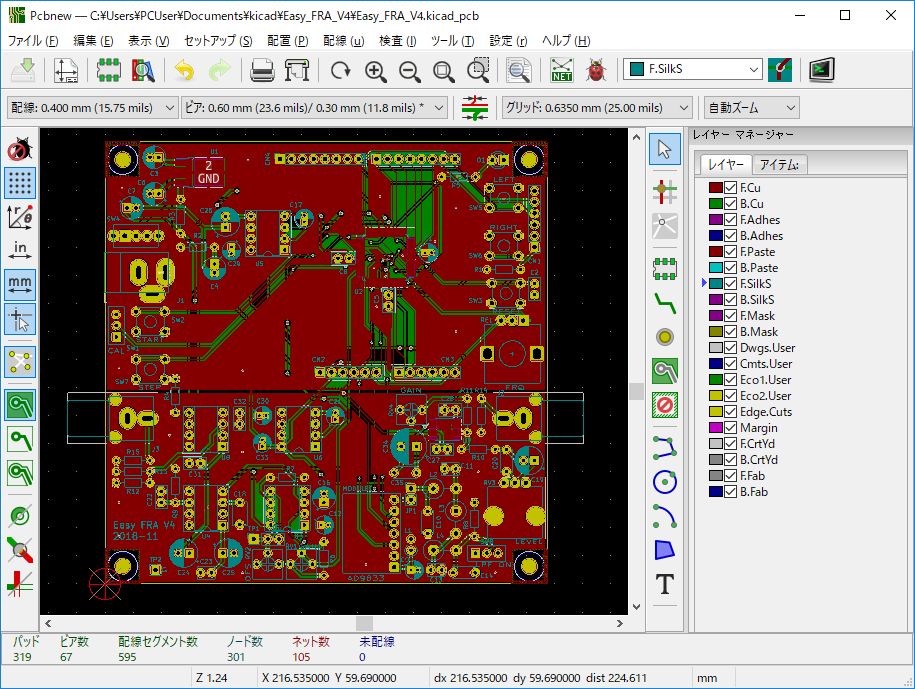

・シルク整理・PCBNew作業終了

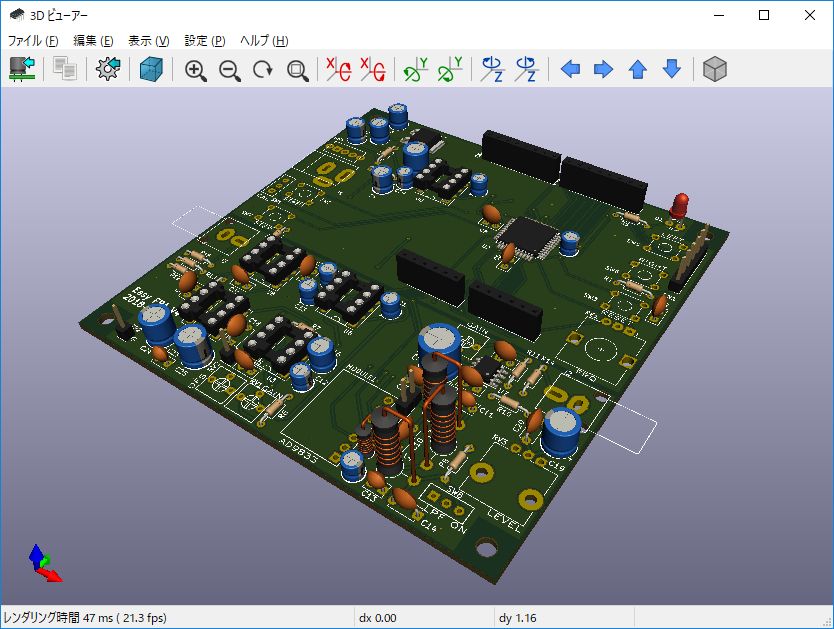

・3Dビューワ確認

■ 2018.11.16

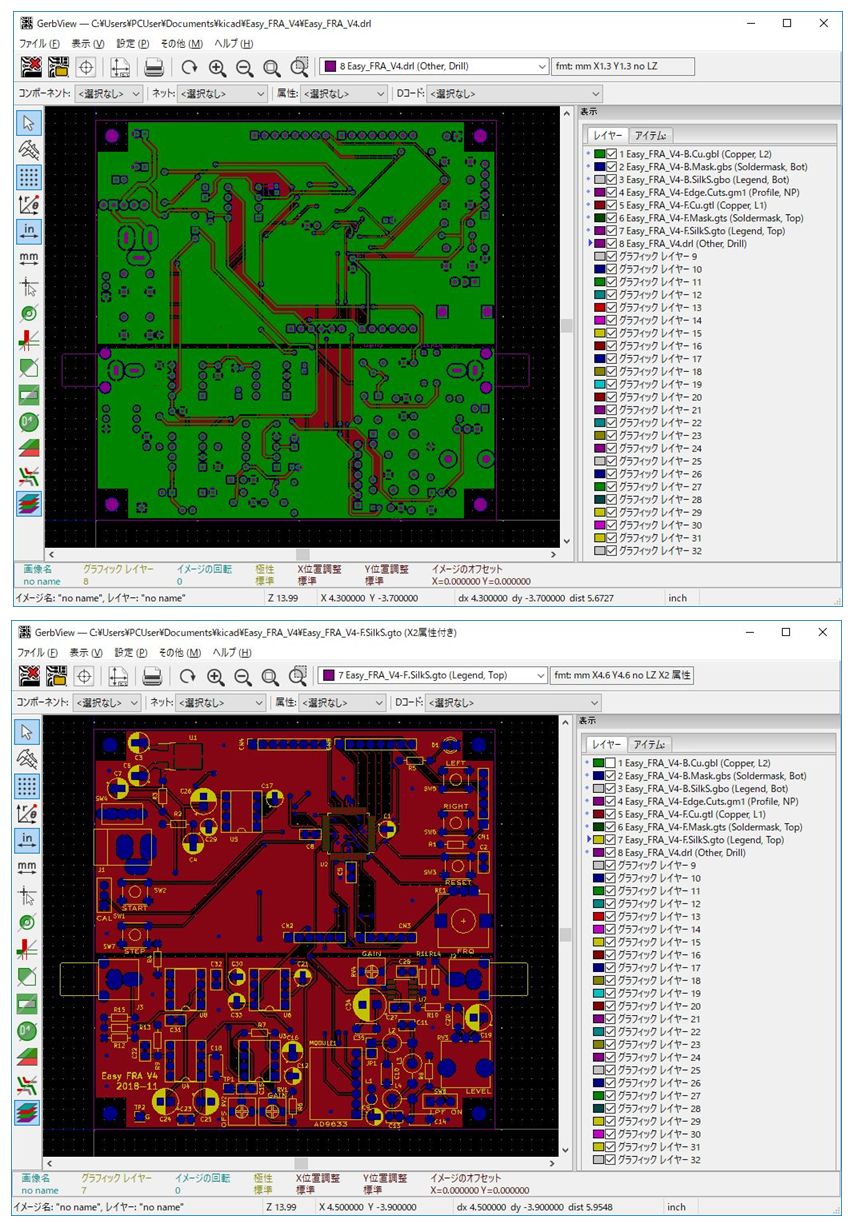

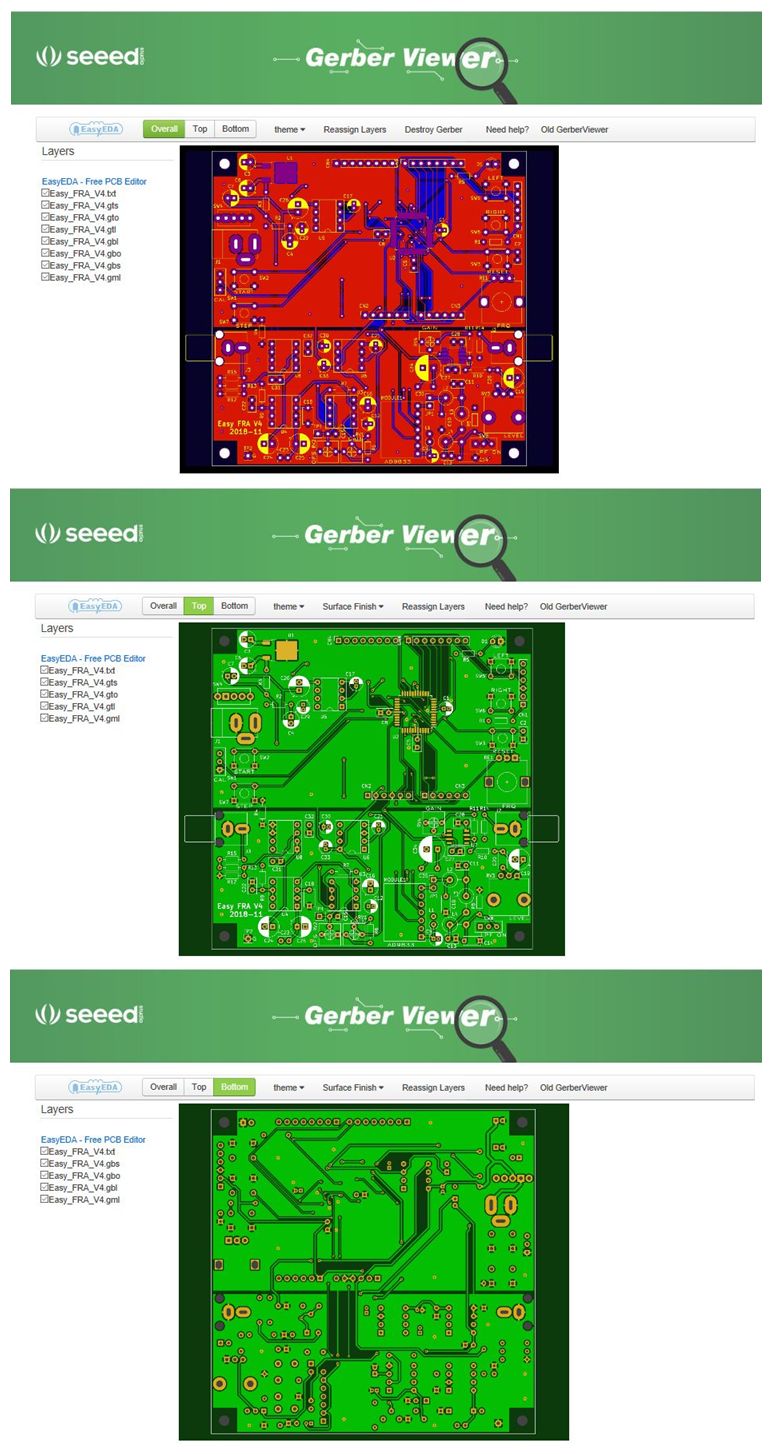

・ガーバー生成作業終了

ガーバーファイル設定+ドリルファイル設定は、このようにしました。

・ガーバー確認作業終了

(確認作業途中、シルク位置不適当発覚修正した。)

・FusionPCB発注作業

100x100 10枚の場合、入力はデフォルトのままで良い。

20%割引クーポン使用で、送料込み:2577円

・部品手配

秋月分:2410円

MARUTU分:950円

RS分:149円 VISA払い

■ 2018.11.21

・ソース書き上げた。

コンパイル〜HEX準備OK

■ 2018.11.23〜 2018.11.26

・机上デバッグ

フローを書いてみる。

・書いたら、仕様が不自然な箇所を見つけ、修正した。→ ソースも修正

※ 181126 午後14:00

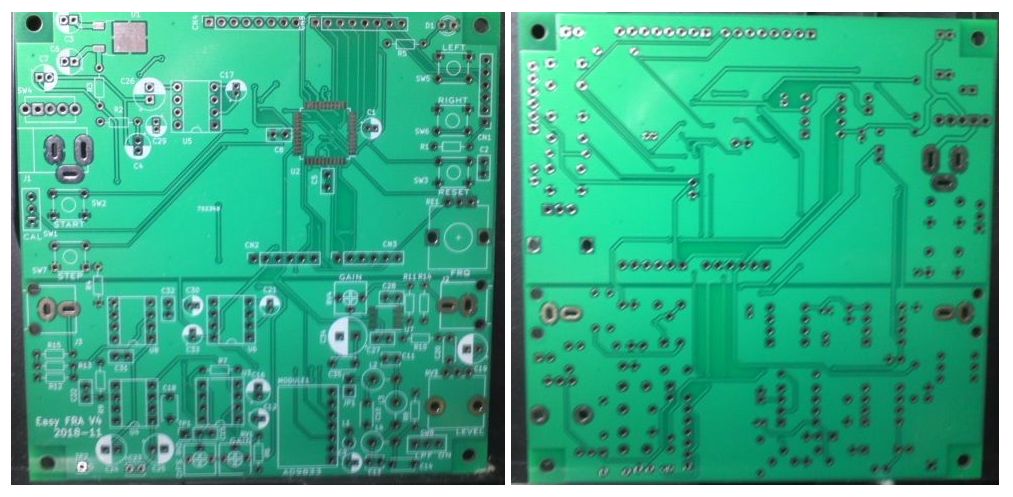

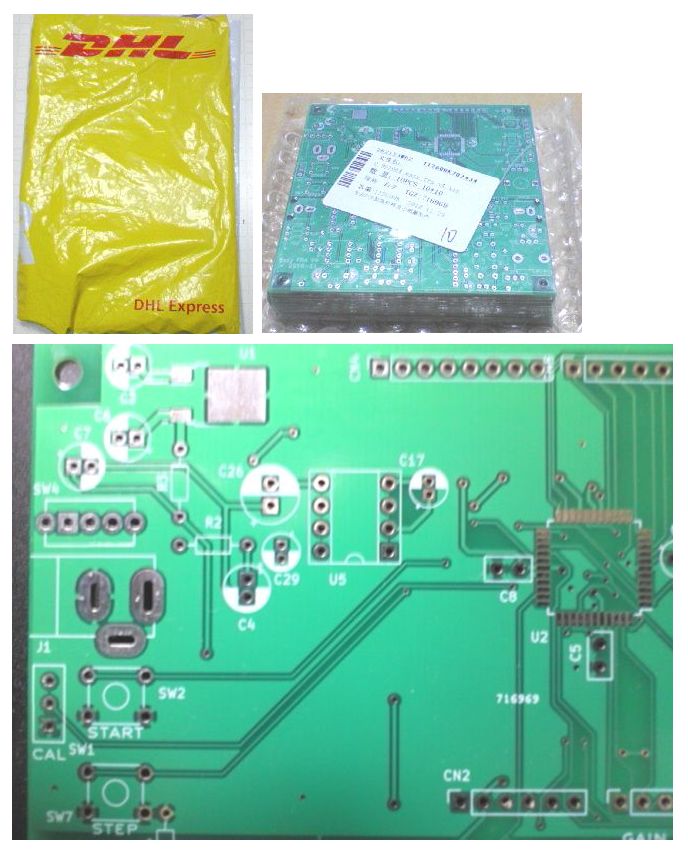

・P板到着(FusionPCBの、しおりが、2枚サービスで付いていました。)

<早速目視チェックしたところ全枚数に不具合を見つけ、FUSIONサポートに報告メールした>

早速、開封して、外観の目視チェックをしてみたところ、大方OKでしたが、

ビアにレジストがされた状態で仕上がっていました。

こちらで発注時の、製造ファイル出力の設定控えを確認したところ、

一般オプション欄の、「ビアのテンティングを禁止」にはチェックマークが入っていました。

また、発注時、御社のガーバービューワで再確認した画像控え(念のため、今日も再確認した)

で見ても、ビアにレジストはされていません。

(画像を添付しましたので御覧いただければと思います。)

失礼ながら御社の手違いとも考えられるので、確認お願いいたします。

実装は今の基板でも問題ないのですが、指定通り上がってないので、気になっています。

出来れば、やり直しサービスを適応していただきたいのですが、無理でしょうか?

可能なら、その手続き方法を教えてください。

・FUSIONからの返信:1回目

石井様:

弊社ご利用頂き、誠にありがとうございました

FUSION TEAMのリンチコウと申します。

確認のため、実物の写真こちらまで送っていただけないでしょうか。

よろしくお願いいたします。

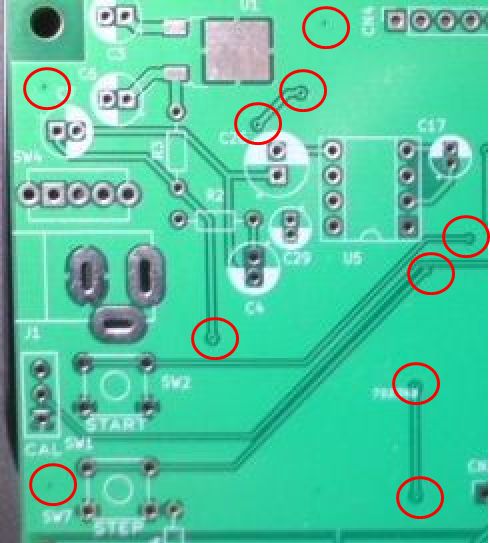

→ 以下、送付した写真です。

・FUSIONからの返信:2回目

石井様:

いつもお世話になっております

チコウです。

ご協力頂き、誠にありがとうございました。

写真に問題があるところにマークしていただけないでしょうか。

説明不足のことに深くお詫び申し上げます。

よろしくお願いします。

→ これに対し、マーク付き、P板の拡大写真を送った。

<参考:FUSIONサイトに書かれていた、不具合時の対応>

基板の不良または不具合品の対応

よくある質問(Fusion向け)

基板に不良や不具合があった場合は、

以下の情報をまとめて fusion.jp@seeed.cc までにお知らせください。

1. 注文番号

2. ファイル名

3. 欠陥/不良の詳しい説明とマーク写真。また不良製品の数を教えてください。

4. 運送状の写真

事情を確認してから、補償の対応をいたします。

<WEB検索:ごはんたべたよサイト「FusionPCBでプリント基板を製造した話 その2(再生産)」>

fusion.jp@seeed.cc(日本用の問い合わせ窓口)に対し、メールで状況を伝えると、

クーポンが送られてきました。クーポンを使って再度発注する、というスタイルのようです。

なお、このクーポンは送料にも適用できるため、ほぼ無料(※)で再度発注ができるようになっています。

前回と比べ、とても素早く対応いただき、発注から1週間で納品されています。

■ 2018.11.27

・FUSION PCBから回答があった。 18:00に確認

石井様:

いつもお世話になっております

チコウです。

先ほど工場からの連絡が来ました。

今回はうちの責任です。エンジニアがカバーデターを確認する時、間違ってしまいました。

不具合品で届けることに深くお詫び申し上げます。

金額の方はクーポンで返金してもよろしいでしょうか。

このクーポン使って、新しく注文すれば良いです

クーポン額:23$→ レイト11/28現在:114円/$=2622円

クーポンの注意事項:

有効期限 返事をくれた日から一年間

最低注文金額 0.01$→ 1.14円

制限 fusionサービスのみ使えます ただ、7.9$キャンペーンは対象外です

使い方 https://www.seeedstudio.com/my_coupon.htmlのページで使って下さい。

使い方についてご不明な点がございましたら、気軽に問い合わせてください。

■ 2018.11.28

・原因がはっきりして良かった。

金額の方はクーポン返金で了解することにした。返信を済ませた。

■ 2018.11.29

・クーポンを使って、再発注した。

合計(1アイテム):555.46円

送料:2142.5円(DHL)

割引:-2607.28円

クーポン(1):$23 OFF, Exp:2019/10/22

総計:90.69円

※ たぶん1Wで到着するものと思われる:12/6(木)

■ 2018.12.8

・19:00 ようやく委託運送業者:佐川急便により、P板到着

今度は、ビアのテンティングは、されてなく、問題ない仕上がりでした。

いろいろ手間が掛かりましたが、結果オーライです。

■ 2018.12.14

・実装上がり

・V4バッグ開始

(1) ショートチェック→ OK

+5V-GND

-5V-GND

+3.3V-GND

+3.3VA-GND

-3V3-GND

(2) ICはLTC1144のみ実装 QVGA未実装にて電源確認)→ QVGAの電源ピンも、OK

+5V:5.22V

-5V:-5.12V

+3.3V:3.29V

+3.3VA:3.29V

-3V3:-3.29V

(3) PICkit2により、HEX書込み→ OK :PIC24FJ64GA004認識・easy_fra_v4.hex書込みOK

(4) IC全て実装 QVGA未実装にて電源確認

+5V:5.22V

-5V:-5.12V

+3.3V:3.30V

+3.3VA:3.19V(= Vref)

-3V3:-3.19V

(5) IC全て実装 QVGA実装(稼働状態)にて電源確認しようと思ったが、

→ QVGA 白く光ったまま動かず。

・QVGAの電源ピンへの電源供給は、OK

・回路図上で、QVGAのポート割付け確認→ OK

■ 2018.12.15

(5) 続き。まずはソフトチェックから

・PICが、RUNしているか、Lチカで確認

→ ① リセットが、おかしそう?(CLOCK設定が、約半分になることがある。)

1秒間隔でブリンク設定するが、2秒位になることがある。

その時、リセットSWを押すと、1秒間隔(実測:1秒弱)になる。

② プログラムを元に戻し、

QVGAを装着して、P_ONで、CALモードを立ち上げると、ゆっくり約2秒後にイニシャルメッセージ

が表示される。

その途中で、リセットSWを押すと、液晶初期化の前に入っている遅延時間:1秒後に

正常に表示される。

一応、液晶にメッセージと、初期グラフが表示したので一安心。

→ ・CONFIG設定記述は、OK

・P_ONリセットと、リセットSWによるリセットのタイミングの違い??

a.リセットSWに入っている、0.1uが気になるが・・

→ 後閑さんhpに、PIC24FJ64GA004を使っている回路例(電光掲示板)があった。

それを見ると、このコンデンサーは、入っていた。

また、後閑さんの、CONFIG記述とも同じだった。(但し後閑さんのは外部X'tal)

■ 2018.12.16

(5) 続き。

・稼働状態電源コンディション確認

+5V:5.05V

-5V:-4.95

+3.3V:3.29V

+3.3VA:3.18V(= Vref)

-3V3:-3.19V

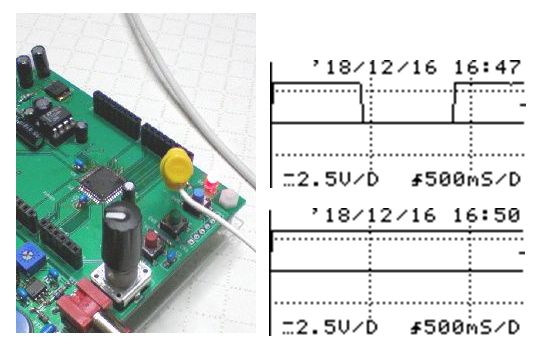

・P_ONリセット(POR)と、RESET SW1によるリセット(MCLR)で、CLOCK設定の読込が違う?

Lチカで、ON/OFF時間を、それぞれ、500mSに設定して、RUNさせると、MCLRの立ち上げ時は、

正常な周期≒1秒になるが、PORでの立上げでは、自作オシロの最低レンジが、500mS/div

なので正確な時間は不明だが、少なくとも、≒2.5秒ほどになっている。

また奇妙なのは、PORでも、ほっておくと、≒2分後には、正常な周期になる。

■ 2018.12.17

(5) 続き。

・原因不明中。

<調査予定>

① PIC:QFP44に、半田ブリッジが無いか? 目視チェック→ なさそう。

② クロックモニターが出来れば確認→ 出来ない

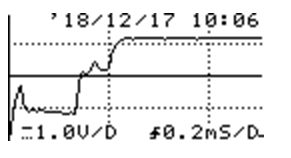

③ VCCの立上りに段が出来ているのが気になる。

データシート(セッション7.リセット)の、図7-8

デバイスリセット遅延、FRC/LPRCクロックの、タイミング・チャート

を読み解くと、PLLがロックするまでの最大時間= Tpor(パワーオンリセット遅延):10u後、2mSと規定されてい

るので、P_ON後、約2mS以上経ってから、VCCが、定常状態:3.3Vになっていれば問題ないはずなので、

約300uSで、定常状態になっているこの立上りは問題ないと考える。

またPORシーケンスは、全てPIC内のハードで行うので、ターゲット側は問題ないはず。

もしかしたら、PICのバグか、不良とも考えられる。

・P_ONして直ぐに、RESER SWを押せば、正規のクロック周波数になるので、とりあえずは

これでソフト・ハードデバッグを行おうと思う。

その間にどうするか考えて行けばよいかな。

■ 2018.12.18

(5) 続き。

・原因不明中。

<今後の作業・進め方>

① POR問題は、別ユニバーサル基板を作って、それで原因を追究する。

本日部品手配[済]

PIC32MX高速版のユニバーサル基板に、QFP44-DIP変換基板を実装すれば、デバッグ出来る。

主な部品

・TQFP44-DIP変換基板

・PIC 2個: 内1個は、PICの不良と判明した場合に、本番の基板のPIC交換の為に購入

② P_ONして直ぐに、RESET SWを押せば、正規のクロック周波数になるので、とりあえずは

これでソフト・ハードデバッグを行う。

③ ②がOK見込みがついた時点で、①を実施

④ PICの不良と判明した場合には、本番の基板のPIC交換

⑤ 先に、PIC32MX BASICボードの、ドキュメントをまとめ、HPアップ。たぶん、12月末〜1月初旬になる。

・デバッグ続行

① CAL MODE画面の、座標表示が、X,Y逆→ 修正OK

② MES MODE(LPF ON時)

トリマは、前回実験時の位置に回しておく。

ほぼ動いている模様。(LPF OFF時もOK)

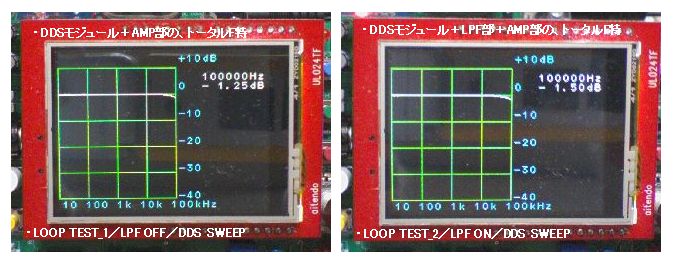

LOOP TESTで、10Hz〜60kHzまで、0dB〜-0.5dBの範囲、100kHzにて-1.0dB程度

ただ、140kHzまでスイープしてまう。

→ 直してOKになる。

③ カーソル計測操作終了後の、再スタート時、画面NG

→ 直してOKになる。

④ STEP SWは、そのモードの繰返しの頭に戻る機能を兼用。これもOK

※ これで、おおまかな動作は、OKになる。

※ 直したい点

① CAL時も、一回目はドット描画、2回目からは、ライン描画にした方がよさそう。→ 済

② イニシャルメッセージに以下を追加。

"WAIT STEP(ONCE MORE)SW ON"→ これは、特に必要ない。暗黙の了解項目にする。

■ 2018.12.19

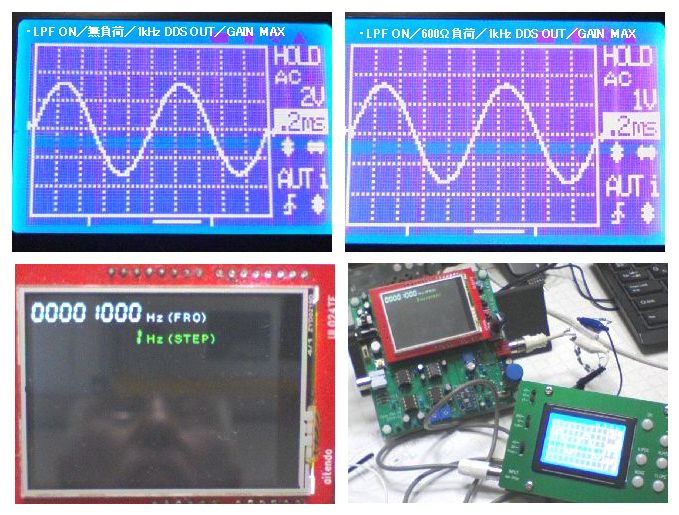

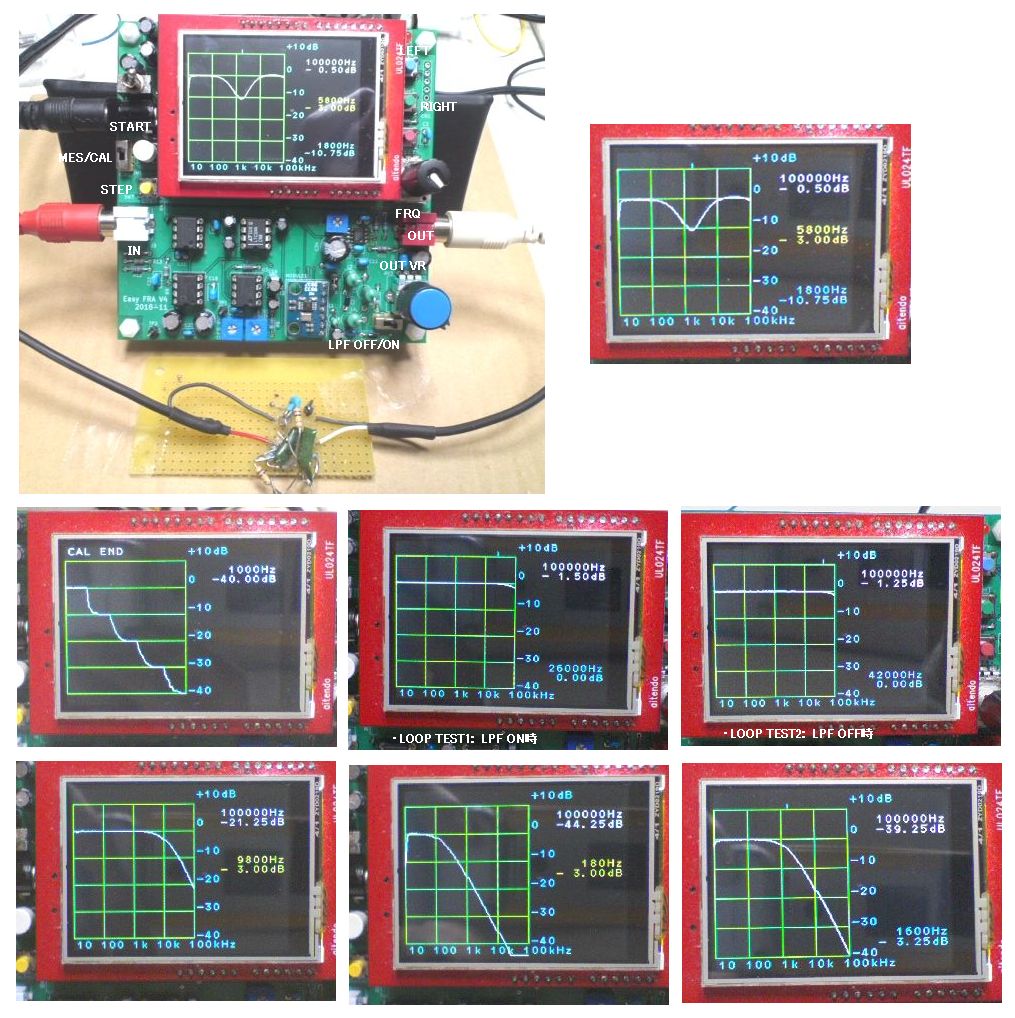

・基本動作は、OKそうなので、今日は、各ブロックのトリマ調整と波形出力確認を行う。

(1)DDSモード(CALモード)時の、DDS出力調整 1kHzにて

・前作の、AD9834_DDS発振器の実測から見た主な性能は、以下。

今回も、これと同等の性能になると思われる。一つの判断基準に使える。

① 出力レベル(GAINポテンショMAX位置)

・レベルVR最大/600Ω負荷時: 3.5Vp-p

・レベルVR最大/無荷時: 7.5Vp-p

→ LPFの有無に関係なく、上記通リになった。OK

② 出力抵抗

560Ω

③ サイン波出力の周波数特性(LPF有り)

・5Hz〜 300kHzまでは、フラット(0dBv= 0.775Vrms(600Ω負荷)→

約2Vp-p)

・-3dB点帯域は、約1.5Hz〜 450kHz(2Vp-p 600Ω 0dBv)

→ 上記通リになった。OK(中華オシロの波形レベルで概略確認)

→ しかし、(2)の調整後の、LOOP TESTでの、F特グラフ表示では、100kHz@-1.5dB(-1.75dBの時もあった)で若干減衰が多い感じ。(LPF ON時)

(2)LOGアンプ部の、調整→ 前回との違い:Vrefが若干高目なので、Vofsの調整が低くなった。

GAINポテンショは中央よりやや左で合った。

① Vref(AVCC)= 3.29V

② Vofs= 1.73V ADC入力

③ 0dB(1Vrms)入力時の、ログアンプ出力(4pin)= 2.02V : 後段アンプ出力(IC2A-1pin)= 2.44V

-10dB(0.316Vrms)入力時の、ログアンプ出力(4pin)= 1.79V : 後段アンプ出力(IC2A-1pin)= 1.88V

-20dB(0.100Vrms)入力時の、ログアンプ出力(4pin)= 1.53V : 後段アンプ出力(IC2A-1pin)= 1.29V

-30dB(0.0316Vrms)入力時の、ログアンプ出力(4pin)=1.30V : 後段アンプ出力(IC2A-1pin)= 0.73V

-40dB(0.010Vrms)入力時の、ログアンプ出力(4pin)= 1.05V : 後段アンプ出力(IC2A-1pin)= 0.15V

■ 2018.12.20

・昨日の、しかし、LOOP TESTでの、F特グラフ表示では、100kHz@-1.5dBで若干減衰が多い感じ。(LPF ON時)を追う。

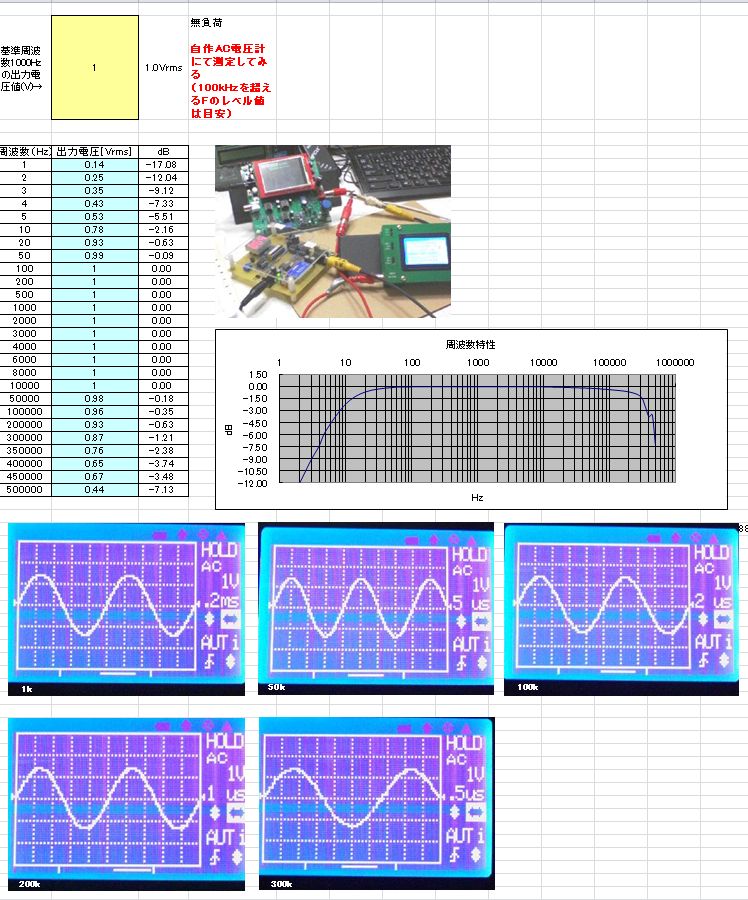

まず、DDS出力部の詳細波形を取ってみた。これは問題なさそう。

詳細波形は、こちらを参照してください。→ 波形データ_181220

以下は、測定風景です。

次に、自作AC電圧計を使って、DDS出力部の単体F特を、手取りで取ってみた。

結果、100kHz@-0.35dB(300kHz@-1.21dB)と、_V2のデータとほぼ同じになった。→ LOG AMP部の再調整を明日予定。

各ポイントの、波形もアップしました。※ 尚、0dB=1Vrmsとして測定しています。

確かに、これに比較するとズレが多少多いような気がするが・・・ 妥協してもよいレベル?

■ 2018.12.21

・LOG AMP部の再調整結果

→ Vofsは同じで、LOG AMPゲインを若干上げてみた。

これで、CAL画面で、0,-10,20,-30,-40dBレベルを入力して、ATT確認をしたところ、ATT確度はGOODな結果になった。

しかし、F特表示は、100kHz@-1.5dBで変わらず。まあ、-1.75dBまではならないので、少しは改善されたようだ。100k付近

での精度は落ちるが、妥協することにした。

LPF OFFにして、DDSモジュール直の、F特を取っても、100kHz@-1.25dBなので、モジュールの特性のせい

かもしれない。或いは、ADCのバラツキ

(_V2では、AD9834モジュールを使用)

① Vref(AVCC)= 3.29V

② Vofs= 1.73V ADC入力

③ 0dB(1Vrms)入力時の、ログアンプ出力(4pin)= 2.03V : 後段アンプ出力(IC2A-1pin)= 2.42V

-10dB(0.316Vrms)入力時の、ログアンプ出力(4pin)= 1.78V : 後段アンプ出力(IC2A-1pin)= 1.88V

-20dB(0.100Vrms)入力時の、ログアンプ出力(4pin)= 1.54V : 後段アンプ出力(IC2A-1pin)= 1.32V

-30dB(0.0316Vrms)入力時の、ログアンプ出力(4pin)=1.30V : 後段アンプ出力(IC2A-1pin)= 0.77V

-40dB(0.010Vrms)入力時の、ログアンプ出力(4pin)= 1.06V : 後段アンプ出力(IC2A-1pin)= 0.24V

※ 以下に結果写真をアップします。

ノッチフィルタ等の、サンプル取りも載せました。

<今後の予定>

・例の、POR問題をユニバーサル基板を作って個別調査予定

・これで原因がはっきりしても、今回のものに修正を加えることは、しないかも・・・

実用に問題ないので・・・

追試として、1stHP公開後にアップする予定。

---<追試:POR問題調査の記事>-------------------------------------------

■ 2018.12.27

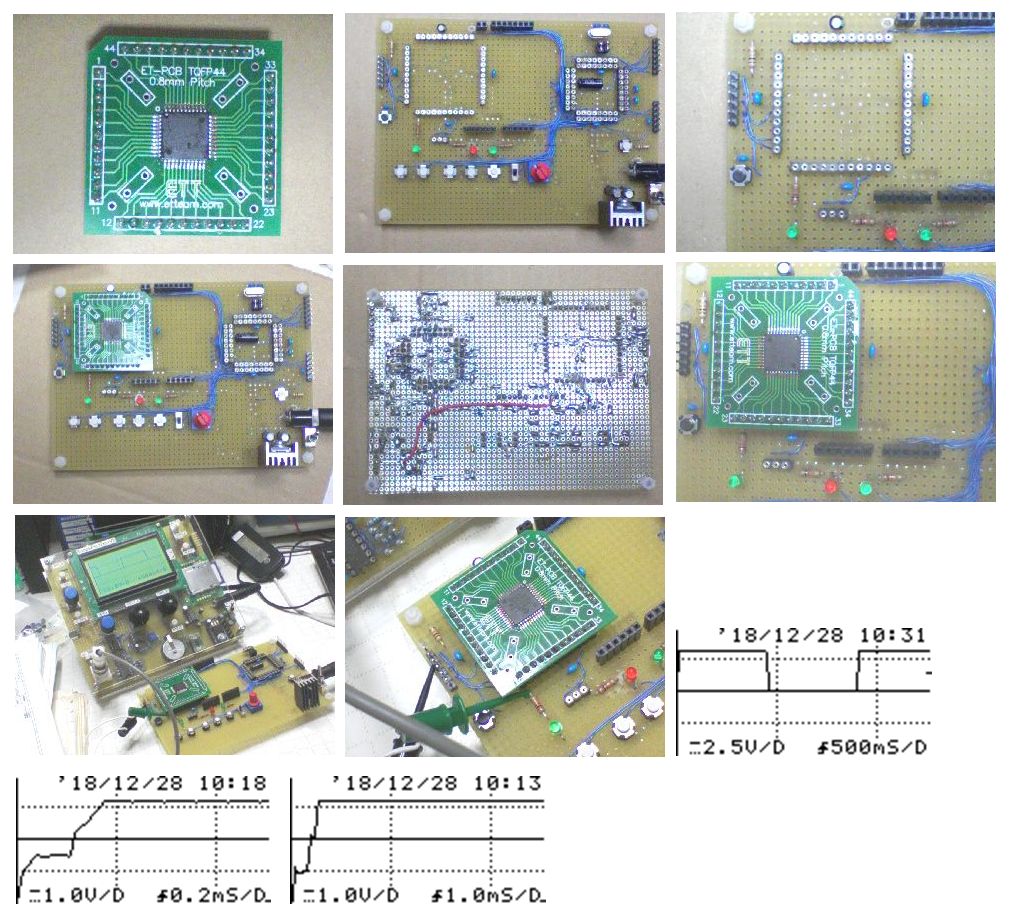

・PIC24FJ64GA004_POR_TESTプロジェクトを作成して調査した。

母体は、easy_fra_v4 プログラムのままで、POR不具合調査の為

プログラム頭に、1秒周期の、Lチカテストループを追加した。

テスト時、使ったプログラムです。→ PIC24FJ64GA004_POR_TEST.c

実験回路図です。→ PIC24FJ64GA004実験回路図

実験は、PIC32MX370Fトレーニング基板の、余スペースに、TQFP44-DIP変換基板を乗せ、それでチェックした。

・結果、実験セットでは正常動作した。

Lチカ時の、波形と、電源立上り波形も取りましたが、特に問題なさそうです。

PICのロット違いによるバグか、不具合の可能性があると考えられます。

今回のものに修正を加えるのは、TQFP取り外しの専用ハンダ吸い取り器等、専用工具がないので、パターンを

傷つける懸念もあるので、しないことにしました。

操作上は、P_ON直後に、RESET SWを押せば、特に問題ないので、そのまま使うことにしました。

ちなみに、正常動作した、PICのロット番号は、不具合と思われるPICと同じ、1620612だった。

ということは、ロット固有のバグではなさそうだ。

単なる不具合品かもしれない・・・

<回路図>

・こちらからどうぞ→ Easy_FRA_V4

回路図

<最終ソース・ヘッダファイル>

・こちらから、どうぞ:

/// メインソース

easy_fra_v4.c

easy_fra_v4a.c

:ソフト更新→ マルチ描画に対応しました。 200513更新

/// QVGAライブラリ(2018.10.29に行った、PIC24F用QVGAへ7SEG表示する実験の時の、ライブラリと同じです。)

colorlcd_libPIC24FVH_v2.c

colorlcd_libPIC24FVH_v2.h

///

アスキー文字フォント(2018.10.29に行った、PIC24F用QVGAへ7SEG表示する実験の時の、フォントと同じです。)

ASCII12dot.h

<メイン・フロー・チャート>

・こちらから、どうぞ→ easy_fra_v4_flowchart_181126

← 実験テーマ1に戻る TOP PAGEに戻る 実験テーマ112へ →