● 実験テーマ123

「PIC24FGCシリーズによる高速オシロの実験_5」

(Offsetポテンショを回していった時にZERO輝線と連動して動く「ZEROマーカー」を目指しての実験です)

■ 2020.5.17

・今迄で何台も自作実験してきたオシロには、市販のオシロにある「ZEROマーカー」の表示機能が無い。

Offsetポテンショを回していった時に、ZERO輝線と連動して動く「ZEROマーカー」だ。

これを何とか実現したい思いがずっとあったが、無くてもいいやという思いの方が強く半分あきらめていた。

今回実現すべく実験をする気になった。

(1)

大雑把に浮かんだ実現案

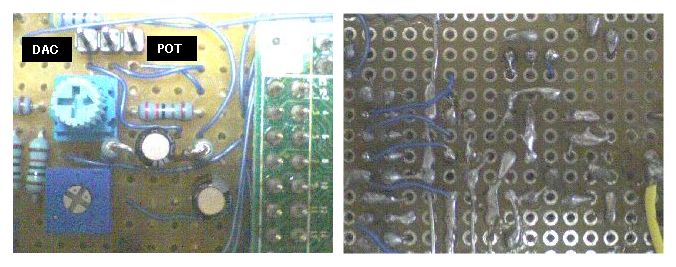

① ZEROシフト用に、PIC内蔵の、10bit DACを使う。

② ポテンショ(以後POTと表記)によるシフトでなく、ロータリエンコーダ(以後REと表記)によるシフトに変更。

(シフト電圧を、ADする方法だと、メインの信号電圧に対する変換にシフト電圧に対する変換が加わるので、F帯域が狭まるので却下)

③ 分解能は現存する、トリガレベルのそれと同じで良いと思う。

④ 波形描画更新インターバルの約0.05秒の間で、トリガレベル用の、REをリードしているが、ここにシフト用REの、リードを追加して、

ZEROレベル・マーカーを、表示画面左端に短いライン(緑)のマーカーを描画する。(トリガレベル・マーカーは、表示画面右端に短いライン(黄色)のマーカー)

・デバッグ(プロジェクト名「High_Speed_Oscillo_Test_6」)は、

ユニバーサル(以後UNVと表示)版の_V1オシロを以下の様に改造して行う。

① シフト源選択用のピンポストを立て、POT ⇔ REの、どちらかを選択出来るようにする。

② 追加のシフト用REポートとしては、RG2:A相/

RG3:B相を使用する。

3pinのピンヘッダに、この2本と、DGNDを引出し、REは外付けにて実験を行う。

③ とりあえずTest_6は、トリガレベルは、中央の、512固定とし、現トリガレベル用の、REをシフト用REにして実験することにした。

■ 2020.5.24

・ソフトを検討し始める。

<検討条件>

① DAC Vref= 2.4V(PIC内蔵基準電圧源:BGBUF0:1.2V x

2出力)使用

② DAC分解能= 10bit

③ ADC Vref= 3.3V(AVCC)

④ ADC分解能=

10bit(生データは12bitだが、QVGAの縦240dotに合わせ、10bitに間引いて格納している。)

<特記事項>

① DACと、QVGAの縦方向の分解能の関係で、ZEROマーカー位置の移動ステップを、±2.7と小数点計算をして、

intでキャストし整数ステップにしてみたが不安が残る。

いずれにしても近似的な位置になる。

(分解能不足で、1dot単位で移動は不可。約4dot単位になる見込み)

・一応、HEXは準備出来たので、ハード改造を行った。

・デバッグ開始

① 一応ZEROシフト・マーカー表示するが、位置関係が大幅にズレている。

DAC Vref= 2.4Vであれば、

DAC_CODE=704で、Vofs= (704/1024) x 2.4= 1.65V(AVCC=3.3Vの半分)になり中央になるはずが、

実測すると、Vofs= 1.57Vと低目になっているため、マーカーはセンター位置なのにオシロ入力:0Vで、輝線は、1/4ラインに位置している。

→ DAC Vref= 2.4V(PIC内蔵基準電圧源:BGBUF0:1.2V

x 2出力)の精度は仕様上どの位かデータシートの記載を調べてみた。

BGBUF0=1.2Vの精度(バラツキ)は、1.14Vmin~ 1.2Vtyp~

1.26Vmaxという事のようだ。

もしBGBUF0=1.14Vであるとすれば、Vref= 1.14 x 2= 2.28V

センターCODE= 704なので

Vofs= (704/1024) x 2.28V= 1.5675V

となる。

何か実測値にすごく近い!!

これが原因かも・・・

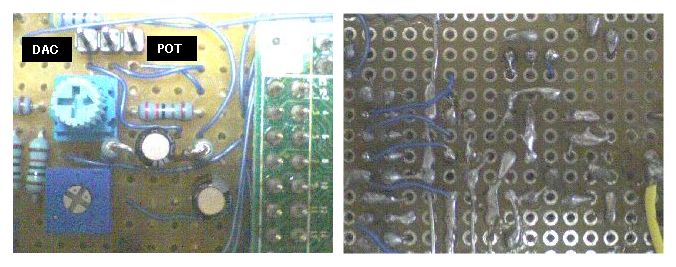

② あと、輝線に重畳するノイズが目立つ。

このノイズは、DAC特有のノイズと思われる。

→ 対策として、DAC出力に入っている、2.2kの後ろに、0.1uを、AGND間に追加してLPFとしたら、まあ良くなったのでこれで様子見とした。

■ 2020.5.25

・シフト電圧の移行は難しくないが、それに合わせマーカー位置を合わせるのは、画面の分解能からして難しい。

中央を、実測の、AVCC= 3.24Vと、BGBUF0:1.2Vのデータシート上の仕様の、下限:1.14V(現状追うと、どうもこの値付近になっている模様)

で考えると、DACの基準電圧としては、x2バッファ出力からのを使っているので、1.14V

x 2= 2.28V(仕様上:2.4Vtyp)となる。

これで、センター0の時の、Vofsを、1.62V(3.24V/2)とする為の、CODEを求めると次のようになる。

1.62V= (CODE/1024) x 2.28より

CODE= (1.62 x 1024)/2.28 = 728 となる。

※ DAC_Vref= 2.4Vtypの時の、センター位置時の、CODE=704に対し、+24の補正を掛けることになる。

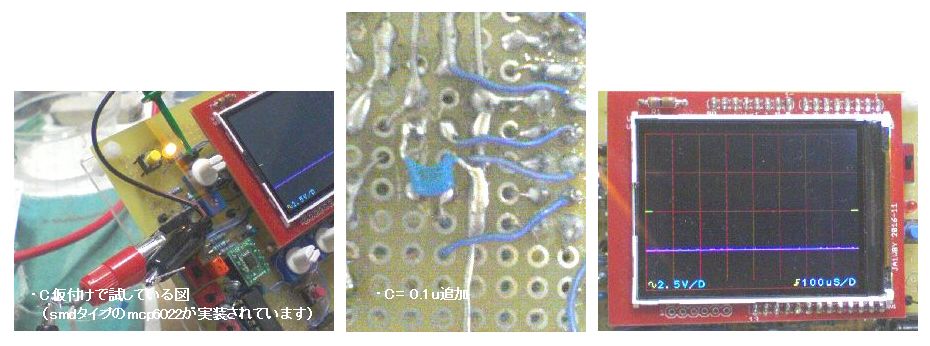

・実際やってみて、これでも合わなかったので、試行錯誤の結果、現状:725でセンターマーカーは合っている。

ところが上下移動共に、1/4ライン近辺がらズレが顕著になる。

んん・・・・・ なかなか手強い。

・またノイジーでライン描画が汚いのも気になっているが・・・・

LPFで少しは良くなったが・・・

・ADCの基準電圧源は、AVCCなので、オフセット印加に使っているDACの基準電圧も、AVCCに変更した方が共通に変動するので

回路としては安定するのでは?

それを明日以降試してみる。

■ 2020.5.27

・DAC・ADC共に基準電圧=AVCC=3.24V実測で考える。

・最初、DAC_CODE= 512としたが、P_ON時、ZEROマーカーに対し、ラインが数ドット下になってしまうので514に修正した。

これで、ロータリエンコーダの動きに対する、ラインの動きは、良くなったが、+側に飽和した状態で、-側に下げて行くと、

マーカーの方が途中からラインと合わなくなる。(数ドット下になる)

・また、DACでオフセットを与える方法だと、POTのそれと比較して、輝線(ライン)に重畳するノイズが若干多くなる。

DACノイズだと思うが・・・・

DACの出力(2.2Kの先)に追加した、0.1uを、47uに増やしてみたが、未だちょっとハイレンジで気になる。

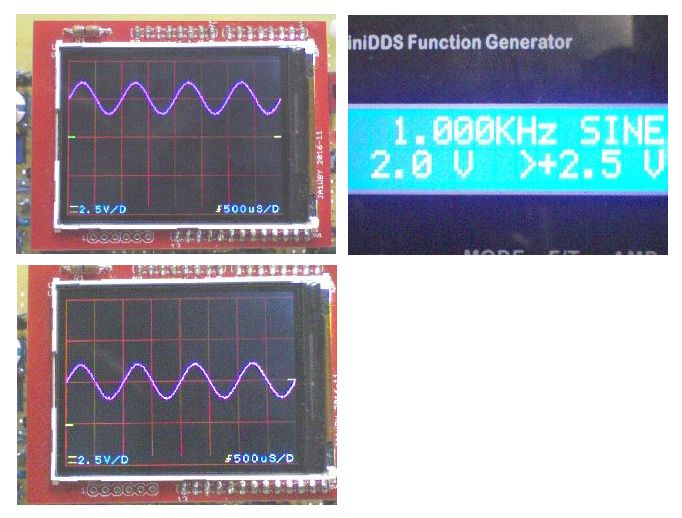

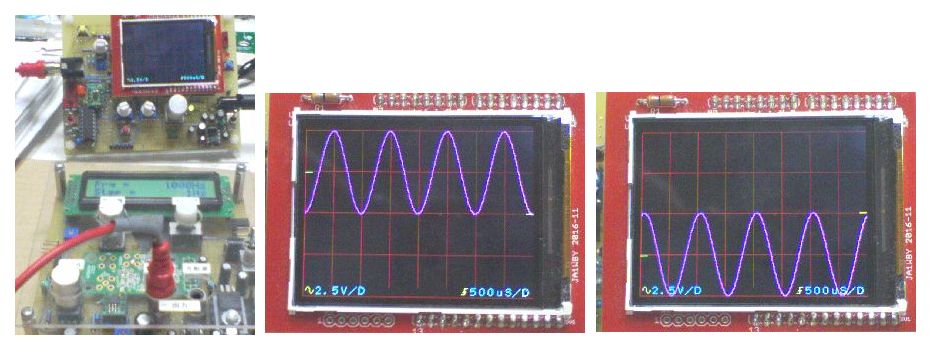

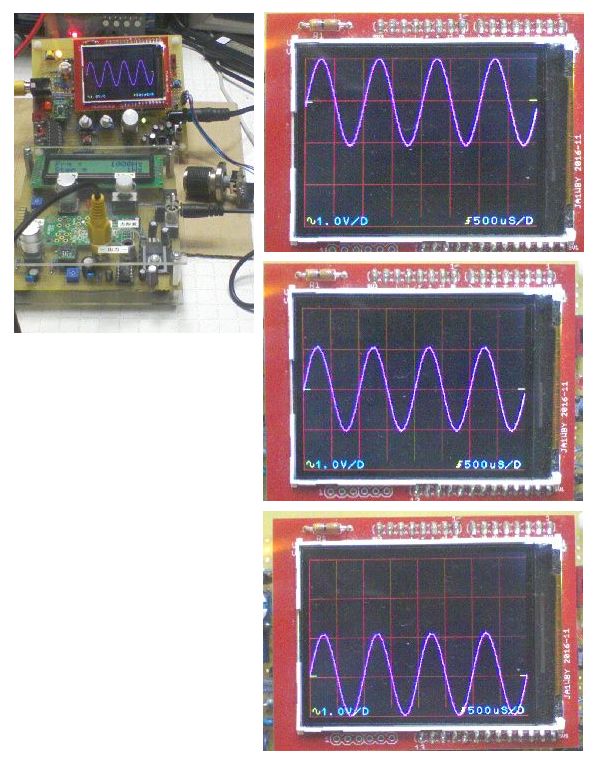

・今日は、FG805からオフセット付のサイン波を入力して、ZEROレベルマーカーの有効性が分かるサンプルをとってみた。

ただ中華製のこのFGはノイズが多い。

なので、自作のDDSオシレータでもサンプルを取ってみた。

■ 2020.5.28

・昨日の症状整理

Vofsのシフト、+領域、-領域とも問題無い模様。

ただ、ZEROマーカーの動きが怪しい。

① -領域は、OK

-飽和させて、+方向へ戻して行っても問題無く、マーカーはズレることなく追いついてくる。

② +領域は、NG

+飽和させて、-方向へ戻して行くと、輝線の位置とマーカーが合わなくなる。(輝線に対し、2~3dot下になる。)

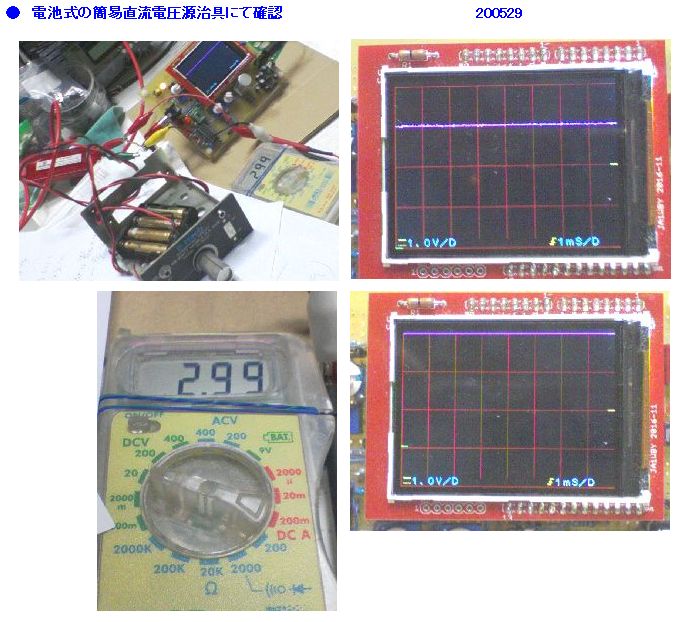

■ 2020.5.29

・何とか無理やり?だが+領域も、OKになる。

上限を判定する、DAC_CODEを、544にしないで一つ手前の、543にして、543以上だったら543にリミットするようにしたら上手く行く。

・あと-領域だが、下限一杯でも若干(2dot位)最下位ラインより上になるので、下限判定のDAC_CODE=

484を、483にしてみた。

これでOKになる。

・移動して行くと、センターの所で、マーカーが、1dotズレてくるので、移動後のDAC_CODEがセンターの514になったら、

強制的に、Ypos= 116に補正してみた。

これで良くなる。

・これで、Test_6プロジェクトはクローズ。

■ 2020.5.31

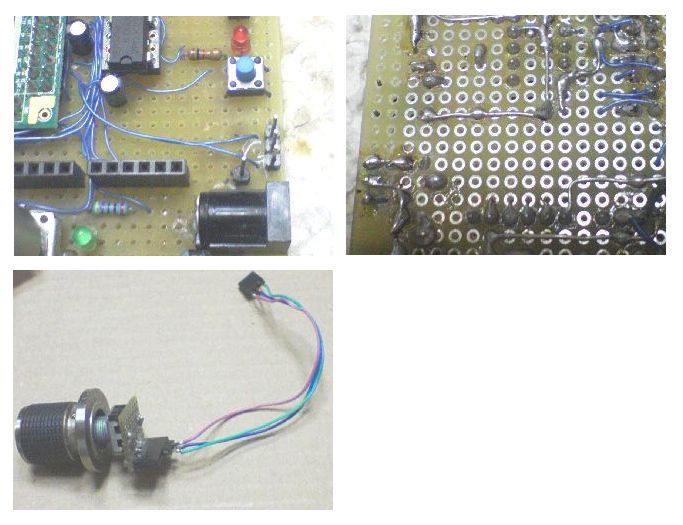

・Test_7プロジェクトに移行

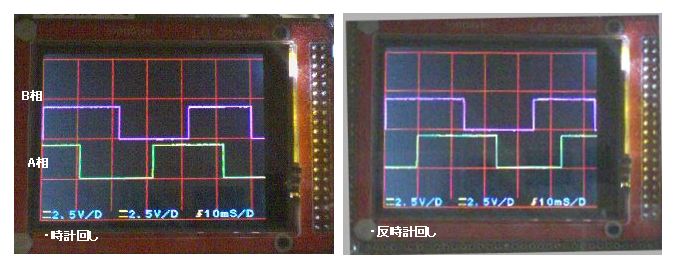

TRIG. LEVEL REとは別に、ZEROシフトREを、RGポート(RG2:A相/RG3:B相)に追加して実験

・ソース~ HEXまで準備出来た。

また追加の改造も済んだ。

・デバッグ開始

まずは駄目。

TRIG. LEVEL REはOKだが、ZEROシフト REはNG

① イニシャル位置中央は、両者共にOK

② REとPICピン間の配線はOKを確認

③ プルアップは、A相ピン・B相ピンともにされていることを確認

REを回すと、Hi⇔Lowに変化する。

■ 2020.6.1

・続デバッグ

今

///

ロータリエンコーダ読込み(波形描画更新インターバル:約0.05秒も兼ねている)

for(i= 0; i < 50; ++i){

Delayms(1);

RotaryEncoderRead(); // ロータリエンコーダ読込み(TRIG_LEVEL)

ZeroRotaryEncoderRead(); // ロータリエンコーダ読込み(ZEROシフト)

}

としているが、TRIG. LEVEL REのところをコメントアウトにして、ZEROレベル

REだけにしても駄目。

この状態で、自作2現象オシロで、ZEROレベル REの、A相・B相のタイミングとレベルを確認したが問題なかった。

(プルアップはPIC内部の弱プルアップなので、低目であるが、許容範囲内)

だけどB相のネガティブ・エッジセンスしない?

→ 色々調べた結果、このRGポートは、USBポート(D+,

D-)との共用ピンとなっていて

単純ポートとして使うには、特別な設定が必要なことが判明した。

以下のような設定記述が必要。

↓

/// USBピン:RG2/D+, RG3/D-を単純入出力ピンとして使う設定

U1CNFG2bits.UTRDIS = 1; // UTRDIS:USB On-Chip Transcever

Disable bit

これを追加したら動き出した。

■ 2020.6.3

・大方OKなのだが、よく使う、1/4ラインと、3/4ラインのところで未だ、1~2dotではあるが

僅かにマーカー位置がズレるのが気になる。

このラインへは最低限確実に合わせておきたいものだ。

そこで、現状妥協レベルではあるがOKになっているソース:200527版での

表示dotと、Yposとの関係を今一度、考察してみた。

以下のような関係になっている。

QVGA表示上の1目盛当たりの電圧幅=

3.24V/58= 0.81Vなので、

細かい1目盛の電圧幅= 0.81/58=0.014V

一方、Vadc(DACによるVofsと入力信号の加算OPアンプ出力点の電圧=ADC入力電圧)は、

DACの分解能不足でDAC_CODEを+1する度に、0.05Vと粗くしか変化しないので、

マーカーをQVGA LCD上の、1dot単位で移動することが出来ない。

そこで最低限、中央・4分の3・4分の1ライン・max・minラインには極力合わせられるように

マーカー移動位置は、センターを基準にYpos ± 4毎に移動することにした。

・現状これでも若干ズレるので、4分の1ラインのところと4分の3ラインのところで中央位置と同じ考えで

強制的に補正を追加した。

これで見た目ズレは無くなった。

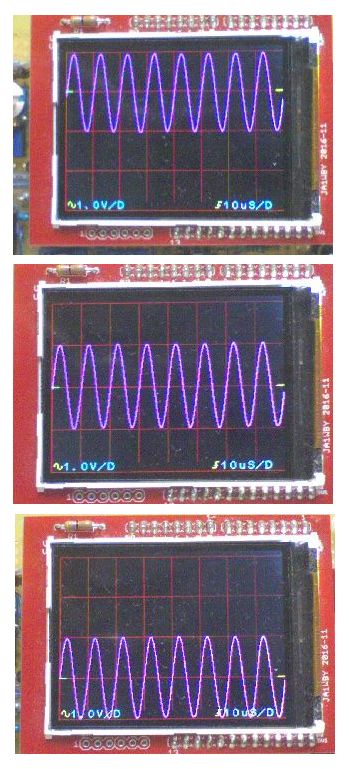

・残る気になる点としては、ハイレンジ:10uS/Dで比較的遅い信号を観測した時、輝線に重畳するノイズ(誘導ノイズ)がまだ若干

目立って見える点だが、UNV版で実験しているので、たぶんGNDの引き回しの問題も、あろうかと推測している。

実験レベルなので、これは妥協してOKとした。

今後、これをP板に反映(_V2 P板の改版V3)しようと考えているので、その時また考えることにした。

<回路図>

・こちらからどうぞ→ 「PIC24F_GC_高速オシロ実験6_7回路図」

<最終ソース>

・こちらから、どうぞ→ High_Speed_Oscillo_Test_6.c

High_Speed_Oscillo_Test_7.c

※ この他に、QVGA液晶ライブラリと、フォントデータ(ヘッダファイル)が必要ですが、

それは、テーマ72のと同様なので、そちらを参照してください。