���@�����e�[�}74

�uPIC24F_GC�V���[�Y�ɂ��A�����I�V���̎���_3�v

�i����_2�̕��H������ATT��H�ł͓��͗e�ʂ̉e���ō��悪�ቺ����B���P����ATT��H�̎��������Ă݂܂����B�j

���@161115�F

���@���m�N���E�I�V���ɔ�r���āA�J���[�E�I�V���̉t����ʂ̃`���c�L���������̂ƁA

�@�@ ��ʍX�V�Ԋu�������i1�b�j���A�\�t�g�X�V�ɂ��A���P���Ă݂܂����B

�@�@ �v���W�F�N�g���F�uHigh_Speed_Oscillo_Test_5�v�Ƃ��܂����B

�@�@ �ڍׂ́A2016.11.11����̋L�����Q�Ƃ��Ă��������B

�@

�ȉ��A���̎����̓^���L�ł��B

���@2016.1.9

�@�@�E�O���画���Ă������Ƃ����A�����̎���I�V���ō̗p���Ă����ȈՓI�ȁA1M���C���s�[�_���X��

�@�@�@����ATT��H�́A������H���ȗ�����Ă���̂ŁA�X���[�ȊO�̓d�������W�ł́A

�@�@�@���͗e�ʂ̉e�����ł������惌�x�����ቺ����B

�@�@�@��̓I�ɂǂ̈ʒቺ���邩���A����I�V��V4�̎��ɁA����AC�d���v�Ńf�[�^����������Ƃ�����B

�@�@�@�A���AHP�ɂ͌��J�͂��ĂȂ��B

�@�@�@����͉��ɂ��A�����I�V���̎����Ƃ������Ƃ�����A100kHz�ɉ����ă��x�����ቺ����̂����Ƃ�

�@�@�@�������Ƃ����C�����������Ȃ����B

�@�@�@�X���[�ȊO�̓d�������W�ŁA100kHz�ɉ��������x���ቺ������ATT��H�������Ȃ�ɖڎw�������Ǝv���B�@�@�@

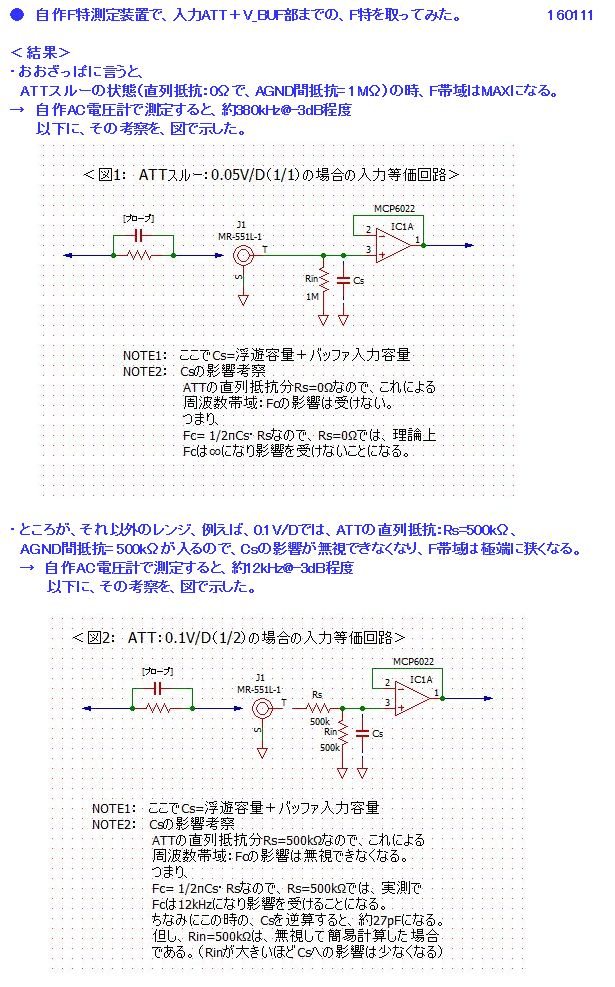

���@2016.1.11

�@�@�E�������������e�[�}71�ō�����u�Ȉ�F���������葕�u�v������̂ŁA����Ō����ATT��H��

�@�@�@F���𑪒肵�Ă݂悤�ƍl�����B

�@�@�@�ȈՓI�ȑ��u�Ȃ̂ŁA����ɂ�������H�͏ȗ����Ă���̂ŁA����̎�_�͂��邪�i����ǎ����邩���E�E�j

�@�@�@�e�����W�̑��Δ�r�Ɏg���ɂ͖��Ȃ��B

�@�@�@���@�ȉ��ɂ��̌��ʂƎ����Ȃ�̍l�@���A�b�v���܂����̂ŎQ�Ƃ��Ă��������B

���@2016.1.12

�@�@�E�s�̃I�V���̓��͉�H�̒�Ƃ��āA����ATT�̒�R�ƃp���ɁA�ш��p��C�����邱�Ƃ�

�@�@�@�m������B

�@�@�@����������̑����̃����W�ɑ���𐳂����|����萔��v����Z�ʂ��m�E�n�E�������ĂȂ�

�@�@�@���A�o�����Ƃ��Ă������̃X�y�[�X���������ʓ|�Ȃ̂ł�肽���Ȃ��B

�@�@�@���������ȒP�ɏo���Ȃ����̂��H

�@�@�@WEB���������Ă��A���̕ӂ��ڂ���������Ă�T�C�g�͖��������B

�@�@�@�����ň����Ȓ��I�V���̓���ATT��H�ׂĂ݂��B

�@�@�@�����e�[�}45�Ő��삵���������I�V���E�L�b�g�i06204KPL�j��pdf��H�}�ł���B

�@�@�@���I�V���ł́A2�i�\����ATT�\���ɂȂ��Ă��B

�@�@�@1�i�ڂł́A1/1�ƁA1/10���X���C�hSW�Őؑւ���悤�ɂȂ��Ă��āA1/10���ɁA�

�@�@�@�́A1pF�ƁACx������悤�ɂȂ��Ă���B�i�����A��H�}��́ACx�̓m���E�}�E���g�ɂȂ��Ă����B�j

�@�@�@1�i�ڂ̓d���o�b�t�@�A���v�ŃC���s�[�_���X����������ɁA2�i�ڂ�ATT�ɐڑ����Ă���B

�@�@�@�����2�i�ڂ�ATT��R�͋ɒ[�ɒႢ��R�l�i249��+150��+100���j���g���Ă���B

�@�@�@����ȂɒႢ��R���g���̂͂��Ԃ�m�C�Y�Ǝv���邪�A�d�����H�����A�I�y�A���v�̎���

�@�@�@�萔�Ƃ��Ă͈�ʓI�ł͂Ȃ��B

�@�@�@�������A���̉�H�̑_���͉���B

�@�@�@�ш��́A���͗e�ʂ̉e������n�C�E�C���s�[�_���X��1�i�ڂ݂̂ōs���A�o�b�t�@�ɂ�

�@�@�@�C���s�[�_���X����������ɁA�Ⴂ��R�l��2�i�ڂ�ATT�Ƃ���A�e�����W�̕�͕K�v�Ȃ��Ȃ�

�@�@�@1�i�ڂ�1/10���̕�����ōςށB

�@�@�@���R�A�����W�́A1,2�iATTT�̑g�����ɂ͂Ȃ邪�B����͂��قǖ��ł͂Ȃ��B

�@�@�@��������ATT��H���l���邱�Ƃɂ����B

�@�@�@���I�V���ł́A2��ATT�̐ؑւ����A2�̃X���C�hSW�ōs���Ă���B

�@�@�@���[�h�A�E�g���K�v�Ȃ̂ŁA���_�o�̗͂L�����ȁA8�s���̃X���C�hSW���g���Ă���B

�@�@�@�������ɁA���̒ʂ�ɂ͂������Ȃ��B

�@�@�@�ŏ��͍����ʂ�A1�̃��[�^���E�f�B�b�vSW�Őؑւ��邱�Ƃ��l�������A�A�i���OSW��2�A

�@�@�@���́A�����[�ƃA�i���OSW�̑g�������K�v�ƂȂ��A1�ӏ��ŁA2�̐ؑւ��f�q�̃R���g���[��

�@�@�@���K�v�ƂȂ邽�߁A���[�^���E�f�B�b�vSW�i�d�������W�j�̓Ǎ��݂ƁA�ؑփp�^�[���̏o�͂�

�@�@�@�ʃ|�[�g�ŃR���g���[�����Ȃ��Ƃ����Ȃ��̂ʼn����̎�Ԃ̂��Ƃ��l���Ă���͋p�������B

���@2016.1.13

�@�@�E���낢�댟���������ʁA���I�V���̓��͉�H�ƈقȂ镔���͈ȉ��̒ʂ�ƂȂ����B�@�@

�@�@�@�@�@1�i�ڂ�ATT�ؑւ́A2��H2�ړ_�̃X���C�hSW�ɂ��A2�i�ڂ�ATT�ؑւ́A�����

�@�@�@�@�@ ���[�^���E�f�B�b�vSW�{�A�i���OSW�i4��1*2��H�i1��H�̂ݎg�p�j�F74HC4052�j�ōs���B

�@�@�@�@�@ �iMPU�̓��[�h�A�E�g�����s���B�j

�@�@�@�A�@2�i�ڂ�ATT��R�͋ɒ[�ɒႢ��R�l�łȂ��A�g�[�^����10K�ɐݒ肵���B

�@�@�@�B�@ATT�ȍ~�̃A���v��H�̈Ⴂ����A2�i�ڂ̒�RATT�̌�ɂ��A�d���o�b�t�@����ꂽ�B

�@�@�@�@�@ �i����Ă��AIC�̐��͑����Ȃ��j

�@�@�@�@�@ ���Ȃ݂ɁA���I�V���́A2�i�ڂ̃A���v�͔]�A���v�ɂȂ��Ă���B

�@�@�@�C�@������A���v�\���̈Ⴂ����Ȃ̂����A���I�V���́A�Œ���W���A0.1V�Ƃ��A

�@�@�@�@�@ 1�i�ڂ�1/1��1/10�̐ؑւ��ƁA2�i�ڂ�1/1�A1/2, 1/5�̐ؑւ��̑g������

�@�@�@�@�@ 0.1V�` 5V�܂ł́A�S6�����W�i2*3�j�Ƃ��Ă��邪�A

�@�@�@�@�@ ���́A�Œ���W���A0.05V�Ƃ��Č�i�A���v�̃Q�C���ݒ�����Ă���̂ŁA

�@�@�@�@�@ ATT�̑g�����i���[�^���E�f�B�b�vSW�̕��́A'0'�`'3'�i1/1,

1/2, 1/5, 1/10)�܂ł̐ݒ�Ƃ����B�j

�@�@�@�@�@ �͓��������A0.05V�`�@5V�܂ł̑S7�����W�i2*4��8�ʂ�ɂȂ邪�A0.05V����X�^�[�g���Ă���

�@�@�@�@�@ �̂ŁA1/1*1/10�i'3'�j=0.5V�����W�ƁA1/10*1/1�i'0'�j=0.5V�����W���_�u���̂�7�ʂ�ɂȂ�B�j

�@�@�@�@�@ �Ƃ����B

�@�@�@�@�@

���̕ӂ͕��͂������Ɖ���ɂ����̂ŁA���̃y�[�W�����ɓY�t�̍ŏI��H�}�ɁA

�@�@�@�@�@ ATT�ؑփe�[�u���\��Y�t�����̂ʼn�H�}�ƂƂ��ɎQ�Ƃ��Ē�����Ǝv���܂��B

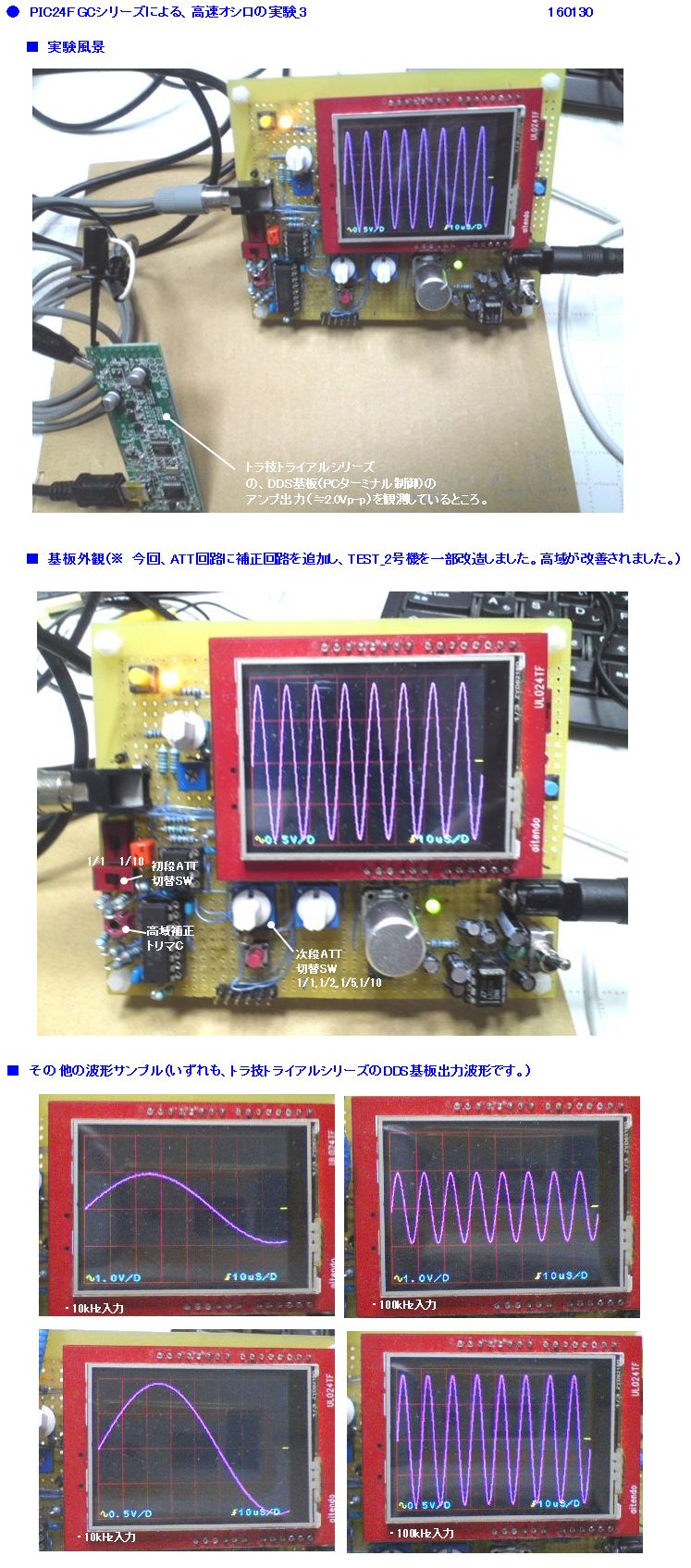

�@�@�@�D�@��p�̃g���}C�́A���萫�̂悢20p�i�ԁj�̂��̂��g�����Ƃɂ����B

�@�@���@ATT�������H�́A����ł��B���@�u�����I�V���p����ATT������H�v

�@�@�E���ꂩ��̎����̐i�ߕ������A�ŏ��́A���̕��������̎������g��ŁA��H�̓���m�F

�@�@�@���s���A�ǂ��ƂȂ�����A���̊��ATT�o�͂��ATEST_2���@�̃o�b�t�@�ȍ~�̃A���v�ɓ��͂���

�@�@�@�\���m�F���s�����Ƃɂ����B

�@�@�@���̌�ATEST_2�̉����`�@����m�F�Ƃ�������ɂ������B

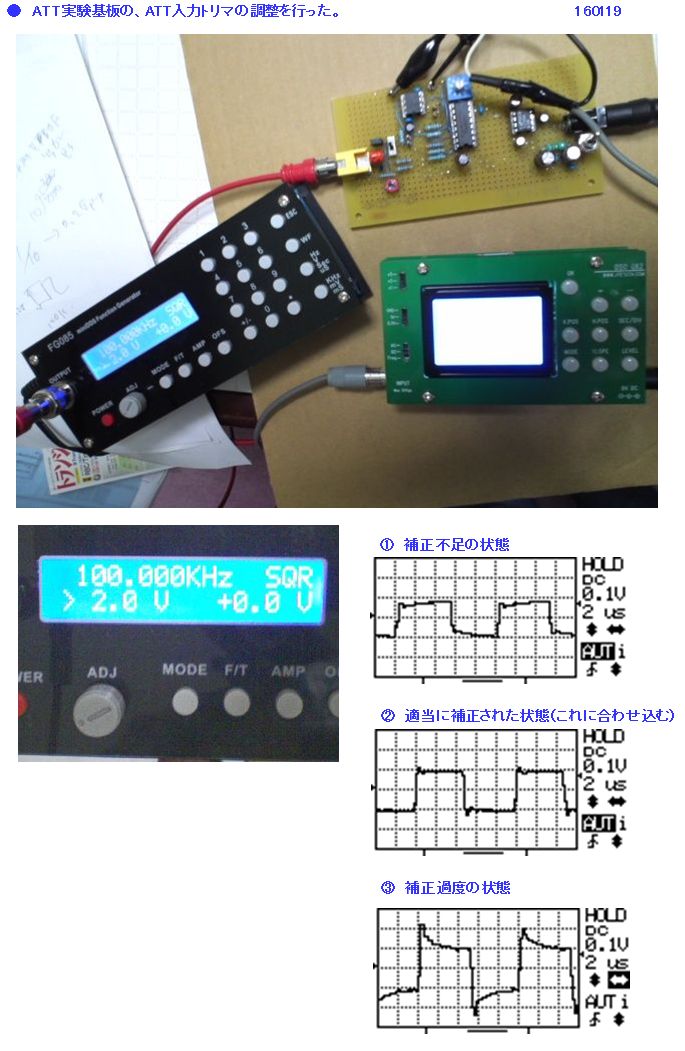

���@2016.1.19

�@�@�EATT������̐��삪�ςB

�@�@�@�`�F�b�N�ɓ���B

�@�@�@�@�@�@�d�����@+5V=5.22V, -5V=-5.04V

�@�@�@�@�A�@ATT�i1/10�j���͂́A�����g���}�̒����������Ă݂��B

�@�@�@�@�@�@

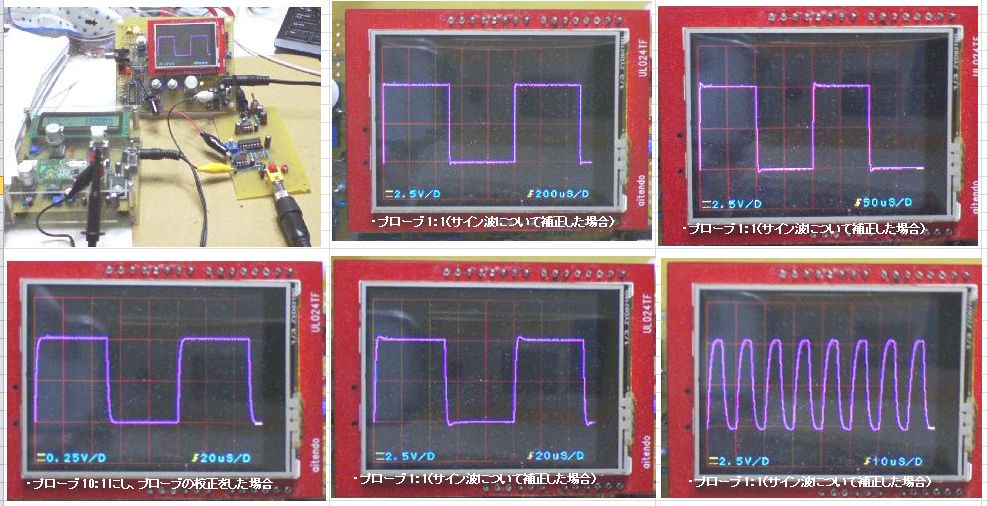

�ŏ��́A��ʓI�ɒm���Ă���A���`�g����͂��āAATT�o�͂��m�F���A���̕��`�g�̃t�H�[��

�@�@�@�@�@�@

�����āA�A���_�[�y�уI�[�o�[�V���[�g���Ȃ����x���܂ō��킹���ޕ��@��������B

�@�@�@�@�@�@ �܂��悭���A10:1�v���[�u�̍Z���Ɠ����ł���B

�@�@�@�@�@�@ ���iATT���A1/10�A���iATT���A1/1�ɂ��āA���͂ɁA100kHz,

2V�̕��`�g����́B

�@�@�@�@�@�@ ���̏�ԂŁAATT�o�́i���i�j���ϑ����A�����g���}���āA�K���ɕ���|�������

�@�@�@�@�@�@

�i�A���_�[�y�уI�[�o�[�V���[�g���Ȃ���ԁj�܂ō��킹���ށB

�@�@�@�@�@�@ �������A�o�̓��x���́A0.2V�ɂȂ�B

�@�@�@�@���@����͏�肭�s�����B

�@�@�@�@�@�@ �ȉ��ɂ��̎��̗l�q�ƌ��ʂ��������B

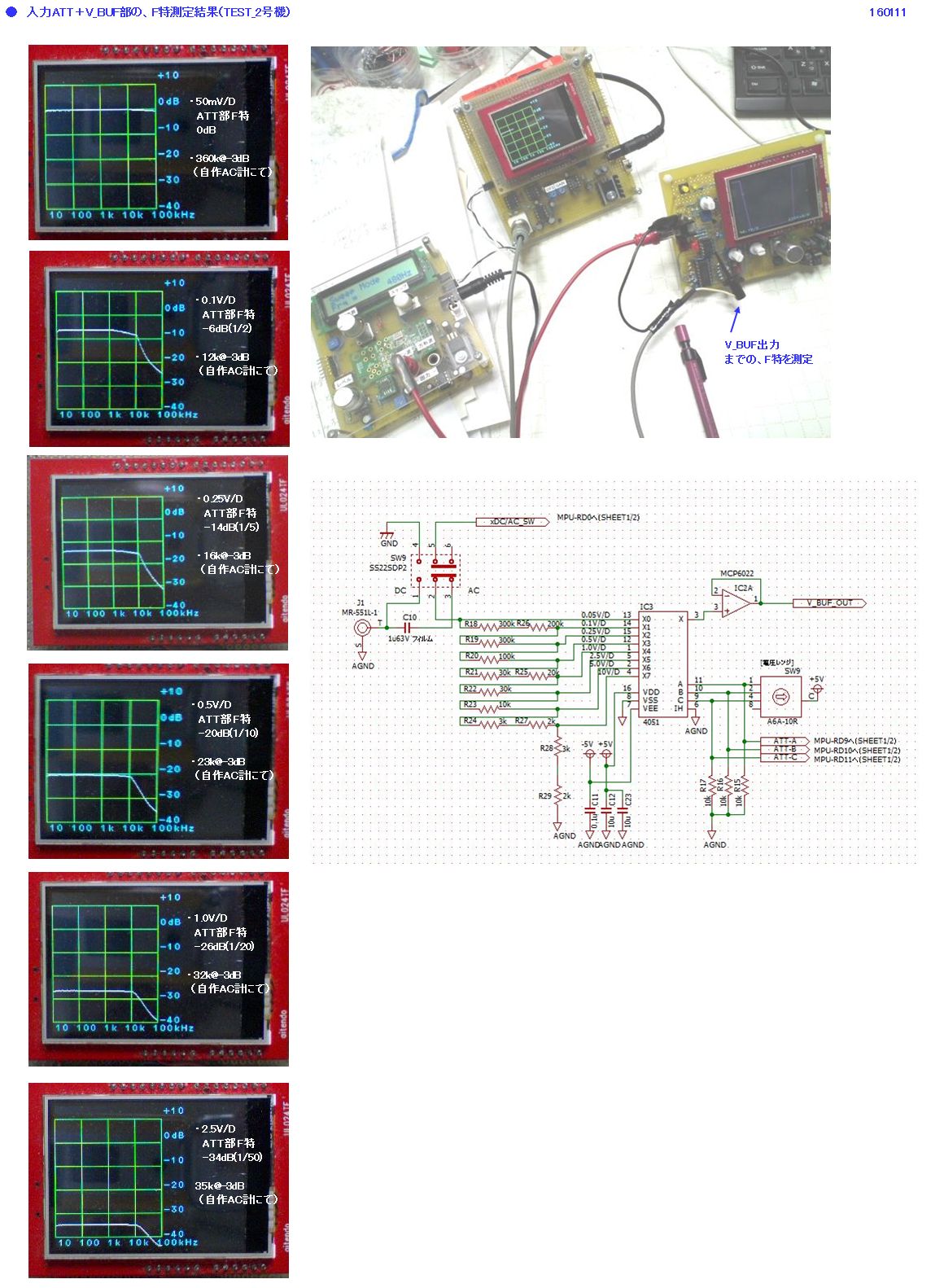

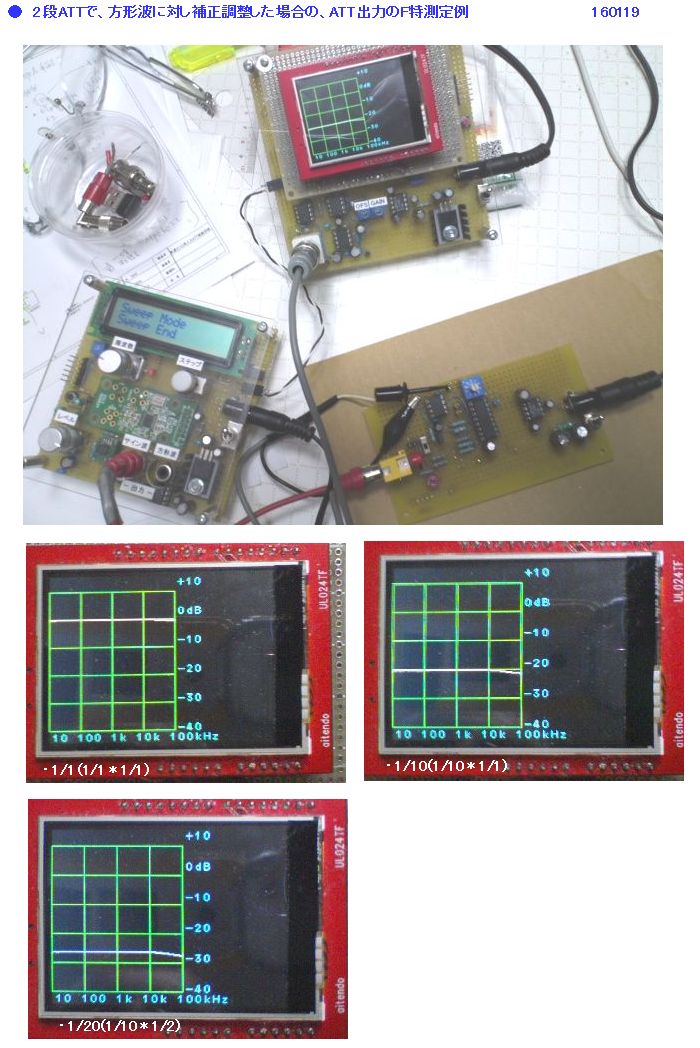

�@�@�EATT�o�́i���i�d���o�b�t�@�o�́j�ɂāA�e�d�������W�ɉ�����AF���𑪒肵���ꕔ�̗���ȉ��Ɏ����B

�@�@���㌋�ʂ�������܂��B��

�@�@�@�@�@ATT�X���[�́A0.05V/D�i1/1�j�̎��̓����́A100kHz�܂łقڃt���b�g�B

�@�@�@�@�@ �ׂ��������A100kHz�ŁA-0.5dB�قlj������Ă���B

�@�@�@�A�@�����A�����W��ؑւ����Ă������ꍇ�́A��1kHz����̌����i10kHz���猰���ɂȂ�j�́A�w�ǖ����Ȃ����B

�@�@�@�@�@ (���R�A�S��Zin= 1M���ɂāj

�@�@�@�@�@ �܂��A�X���[�ł��A100kHz�ŁA-0.5dB�قlj������Ă���̂ŁA���̉e���͊e�����W�ɐؑւ����Ă������ꍇ

�@�@�@�@�@ �����R�c��B�iMAX100kHz�ŁA-1.0dB�قǁj

�@�@�@�B�@���i�d���o�b�t�@�̓���10k���V���[�g�����ꍇ�ƁA�V���[�g���Ȃ��ꍇ�����������A�����ɕω��͖��������B

�@�@�@�@�@ ���͕ی�ƃ_���s���OR�̈Ӗ��œ���Ă������Ƃɂ����B

�@�@�@�C�@�S�z�������}5V�d���R���f�B�V���������A5.22V,

-5.04V�Ǝv������艺�����Ă��Ȃ������B

�@�@�@�@�@ �܂��AATT�o�͂��I�V���Ŋϑ��������A�m�C�Y�͏d�ĂȂ������B

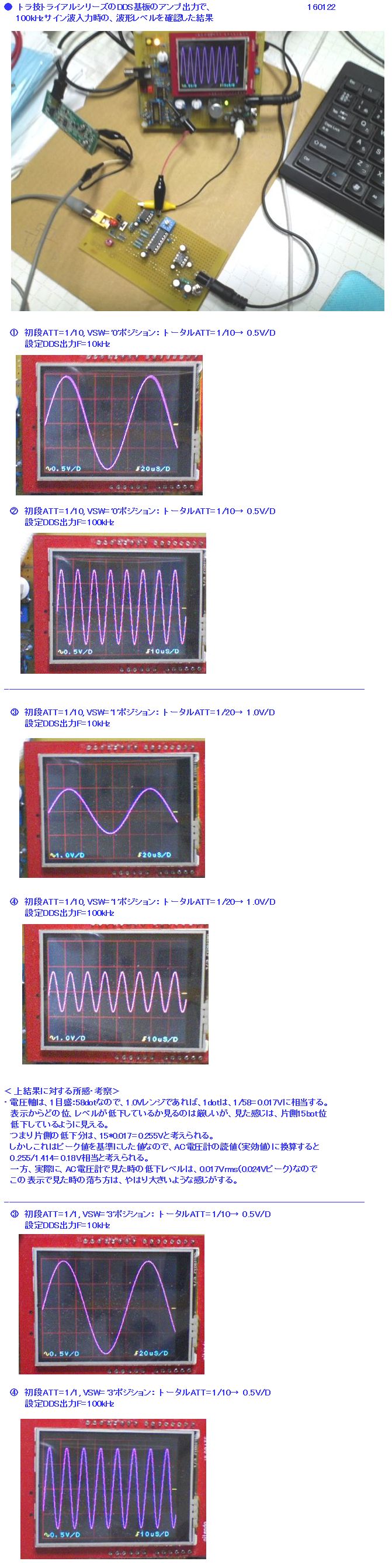

���@2016.1.22

�@�@�E����őË��Ƃ��l�������A�܂��A������������ꍇ�ł��A��ł͂��邪�A100kHz�ɉ����郌�x�����ቺ���Ă���

�@�@�@�̂��C�ɂȂ�B

�@�@�@���̒i�K�ł́A���̎�����̏o�͂��ATEST_2���@�̓d���o�b�t�@�ȍ~�̃A���v���͂ɐڑ����āA���ۂ�

�@�@�@�g�`�\�������Ă݂�킯�����A���̎��ɂ́A�����������x�̗ǂ����U�\�[�X���g���Ă���Ă݂邱�Ƃɂ����B

�@�@�@���̑O�ɁA�����g���Ă�������DDS OSC�́A100kHz�ɉ����郌�x���ƁA���x���ǂ��Ǝv����A�g���Z�g���C�A��

�@�@�@�V���[�Y��100kHz�ɉ����郌�x�����A��r�I�M���̂����鎩��AC���x�����[�^�i�{����1�䂭�炢�s�̂́A

�@�@�@���x�̗ǂ�AC���x�����[�^���~�����̂����E�E�E�j�Ŋm�F���Ă݂邱�Ƃɂ����B

�@�@�@���̌��ʁA����DDS OSC�́A100kHz�ɉ����郌�x���́A��0.96V�i-0.35dB

�A���A1V= 0dB�Ƃ��āj

�@�@�@����A�g���Z�g���C�A���V���[�Y��DDS��́A100kHz�ɉ����郌�x���́A-0.15dB�قǂ��������Ă�

�@�@�@���Ƃ��m�F�����B

�@�@�@����́A1V= 0dB�Ƃ��ċt�Z����ƁA0.983V�ł���B

�@�@�@�i�����ɓ������ẮA�g���ZDDS��̃A���v�o�͂́A��2Vp-p�Œ�Ȃ̂ŁA���������AC�d���v�ɂ�

�@�@�@�m�F�B���@1kHz�ɂ�0.65Vrms�ŁA100kHz�ł�0.639Vrms�i-0.15dB�j�ł������B�j

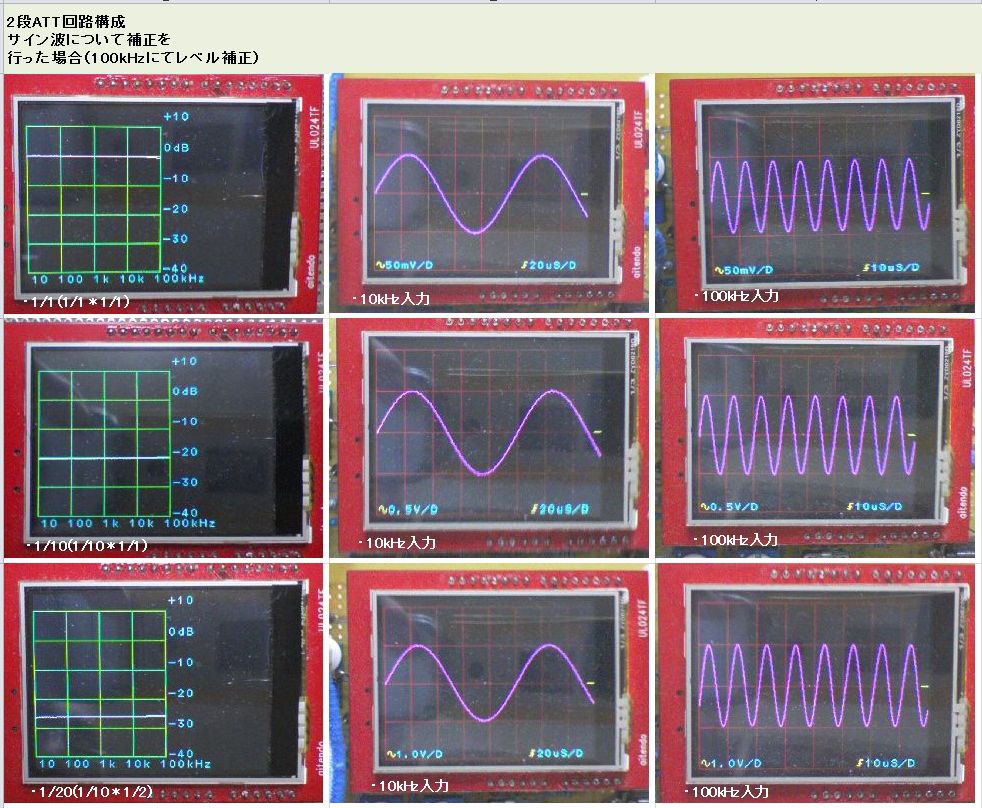

�@�@�@�ȉ��ɁA�g���ZDDS��̃A���v�o�͂��AATT���������A���̏o�͂�TEST_2���@�́A�o�b�t�@�o�͈ȍ~

�@�@�@�̃A���v���͂ɐڑ����āA�g�`�\�������A���̕\���Ń��x���ቺ�x�����m�F���Ă݂����ʂ������B

�@�@�@�l�@�R�����g�ɂ�����ʂ�A���x�̗ǂ�OSC�̏o�͂Ō��Ă��A�\�������g�`����ǂݎ�������x���́A�Ⴂ

�@�@�@�悤�ł���B

���@2016.1.27

�@�@�E��ȊO�ōl�����邱�Ƃ́A�o�b�t�@�A���v���A����ɑш�̍L�����̂Ɍ������Ă݂�

�@�@�@���Ƃ����A���s��MCP6022�i�ш�10M�j�́A5V�Ŏg�����ꍇ�̃t���X�C���O�ш�́A�f�[�^�V�[�g

�@�@�@�ɃO���t�ōڂ��Ă���A400k�܂ł̓t���b�g�ł���B

�@�@�@���Ƃ��ƁA1.5�`3M�ш�̃I�y�A���v�ł͑ш���\���L���ł��Ȃ������̂ł�����̗p���Ă���o��

�@�@�@������A����̓I�y�A���v�Ɋւ��Ă͂��̂܂܂ōs�����Ƃɂ����B�i�����̂���ǎ����邩���H�j

�@�@�@���ǁA����͕�̕��@�œ����邱�Ƃɂ����B�i�܂�́A�T�C���g�ɂ��ĕ����������@�ɂȂ�B�j

�@�@�@�ȉ��̎菇�ł���B

�@�@�@�@�@�@�܂��́A���`�g���͂ŕ�i�A���_�[�E�I�[�o�[�V���[�g���������x���ɍ��킹��j��������B

�@�@�@�@�A�@���ꂾ���ł́A�����T�C���g���͂������A100k�Ń��x������ቺ����̂ŁA�ēx�g���}��

�@�@�@�@�@�@

�āA���x������グ�A�t���b�g�ȓ����ɂȂ�悤�ɂ���B

�@�@�@�@�B�@�����ŁA���͂���`�g�ɖ߂��A�ڗ����ăI�[�o�[�V���[�g�E�A���_�[�V���[�g���Ȃ����m�F����B

�@�@�@���̂悤�ɍ��킹�Ă��A�B���I�[�o�[�V���[�g�E�A���_�[�V���[�g�͖w�NjC�ɂȂ�Ȃ����x�������̂�

�@�@�@����͂���őË����邱�Ƃɂ����B

�@�@�@�������`�g�̃t�H�[�����܂Ƃ��ɕ]������悤�ȏꍇ�́A�I�V���̃v���[�u���A10�F1�ɂ��āA�����

�@�@�@�I�V���v���[�u�̕�g���}�����Y��ɕ�ł���̂ŁA���̂悤�Ɏg���悢���Ǝv���B

�@�@�@�ǂ����Ă��悤�Ȍ��ۂɂȂ�̂��s���ʼn���Ȃ����A���͂����v���Ă���B

�@�@�@���`�g�́A�����in���j�T�C���g���ɍ����������́i�܂薳���̍����g���܂ށj�ƍl������B

�@�@�@����ɑ��ĕ���|�����ꍇ�ƁA�P��̃T�C���g�ɑ��Ċ|�����ꍇ�Ƃł́A���`�g�܂�

�@�@�@n���T�C���g�̍����ɑ��Ċ|�����ꍇ�̕����A���V�r�A�Ȃ悤�Ȋ���������B

�@�@�@���̕ӂ��W���Ă���̂��ȂƂ�����Ɏv���Ă���B

�@�@�@���`�g�̕�ŁA�T�C���g���͂̏ꍇ���ш���m�ۂł���悤�ɂ���ɂ́A����ɓ��͉�H��

�@�@�@�����\�Ȃ��́i�f�B�X�N���[�g�iFET�j��OP�A���v�̑O�i�o�b�t�@��g�ނƂ��E�E�E�j�ɂ��Ȃ��ƑʖڂȂ̂���

�@�@�@����Ȃ��E�E�E

�@�@ �ȉ��ɁA�T�C���g�ɂ��ĕ���s�����ꍇ�́AATT��H��F���̗�ƁA�T�C���g�E���`�g���͂����ꍇ

�@�@�@�̔g�`�T���v�����������B

���@2016.1.28

�@�@�E�����ATT������ł̓���͗ǂ��悤�Ȃ̂ŁA���̉������ATEST_2���@�ɑ��čs����

�@�@�@�Ǝv���B

�@�@�@�������\�啝�����ƂȂ�̂ŁA�ɗ͌���ATT��H�̖ʉe���c�����܂܂̉����Ƃ������B

�@�@�@�o���邾�������ӏ������Ȃ����邱�Ƃ��l�����B

�@�@�@�܂��A�i���OSW�́A74HC4052�i4��1 *2��H�j�łȂ��A74HC4051�i8��1

* 1��H�j�̂܂܂ɂ�

�@�@�@�d�������W�ؑ֎��ӂ̉�H�i1, 2, 4pin�iA, B, C�j��3bit�Őؑցj�����̂܂܂ɂ���B

�@�@�@��������ƁA�A�i���OSW�̌㔼4���́iX4�`X7�j���]�邪�A������GND�ɗ��Ƃ��B

�@�@�@�����āA�����W�ؑփ��[�^���f�B�b�vSW�̈ʒu���A'4'�`'7'�̎��́A�t���̓d�������W�̂Ƃ����

�@�@�@"GND"�ƕ\�����邱�Ƃɂ����B

�@�@�@���̕��j�ŁA�����}�ʂƁATEST_3���@�Ƃ��Ă̐}�ʂ��쐬�����B

�@�@�@�܂��\�t�g���X�V��HEX�܂ŗp�ӂ����B

���@2016.1.29

�@�@�E�{���[�����A�������I������B

�@�@�ETEST_2���@�AATT������̃`�F�b�N�ŁA�܂�����m�C�Y��蔭��

�@�@�@�@�@�����と�@HEX������OK

�܂��́A�d���R���f�B�V�����m�F�i�ғ����j

�@�@�@�@�@ +5V= 5.18V �iATT��H������̏ꍇ�F5.22V�j

�@�@�@�@�@ -5V= -4.95V�@ �iATT��H������̏ꍇ�F-5.04V�j

�@�@�@�@�@ +3.3V=3.29V

�@�@�@�@�@ AVCC=3.26V

�@�@�@�A�@�g���}������OK

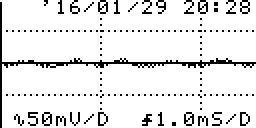

�@�@�@�@ ���OK�����A1�F1�v���[�u�A50mV/D

AC�����W�ŁA10uS/D�ő���\�������ꍇ�A�g�`��

�@�@�@�@�@ �d��m�C�Y�������悤�ȋC������B

�@�@�@�@�@

�������̃����W�����ł͋C���t���Ȃ������̂��͕s�������E�E�E

�@�@�@�@�@ �C�ɂȂ�̂́AATT��H������̏ꍇ�Ɣ�r���āA+5V�ƁA-5V����ቺ���Ă���_�ł���B

�@�@��������

�@�@�@�@�@-5V���C���̃��b�v���g�`�����Ă݂��B

�@�@�@�@�@ ���̒ʂ�A�ȑO������g�`������x���͏オ���Ă��邪�A���ɂȂ郌�x���ł͂Ȃ��悤���B

�@�@�@�@�@�@ �i+5V��LC�t�B���^�������Ă���̂Ŗ��Ȃ��B�j

�@�@�@�A�@�o�b�t�@�A���v�́A-5V���̃p�X�R��0.1u�ɁA100u���p���ڑ�����Ǝ�A�g�`�m�C�Y�͏��Ȃ��Ȃ邪�A

�@�@�@�@�@

������������X�y�[�X�����Ȃ茵�����̂ŁA����͂�肽���Ȃ��B

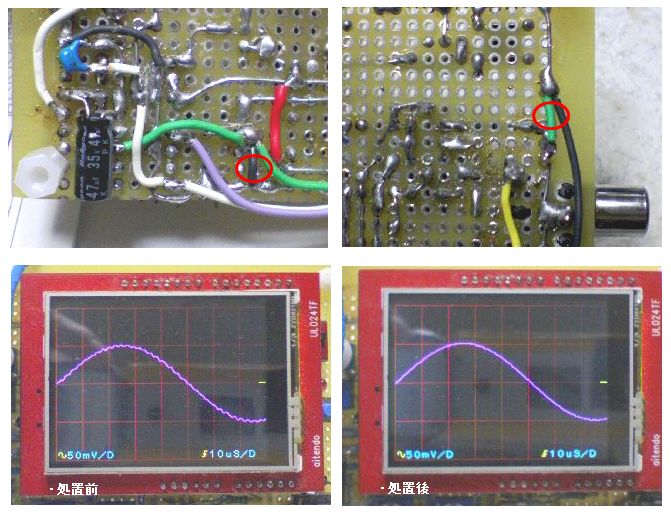

�@�@�@�B�@ATT��H������Ŏ������Ă��鎞���A���̃����W���ǂ����������͊o���ĂȂ������C����iTEST_2��j

�@�@�@�@�@ �Ƃ́AGND�ڑ��_��ς�����A�m�C�Y�����Ȃ茸�������Ƃ��v���o�����B

�@�@�@�@�@ ���̎��́AATT��H������́AAGND�ƁA���C����́A3.3V���M�����[�^��GND�t�B���i�L��GND�d�Ɂj

�@�@�@�@�@ ���N���b�v�Őڑ�������悭�Ȃ����B

�@�@�@�@�@ RCA�R�l�N�^�ɋ߂�AGND�Ƃ̐ڑ��ł͑ʖڂ������B

�@�@�@�@�@ ���ǁA�d���߂��ŁAAGND�ƁADGND��ڑ����Ă���̂����A����Ƃ͕ʂɁARCA�R�l�N�^�́AAGND�ƁA

�@�@�@�@�@ ���̋߂��ɗ��Ă���ADGND��ڑ�������A�m�C�Y���A���Ȃ茸��A�g�`�ɏd��m�C�Y���w�nj����Ȃ��Ȃ����B

�@�@�@�@�@�@�i�����Ƃ������������W�Łj

���@2016.1.30

�@�@�E����őË������_�����邪�A���Ƃ������ړI��B�����Ǝv���̂ŁA���̃v���W�F�N�g�́A�����܂ł�

�@�@�@�N���[�Y�������B

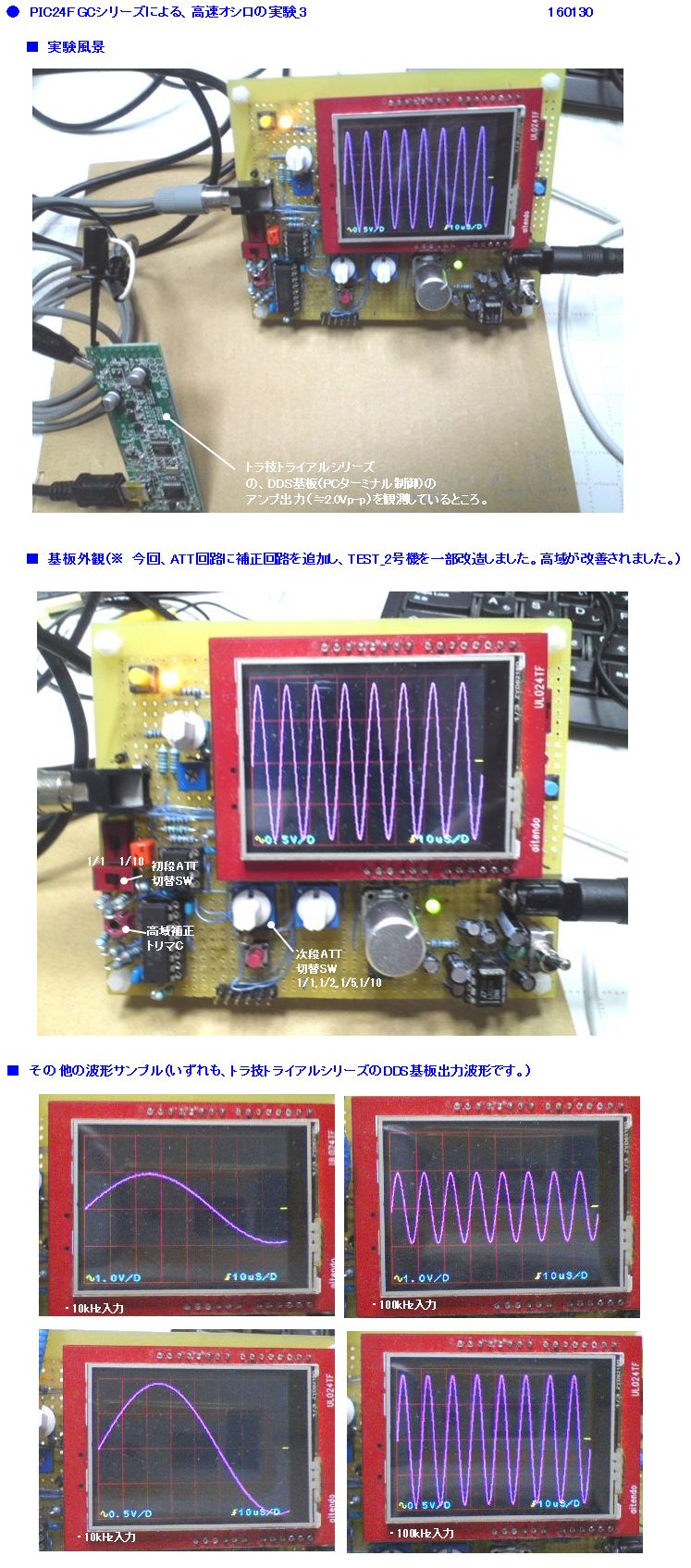

�@�@�@�Ō�ɁATEST_3���@�Ńg���Z�g���C�A���V���[�Y�́ADDS��̃A���v�o�͂��ϑ���������A

�@�@�@���̃y�[�W�g�b�v�ɃA�b�v���܂����B

�@�@�@�Q�Ƃ��Ă��������B

---����������A�ǎ��F�u�`���c�L���ƁA�\���X�V�Ԋu�̉��P�v�̋L����-------------------------------------

���@2016.11.11

�@�@�EPIC24FGC�V���[�Y�����I�V���ɑ��Ă��A�����e�[�}52�́A�J���[��2CH�I�V��V6�Ɠ���

�@�@�@���u�����ĉ��P�����݂��B

�@�@�@���P�̕��@���́A��{�A�����e�[�}52�́A2016.11.7����̋L���Ɠ����Ȃ̂ŎQ�Ƃ��Ă��������B

�@�@�@���ʓI�ɂ́A����Ȃɖ��Ȃ���肭�s���B

�@�@�@�����A1���������ʓ|�ȂƂ��날��B

�@�@�@����̓g���K�E�J�[�\���̕\���ł���B

�@�@�@�����A�\���X�V���ƂɁA�S��ʃN���A���Ă��̂Ŗ��Ȃ��������A�������߂āA�g�`���̂�

�@�@�@�N���A����悤�ɂ����̂ŁA�J�[�\�����ړ�����ƁA���̑O�̃J�[�\���\�����c���Ă��܂��B

�@�@�@����́A���[�^���E�G���R�[�_�Ǎ��݊��̂Ƃ���ŁA��]�L�肪���m���ꂽ��A

�@�@�@�J�[�\���́AY���W���C���N�������g���A�f�B�N�������g����O�ɁA���݈ʒu�̃J�[�\��

�@�@�@���N���A����悤�ɏC��������A��肭�s���B

�@�@�@��������ł��A�J�[�\�����Z���^�[�ʒu�ɂ��鎞�́A���W�����ĕ`�悷�鎞�A���F�̃J�[�\����

�@�@�@�̏�ɁA���̍��W�����d�Ȃ�̂ŁA�J�[�\�����A�u�����N���Ă���悤�Ɍ����邪�A��������

�@�@�@�Z���^�[�ʒu�Ƀg���K�_�����邱�Ƃ������ėǂ��ƁA�ǂ����ɉ��߂��āA�ǂ��Ƃ����B

�@�@�@�܂��A�z�[���h����A���Ȃ��J�[�\�����Y��ɕ\�������̂Ŗ��͂Ȃ��B

���@2016.11.14

�@�@�E�v���Ԃ�Ƀ\�[�X���������ƁA���\�Ȋm���ŁA���ʂȋL�q�ɁA�C�t���ꍇ�������B

�@�@�@���������ȁA���ʂȋL�q�����Ă��܂����̂ŁA�C�����Ă������B

�@�@���@�O���[�o���ϐ��錾�ƁA��2�����ŁAIndex�ϐ������邪�A����́A

�@�@�@�@ �I���W�i���E�\�[�X�i��Ղ���j�́ABT���W���[���̃R�}���h��M�o�b�b�t�@�pIndex�ł����āA

�@�@�@�@ ����͎g���ĂȂ��B

�@�@�@�@ DMA�]���̓n�[�h�Ŏ����I�ɍs����̂ŁAIndex�͕K�v�Ȃ��B����ăR�����g�A�E�g�ɂč폜�����B

���ŏI��H�}��

�@�E�����炩��A�ǂ������@�uPIC24F_GC_�����I�V��������H_3�i1/2�j�v�@�F�@�f�W�^�����{�A�i���O��2

�@�@�@�@�@�@�@�@�@�@�@�@�@�@�@�@�@�@�@�uPIC24F_GC

�����I�V��������H_3�i2/2�j�v�@�F�@�A�i���O��1

���ŏI�\�[�X��

�@�E�����炩��A�ǂ������@High_Speed_Oscillo_Test_3.c

�@���@���C���E�\�[�X���X�V���܂����B161115�� High_Speed_Oscillo_Test_5.c

���@���̑��ɁAQVGA�t�����C�u�����ƁA�t�H���g�f�[�^�i�w�b�_�t�@�C���j���K�v�ł����A

�@�@�@�@����́A�e�[�}72�̂Ɠ��l�Ȃ̂ŁA��������Q�Ƃ��Ă��������B

���@�����e�[�}1�ɖ߂��@�@�@TOP PAGE�ɖ߂��@�@�@�����e�[�}75�ց@��