仠丂幚尡僥乕儅127

乽CQ_DDS_SWEEPER懠乿

乮幚尡僥乕儅126偺僼傽乕儉僂僄傾乮傾僾儕乯傪夵斉偟10k乣20MHz偺僗僀乕僾傕弌棃傞傛偆偵偟傑偟偨丅偙傟偲懳偱巊梡偡傞廃攇悢摿惈應掕憰抲偺婰帠傕彂偒傑偟偨丅乯

仭丂2020.9.23

丂 丒師偺傛偆側摦嶌巇條偱丄CQ_DDS_SWEEPER僾儘僕僃僋僩傪棫忋偘傑偟偨丅

丂丂丂亙摦嶌巇條亜

丂丂丂丂嘆丂DOWN_SW傪墴偝側偄偱丄P_ON偟偨応崌

丂丂丂丂丂丂 捠忢儌乕僪

丂丂丂丂丂丂 廬棃偺儘乕僞儕僄儞僐乕僟偵傛傞儅僯儏傾儖愝掕

丂丂丂丂嘇丂DOWN_SW傪墴偟偰丄P_ON偟偨応崌

丂丂丂丂丂丂 SWEEPER儌乕僪

丂丂丂丂丂丂 10k乣 20MHz傑偱偺僗僀乕僾摦嶌

丂丂丂丂丂丂 ON SW傪丄START SW偲偟偰巊偆丅

丂丂丂丂丂丂 乮SW儕乕僪偵妱崬傒偼巊傢側偄丅乯

丂丂丂丂丂丂 RB4億乕僩弌椡偵丄廃攇悢摿惈應掕憰抲乮easy_fra_v3偺夵憿梊掕乯偲摨婜傪庢傞堊偺SYNC僷儖僗傪弌椡

丂丂丒彯丄僜僼僩偵偮偄偰偼丄僽乕僩儘乕僟晹偼巆偟偰傾僾儕晹偵僗僀乕僷婡擻傪捛壛偟傑偟偨丅

丂丂丂偙傟偼丄C18偱婰弎偟丄USB巊梡偺丄PC傾僾儕 HIDBootloader (Windows).exe偵傛偭偰hex彂崬傒傪峴偄傑偡丅

仭丂2020.9.25

丂 丒僐儞僷僀儖OK丒HEX傑偱弨旛弌棃丄摦嶌妋擣傕堦墳OK偵側傞丅

丂丂

徻嵶偵偮偄偰偼丄偙偺儁乕僕枛旜偺僜乕僗傪嶲徠偟偰偔偩偝偄丅

仭丂2020.9.28

丂 丒easy_fra_v3a僾儘僕僃僋僩乮僴乕僪丒僜僼僩嫟v3傪丄夵憿丒夵斉乯傪奐巒偟偨丅

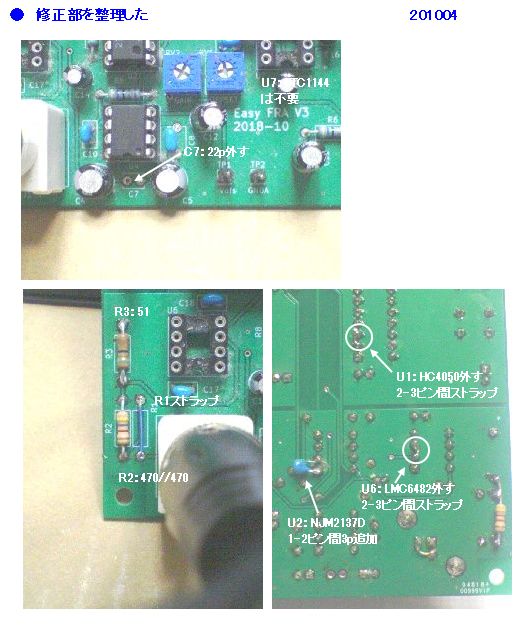

丂丂丂崱夞偼丄20MHz偺崅廃攇傑偱傪庴偗傞偺偱丄LOG傾儞僾擖椡偺懷堟惂尷梡僐儞僨儞僒偺丄22p偼嶍彍偟偨丅

丂丂丂傑偨丄SYNC僷儖僗偺擖椡儗儀儖曄姺梡偺丄74HC4050偼晄梫側偺偱僜働僢僩偐傜奜偟丄僜働僢僩偺擖椡3pin偲弌椡2pin傪僗僩儔僢僾偟偨丅

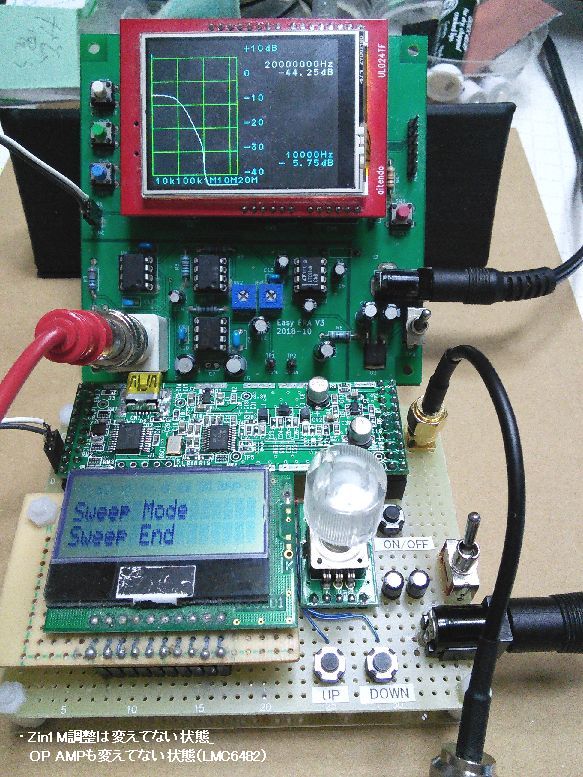

丂丂丂傑偢偼偙偺夵憿偺傒偱丄OP傾儞僾乮LMC6482乯傕曄偊偢丄GAIN偲OFFSET億僥儞僔儑偺挷惍埵抲傕偦偺傑傑偱丄僗儖乕偺F摿傪庢偭偰傒偨丅

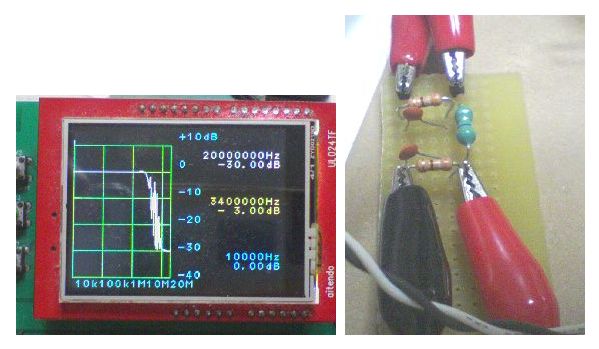

丂丂丂埲壓偺傛偆側寢壥偱丄僼儔僢僩椞堟偼丄0dB偱側偔壓偑偭偰偄傞偟丄50kHz嬤曈偐傜憗偔傕儗儀儖偑壓偑傝巒傔偰偄傞丅

丂丂丂僼儔僢僩椞堟偑丄0dB偱側偄偺偼丄CQ_DDS_SWEEPER弌椡偑丄1M僀儞僺偱庴偗偨応崌丄2Vp-p屌掕乮50兌晧壸偱1Vp-p乯偱丄

丂丂丂偙傟傑偱丄0dB偺婎弨傪丄1Vp-p偱側偔丄1Vrms乮1.4V x 2=

2.8Vp-p乯偵偟偰偄偨堊偱偁傞丅偙傟偼曄偊傞偮傕傝偼柍偄丅

丂丂丂擖椡偑掅偄偺偱丄擖椡ATT偺尭悐斾傕丄1/10偐傜丄1/6掱搙偵壓偘側偄偲LOG傾儞僾弌椡偑崌傢側偔側傞丅

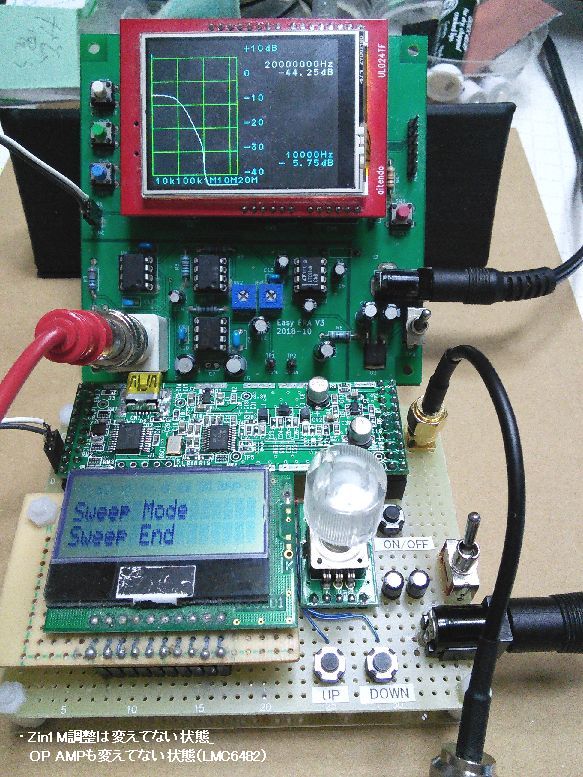

丂丂丂偦偙偱娙堈揑偵丄ATT乮僩乕僞儖丗1M兌乯傪峔惉偟偰偄傞掞峈偺撪丄470k偺椉抂傪僋儕僢僾偱僔儑乕僩偟丄430k偲100k偺暘埑偺傒偱栺1/6偵

丂丂丂偟偰傒偨丅偨偩偙傟偩偲LOG傾儞僾偺弌椡儗儀儖偑忋偑傞偺偱丄屻抜傾儞僾偺GAIN僩儕儅傪峣偭偰丄0dB偵崌傢偣偰傒偨丅

丂丂丂埲壓偵偦偺帪偺幨恀傪帵偟偨丅懡彮1M嬤曈偺尭悐偑尭偭偨偑丄偨偩扨偵摿惈偑忋偵僔僼僩偟偰偄傞傛偆側姶偠丒丒丒

丂丂丂挷傋偨傜丄懷堟偑嬌抂偵怢傃側偄偺偼丄LMC6482偺丄儐僯僥傿僎僀儞偱偺懷堟GBW偑丄1MHz偲嫹偔慡慠懯栚側偙偲偑敾柧偟偨丅

丂丂丂廐寧偱庤偵擖傞丄峀懷堟偺OP傾儞僾丗NJM2137D乮GBW=200MHz乯傪庤攝偟偨偺偱丄撏偒師戞丄帋偟偰傒傞丅

仭丂2020.9.30

丂 丒NJM2137D偑撏偄偨丅

丂丂丂崱夞偺帋峴忦審偼師偺條偵偟偰傒偨丅

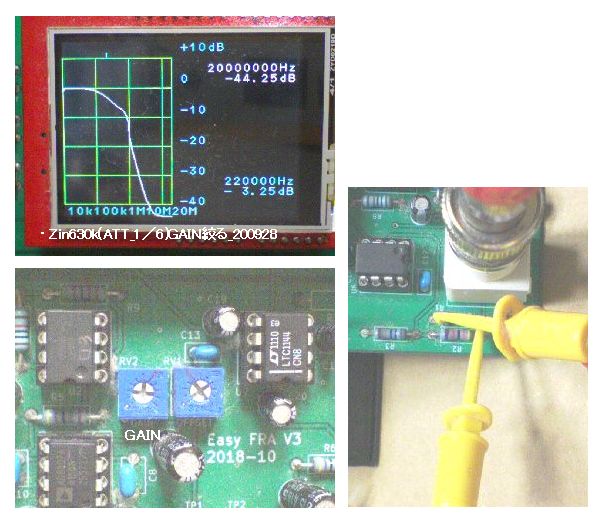

丂丂丂嘆丂擖椡偼掅僀儞僺乕僟儞僗偱庴偗傞偙偲偵偟丄弶抜偺揹埑僶僢僼傽偼僜働僢僩偐傜敳偄偨丅

丂丂丂嘇丂偦偟偰丄DDS弌椡掞峈偺丄51兌傪娷傔偰栺1/10偺ATT偵側傞傛偆偵丄掞峈抣傪寛傔偨丅

丂丂丂丂丂 庤帩偪偺掞峈偺娭學偱丄470兌偺僷儔愙懕乮235兌乯偲丄51兌偺慻崌偣偵偟偨丅

丂丂丂嘊丂LOG傾儞僾弌椡偺丄OP傾儞僾偺傒丄NJM2137D偵岎姺偟偨丅

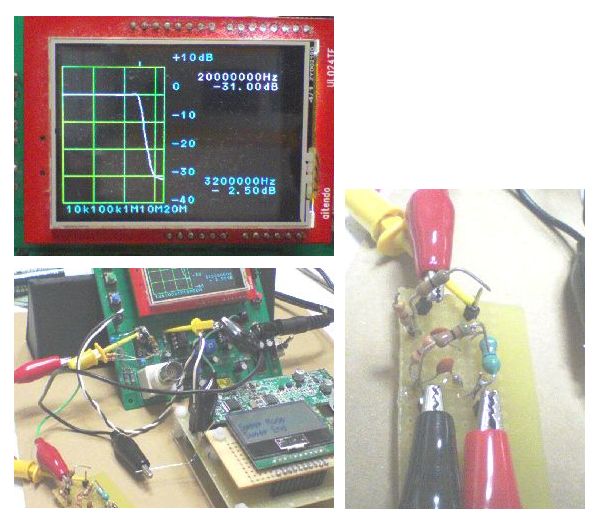

丂丂仸丂寢壥偼丄10MHz傑偱偼傎傏僼儔僢僩偱丄20MHz偱傕丄-1dB偺僟僂儞偵偲偳傑偭偨丅

丂丂丂丂 彯丄GAIN億僥儞僔儑偺埵抲偼v3偺帪偺傑傑偱丄OFFSET億僥儞僔儑偺傒彮偟忋偘傑偟偨丅

仭丂2020.10.1

丂 丒娙扨側丄LC偺兾宆LPF乮L= 4.7uH, C= 1000p乯傪慻傫偱丄偦偺F摿傪庢偭偰傒偨偲偙傠丄

丂丂丂-3dB揰傑偱偼栤戣側偄偺偱偡偑丄埵憡偑夞傝巒傔傞崅堟偱丄偼偱側僶僞僣僉偑尒傜傟傑偟偨丅

丂丂丂幨恀偱偼丄390兌偺廔抂傪晅偗偰偄傑偡偑丄柍偔偰傕杦偳摨偠忬懺偱偟偨丅

仭丂2020.10.3

丂 丒崅堟偺僶僞僣僉傪捛偆丅

丂丂丂崅堟偱丄峀懷堟OP傾儞僾偺弌椡偑敪怳偟偰偄傞偺偱偼側偄偐偲悇掕乮崅懍僆僔儘傪帩崌偣偰柍偄偺偱妋擣晄壜乯偟

丂丂丂NJM2137D偺僼傿乕僪僶僢僋儖乕僾偵丄3p偺埵憡曗彏傪擖傟偰傒偨傜尒帠偵僶僞僣僉偼柍偔側偭偨丅

丂丂丂崱夞偼丄帯嬶偺廔抂掞峈偼奜偟傑偟偨丅

仭丂2020.10.4

丂

丒崱枠丄廋惓晹傪僶儔僢僋偱愙懕偟偰幚尡偟偰偒偨偑丄偙偙偱廋惓晹傪堦扷惍棟偟傑偟偨丅

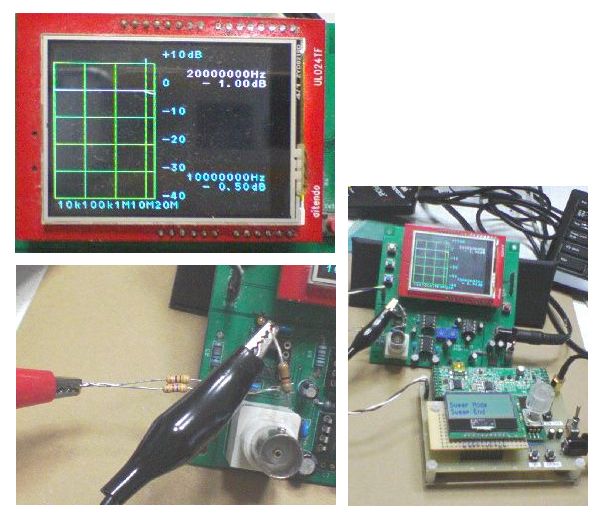

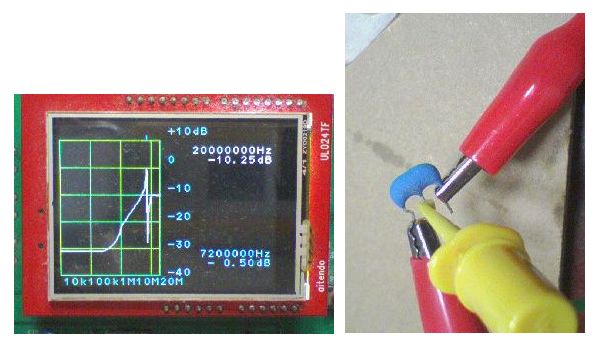

丂丂丒LPF偩偗偱偼偮傑傜側偄偺偱僒儞僾儖偲偟偰丄庤帩偪偺丄8MHz僙儔儘僢僋乮僙儔儈僢僋怳摦巕乯偺丄F摿傪庢偭偰傒傑偟偨丅

丂丂丂應掕朄偵帺怣偑側偄偺偱偡偑丄扨弮偵擖弌椡僺儞偵丄偦傟偧傟DDS弌椡偲丄easy_fra_v3a偺擖椡傪愙懕偟丄

丂丂丂GND僺儞偲儃乕僪偺GND傪愙懕偟偰應掕偟傑偟偨丅

丂丂丂10kHz偐傜僗僀乕僾偟偰偄傞偺偱巄偔偼丄-30dB晅嬤偱偡偑丄1MHz晅嬤偐傜彊乆偵忋徃偟丄8MHz偺嬤朤偐傜

丂丂丂媫忋徃偟偰峴偒丄惓偺嫟怳揰偲丄晧偺斀嫟怳揰偑懚嵼偡傞偦傟傜偟偄僇乕僽偑妋擣弌棃傑偟偨丅

丂丂丂偨偩丄嫟怳揰偺廃攇悢傪僇乕僜儖偱撉庢傞偲丄7.2MHz偲側偭偰偄傞偺偑婥偵側傝傑偡偑丒丒丒偙傟偼椙偟偲懨嫤偟傑偟偨丅

丂丂丂崱屻壗偐暘偐偭偨傜捛婰偟傛偆偲巚偄傑偡丅

亙夞楬恾亜

丂丒偙偪傜偐傜偳偆偧仺丂乽CQ_DDS_SWEEPER乿

丂丂丂丂丂丂丂丂丂丂丂丂 乽easy_fra_v3a傊偺廋惓巜帵夞楬恾乿

丂

亙嵟廔僜乕僗亜

丂(1) CQ_DDS_SWEEPER

丂丂丂丂/// 儊僀儞僜乕僗

丂丂丂丂丂CQ_DDS_SWEEPER.c

丂丂丂丂丂/// LCD儔僀僽儔儕

丂丂丂丂丂SW_i2cLCD.c

丂丂丂丂丂SW_i2cLCD.h

丂(2) easy_fra_v3a

丂丂丂丂/// 儊僀儞僜乕僗

丂丂丂丂丂easy_fra_v3a.c

丂丂丂丂丂/// QVGA LCD儔僀僽儔儕

丂丂丂丂丂colorlcd_libdsPICVH.c

丂丂丂丂丂colorlcd_libdsPICVH.h

丂丂丂丂丂/// 僼僅儞僩僥乕僽儖

丂丂丂丂丂ASCII12dot