● 実験テーマ109

「KiCad事始め-その2」

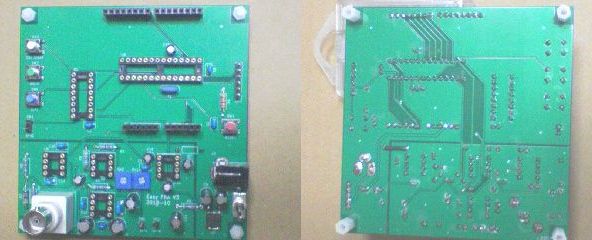

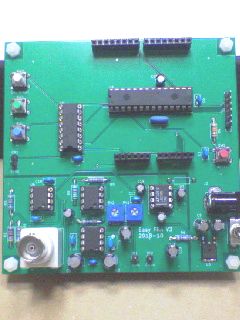

(具体的なプロジェクトとして、手始めにテーマ70の、P板化:Easy_FRA_V3にしてみました。)

■ 2018.9.6

・ユニバーサル基板で製作した物の、P板化ですが、まずは計画から

① QVGAの取り付けは、アダプター基板を介さないで行う。

② 3端子レギュレータは、SMTに変更

③ チップは、②のみで、他は通常使っているDIPにする。

④ 抵抗は、マルツの小型サイズの1/4Wでなく、全て標準サイズにする。

⑤ まずは、プロジェクトシンボルを調査

新規作成/既存/修正で使うものの振分けから

・Eagleのマイライブラリでよく使っている部品を、KiCadライブラリから探す。

① フットプリント

※1.ギザギザマークの抵抗シルクは、KiCadには無い。矩形のみだが、これはこのまま使う。(回路シンボルにはある)

※2.電気的シンボルの横実装コンデンサシルク、KiCadには無い。外形をリアルに表現。これはこのまま使う。(今回は全て縦実装)

■ 2018.9.7

・手始めに、普通サイズとスモールサイズの金属皮膜・炭素被膜抵抗のフットプリントが、標準ライブラリにあるか探してみる。

① MF1/4CCxxxxF "KOA"

LxD= 6.3x2.3mm(実測)/実装ピッチP= 7.62mm/リード径=

0.6φ/ドリル径= 0.8φ

KiCadライブラリ名:Resistor_THT

がDIPの抵抗ライブラリ

|-

フットプリント名:R_Axial_DIN0207_L6.3mm_D2.5mm_P10.16mm_Horizontal

が使えそう。

※ ドリル径をビューワの、dxで確認したところ、0.8mmになっていた。

パッド径をビューワの、dxで確認したところ、1.6mmだった。

② MFS1/4CCxxxxF

"KOA"

LxD= 3.2x1.7mm(実測)/実装ピッチP=

7.62mm/リード径= 0.45φ/ドリル径=0.8φ(Eagleの時は、0.8に揃えたが特にその必要はない)

KiCadライブラリ名:Resistor_THT

がDIPの抵抗ライブラリ

|-

R_Axial_DIN0204_L3.6mm_D1.6mm_P7.62mm_Horizontal が使えそう。

※ ドリル径をビューワの、dxで確認したところ、0.7φ

パッド径をビューワの、dxで確認したところ、1.4φだった。

③ 積層セラ2.5mmピッチ:RPEF11H104Z2P1A

"村田"

DxW= 5x2.5mm/実装ピッチP=

2.5mm/リード径= 0.5φ/ドリル径= 0.8φ

KiCadライブラリ名:Capacitor_THT

がDIPのコンデンサライブラリ

|-

フットプリント名:C_Disc_D5.0mm_W2.5mm_P2.50mm が使えそう。

※ ドリル径をビューワの、dxで確認したところ、0.8φになっていた。

パッド径をビューワの、dxで確認したところ、1.6φだった。

④ 積層セラ5mmピッチ:RPEF11H104Z2K1A

"村田"

DxW= 4x2.5mm/実装ピッチP= 5mm/リード径= 0.5φ/ドリル径=

0.8φ

KiCadライブラリ名:Capacitor_THT

がDIPのコンデンサライブラリ

|- フットプリント名:C_Disc_D4.7mm_W2.5mm_P5.00mm

が使えそう。

※ ドリル径をビューワの、dxで確認したところ、0.8φになっていた。

パッド径をビューワの、dxで確認したところ、1.6φだった。

⑤ 積層セラ2.5mmピッチ:RD15N220J1HL2L

"Superteh" 50V22p 秋月10個入り

DxW= 4x2.2mm/実装ピッチP=

2.54mm/リード径= 0.5φ/ドリル径= 0.8φ

KiCadライブラリ名:Capacitor_THT

がDIPのコンデンサライブラリ

|- フットプリント名:C_Disc_D3.8mm_W2.6mm_P2.50mm

が使えそう。

※ ドリル径をビューワの、dxで確認したところ、0.8φ

パッド径をビューワの、dxで確認したところ、1.6φだった。

⑥ 積層セラ5mmピッチ:RDER71H105K2K1H03B "村田" 50V1u 秋月

DxW= 5.5x3.15mm/実装ピッチP= 5.00mm/リード径= 0.5φ/ドリル径= 0.8φ

KiCadライブラリ名:Capacitor_THT がDIPのコンデンサライブラリ

|- フットプリント名:C_Disc_D5.1mm_W3.2mm_P5.00mm が使えそう。

※ ドリル径をビューワの、dxで確認したところ、0.8φ

パッド径をビューワの、dxで確認したところ、1.6φ

■ 2018.9.8

・続き。

⑦ 小型電解コンMH7シリーズ:16MH710MEFC4X7 "ルビコン":16V10u

D= 4φ(H=7)/実装ピッチP= 1.5mm/リード径= 0.45φ/ドリル径= 0.8φ(Eagleの時は、0.8に揃えたが特にその必要はない)

KiCadライブラリ名:Capacitor_THT

|- フットプリント名:CP_Radial_D4.0mm_P1.50mm が使える。

※ ドリル径をビューワの、dxで確認したところ、0.6φになっていた。

パッド径をビューワの、dxで確認したところ、1.2φだった。

⑧ 小型電解コンMH5シリーズ:16MH5100MEFC6.3X5 "ルビコン":16V100u

D= 6.3φ(H=5)/実装ピッチP= 2.5mm/リード径= 0.45φ/ドリル径= 0.8φ(Eagleの時は、0.8に揃えたが特にその必要はない)

KiCadライブラリ名:Capacitor_THT

|- フットプリント名:CP_Radial_D6.3mm_P2.50mm が使える。

※ ドリル径をビューワの、dxで確認したところ、0.8φになっていた。

パッド径をビューワの、dxで確認したところ、1.6φだった。

➈ 普通サイズ電解コンPKシリーズ:35PK47MEFC5X11 "ルビコン":35V47u

35PK33MEFC5X11 "ルビコン":35V33u

D= 5φ(H=11)/実装ピッチP= 2.0mm//リード径= 0.5φ/ドリル径= 0.8φ(Eagleの時は、0.8に揃えたが特にその必要はない)

KiCadライブラリ名:Capacitor_THT

|- フットプリント名:CP_Radial_D5.0mm_P2.0mm が使える。

※ ドリル径をビューワの、dxで確認したところ、0.8φ

パッド径をビューワの、dxで確認したところ、1.6φ

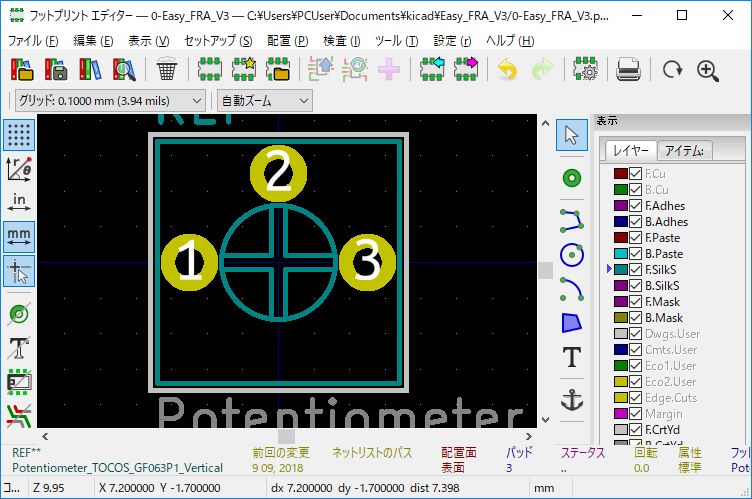

⑩ 半固定ボリューム:3362P-1-xxxLF "Bourns":秋月販売

GF063P1Bxxx "東京コスモス":マルツ

WxH= 6.8x6.8/実装ピッチP= 2.5mm・5.0mm/リード径= 0.5φ/ドリル径= 0.8φ(Eagleの時は、0.8に揃えたが特にその必要はない)

KiCadライブラリ名:Potentiometer_THT

|- フットプリント名:Potentiometer_Bourns

※ KiCad標準ライブラリPotentiometer_Bournsにあるのは殆どが多回転タイプ

普通回転タイプだが、Bourns 3362P:6.8x6.8は無かった。あるのは、3386F:9.53x9.53, 3386P:.53x9.53でピン位置が異なる。

⑪ 半固定ボリュームツマミ付き:3386K-EY5-xxxTR "SUNTAN TEC":秋月販売

これも標準ではなさそう。今回は未使用

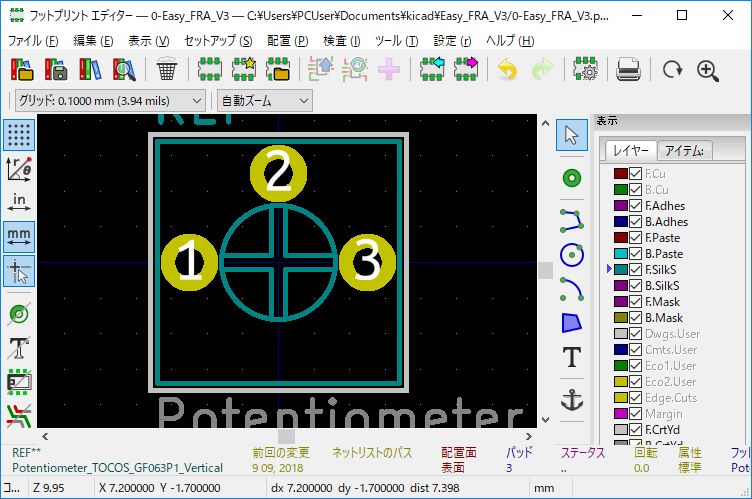

■ 2018.9.9

・続き。

※1 今日は、半固定ボリューム:3362P-1-xxxLF "Bourns":秋月販売

GF063P1Bxxx "東京コスモス":マルツ

のフットプリントを新規作成してみる。

標準フットプリントからの修正でもよいが、未知の部分も多いので新規作成のが

今は早いと思うし、やりながらテクニック取得に努めようと思う。昨日、Githupを検索してみたが適当なのはなかった。

まずは、プロジェクト名を決めないといけない。

以前UNVで作った簡易自動周波数測定装置_V3の、P板化にしようと思う。

プロジェクト名:「Easy_FRA_V3」とする。→新規作成

プロジェクト・フットプリント・ライブラリ名:「0-Easy_FRA_V3」とする。

ここに作成:フットプリント名=Potentiometer_TOCOS_GF063P1_Vertical→寸法表が解り易いのでBournsと互換のあるコスモスを使う。

→ ファイルエクスプローラ等を用いてEasy_FRA_V3プロジェクトのフォルダ配下に0-Easy_FRA_V3.prettyフォルダ作成・組込み

尚、使いたいシンボルは標準であった。「R_POT_US」

ついでに、プロジェクト・シンボル・ライブラリ:「0-Easy_FRA_V3.lib」 も作成しシンボルのコピーまで行う。

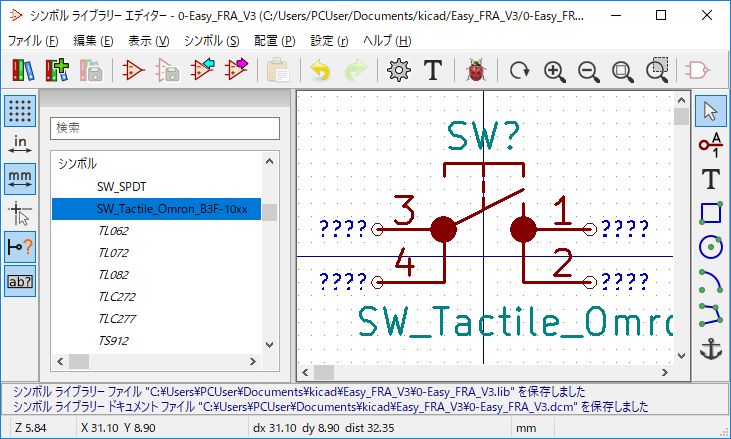

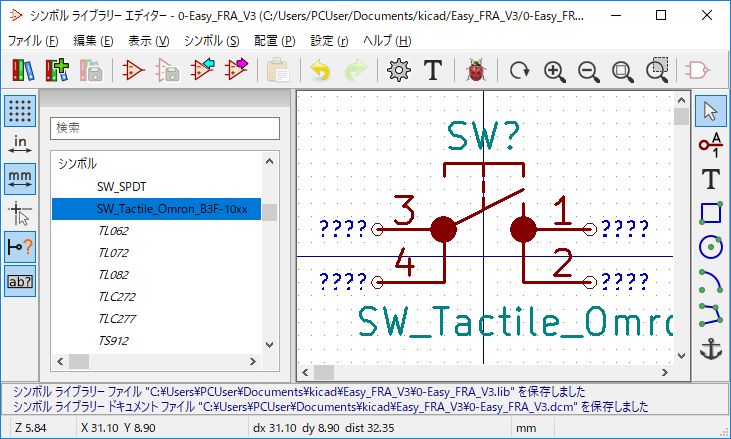

※2 次に、タクトスイッチ:B3F-1000相当 秋月があるか?→ 以下あった。(シンボル:SW_Push_Dual)

KiCadライブラリ名:Button_Swith_THT

|- フットプリント名:SW_TH_Tactile_Omron_B3F-10xx

※追記180919

シンボル:Switch-SW_Push_Dualは、単極プッシュが、2個連動したものなので、このタクトSWのイメージから外れる。

当該SWは、単極1回路で、comピンと、noピンが、それぞれ2ピンずつ出ているタイプでボタン付き

なので新規作成する。

シンボル名:SW_Tactile_Omron_B3F-10xx

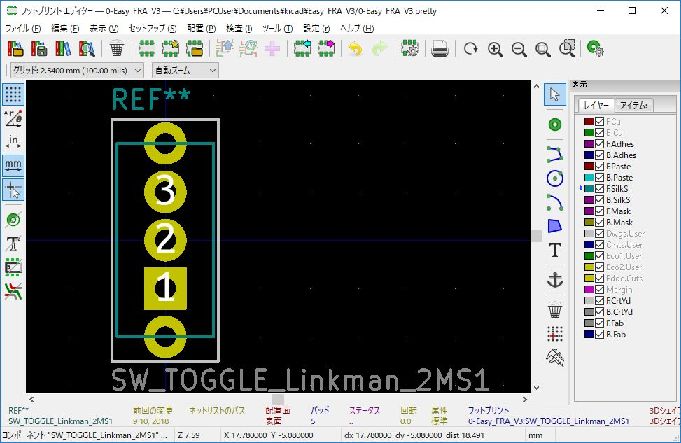

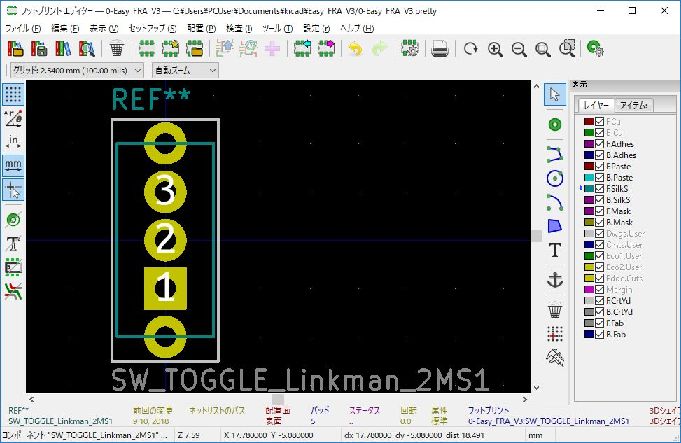

※3 次に、トグルスイッチ:2MS1-T1-B4-VS2-Q-E相当 秋月があるか?→ 以下

KiCad標準ライブラリには、トグルスイッチがなさそう。ただシンボルはあった:SW_SPDT→たぶん単極双投の意

github上にあるとの情報をwebで入手(2chスレ)

→ https://github.com/KiCad/Buttons_Switches_ThroughHole.pretty

にDIP, トグル, push スイッチがありました。→確認したがトグルは無かった。ガセ情報?新規作成する。

■ 2018.9.10

・続き。

※1 トグルスイッチ:2MS1-T1-B4-VS2-Q-E相当 これのフットプリントは自作することにした。

フットプリント名:SW_TOGGLE_Linkman_2MS1

[注意]:このSWには取付け用のピンが、2pinあるが、これをフットプリントエディタ上に置いて編集する時は

ピン番の欄は空欄にしてピン番無しにする。そうすればたぶんシンボルに、この取り付け穴を書かなくて済む。

※2 次に、セラミック振動子:CSTLS8M00G53-B0相当 秋月があるか?→ 以下あった。(ライブラリ名:Device・シンボル名:Resonator)

KiCadライブラリ名:Crystal

|- フットプリント名:Resonator_muRata_CSTLxxxG-3pin_W8.0mm_H3.0mm

[メモ]:灰色で描画されてるライン:Fabレイヤ(Fabricator(製作者)のためのレイヤ)は基板には印刷されない。

振動子は水晶を含めて、KiCadでは、ref= 'X'でなく'Y'になっているが、そのまま使う。何故かは不明だが・・ 180921

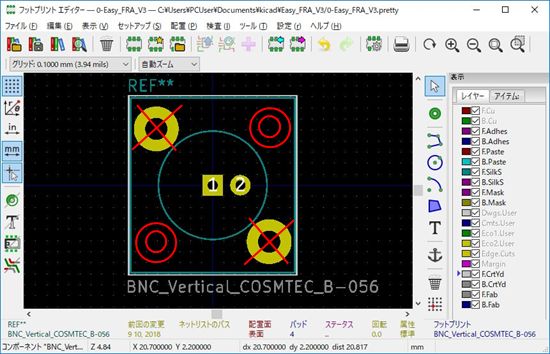

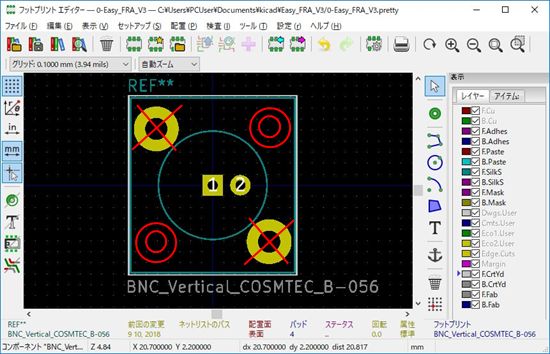

※3 次に、BNC:B-056相当 秋月があるか?→ (ライブラリ名:Connector・シンボル名:Conn_Coaxial)

フットプリントは無い。自作する。

|- フットプリント名:BNC_Vertical_COSMTEC_B-056

→ ※ 追記:181009

ドキュメントを整理している途中で、BNCコネクタの、B-056のフットプリントが間違っていることに気付く。

位置決め用のピン位置が180°反転していた。

メーカーの寸法図が、BOTTOM、TOP VIEWを、ごりゃまぜにして書かれている為、信号ピンと、GNDピンの位置

は問題無かったが、位置決め用のピン位置が反転してしまった。現物合わせがやはり必要だった。

P板のバージョンアップはこのプロジェクトではやらないことにした。

この次に、Easy_FRA_V4として、DDS部を一体化したハードを作る予定なので、その時に、

フットプリント名:BNC_Vertical_COSMTEC_B-056_REV1として作り直す予定。

以下のようなフットプリントの修正を予定しています。(朱書き部が修正部)

尚、今回の修正方法については、基板到着後の、10/24の記事を御覧ください。

■ 2018.9.11

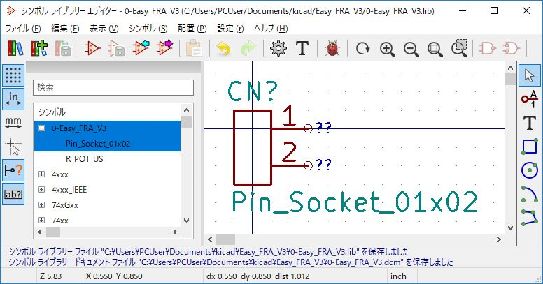

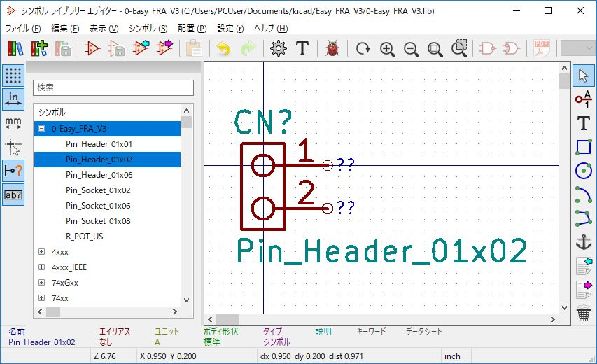

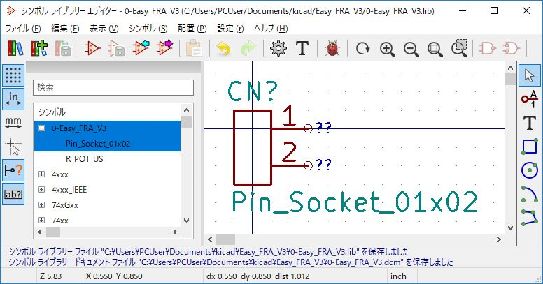

※1 今日は、ソケット・コネクタから

KiCadには枠有りシンボルのソケット・コネクタは大量ピンしか見当たらなかった。例:Conn_15x4

また枠有りシンボルのピン・コネクタは枠有りあったが適当でない。

Eagleの時と同じ、単なる矩形シンボルを自作することにした。

フットプリントは、KiCad標準にあった。外形シルクが1番ピンと他ピンで分かれているがピン数のバリエーションが多いので

そのまま使うことにした。

Connector

① 2, 6, 8pinソケット・コネクタ

シンボル名:Pin_Socket_01x02→ Connector_PinSocket_2.54mm

- PinSocket_1x02_P2.54mm_Vertical

シンボル名:Pin_Socket_01x06→ Connector_PinSocket_2.54mm

- PinSocket_1x06_P2.54mm_Vertical

シンボル名:Pin_Socket_01x08→ Connector_PinSocket_2.54mm

- PinSocket_1x08_P2.54mm_Vertical

尚、リファレンスは、JでなくEagleの時と同じ、CNにする。(ジャックと一般コネクタの種別をしたい為)

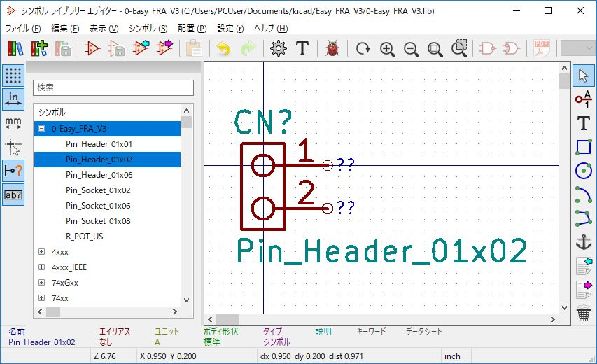

② 1, 2,

6pinヘッダ・コネクタ

シンボル名:Pin_Header_01x01→ Connector_PinHeader_2.54mm

- PinHeader_1x01_P2.54mm_Vertical

シンボル名:Pin_Header_01x02→ Connector_PinHeader_2.54mm

- PinHeader_1x02_P2.54mm_Vertical

シンボル名:Pin_Header_01x06→ Connector_PinHeader_2.54mm

- PinHeader_1x06_P2.54mm_Vertical

尚、リファレンスは、JでなくEagleの時と同じ、CNにする。

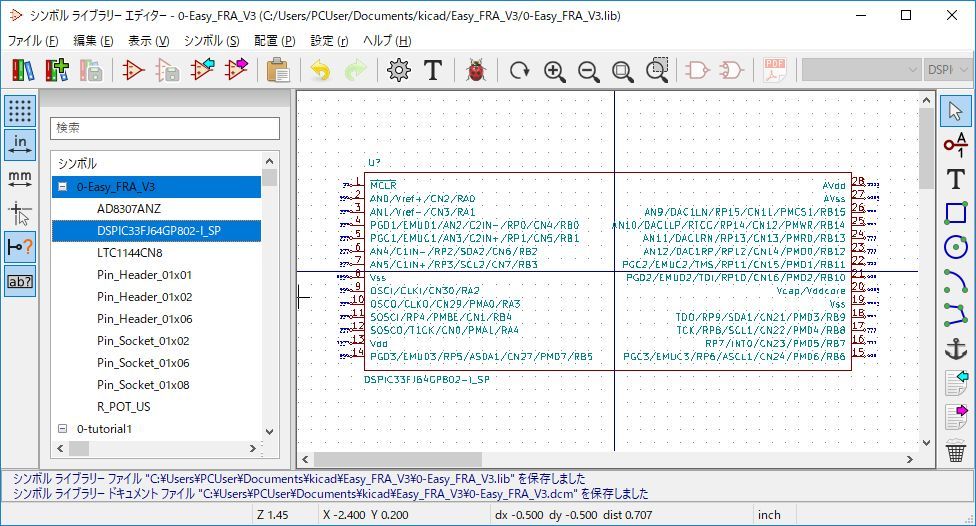

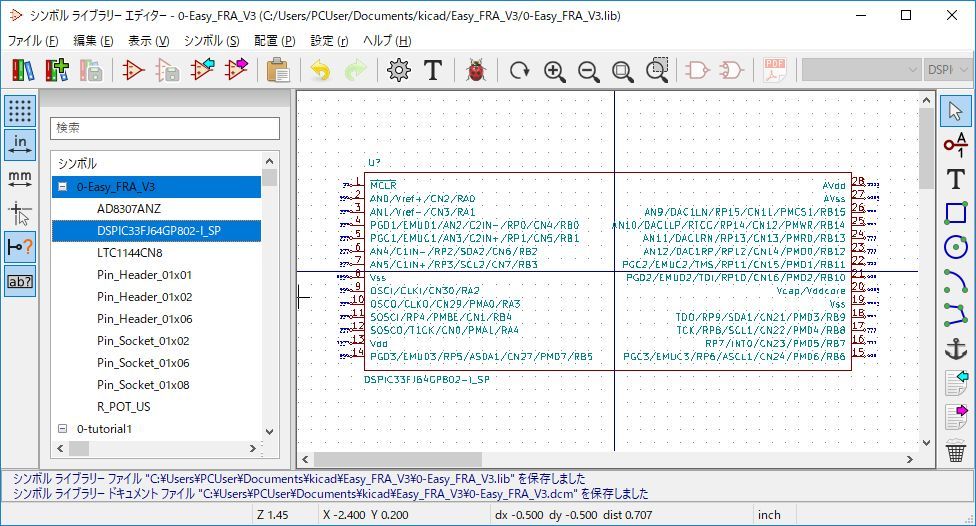

※2 IC類に移る。

① DSPIC33FJ64GP802-I/SP(DIP28)

KiCadには標準シンボル無し。有るのは、多ピンの、DSPIC33FJ64GP804(ライブラリ:DSP_Microchip_DSPIC33)

新規作成することにした。

シンボル名:DSPIC33FJ64GP802-I_SP→ どうもスラッシュは使えないようだ。_に置換えられてしまう。

※ <作業途中での特記事項はここにまとめておく>

・リファレンス名は、ICとしていたが、KiCadの標準は、Uのようなので、Uに統一することにした。

・負論理信号名は、チルダ(~)記号を前につけるだけ

・負論理ピンの丸にすると、KiCadの場合、ピン番号が〇に重なってしまうので通常ピン描画のみにした。

・グリッド設定は50milが基本。コンポーネントのピンがグリッド上に乗らないと配線できなくなる。

回路図エディタのグリッド設定が、50milになっている。

・ただICのボディの縦方向は、100mil単位サイズがバランスがよい。50milだと負論理のバーが1番ピンにあると、

外形線が重なってしまう。通常はピン間=100milだが、高密度にしたい時は、50milでもよさそう。

・シンボルのアンカーポイントを合わせる時は、グリッド設定50milでOK→ ピン間にも合わせられる。

・保存してしまった後、シンボル名を変更したい場合は、シンボル名にカーソル合わせ、'E'を入力。ダイアログの当該項目を修正でOK

・DGNDと、AGNDを回路図上で分けて書き、その一点アースポイントは、0Ω抵抗で両者を結ぶ方法(Eagleの時と同じ)でよいようだ。

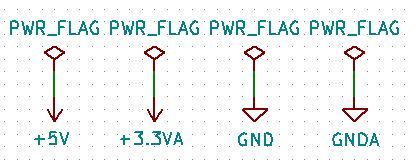

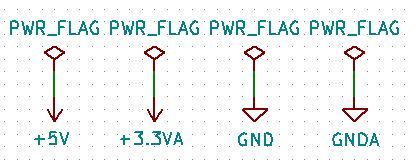

・POWER FLAGは、ERCの為に必要。POWERシンボルかどうかを知らしめるための物なので、全てのPOWERシンボルに必要と思われる。

・KiCadのic標準シンボルライブラリの書き方を見ると、

電源関係は縦方向に並べ、他の信号は横方向に並べている。

また、横方向の信号列は、ポート番号順に並べている。(例:RA0,RA1,RA2・・・)なのでピン番号の並びが順不同になってる。

Eagleの時は、icのピン配列のまま信号名を素直に振っていた。

こっちの方が、実装的に直観的に解り易いので、新規作成時は今迄通リの書き方で行くことにした。

・ピンの電気的特性は、vdd,gnd=電源入力・Vcap/Vddcore=電源出力・mclr=入力・その他のポート=双方向でよさそう。

・フットプリント・ビューワという言い方はしない。フットプリント・ウイザードと言う。

・KiCadメイン画面での既存プロジェクトのツリー表示は、作業中のプロジェクトしか表示出来ないようである。 180919

「既存プロジェクトを開く」で、他の既存プロジェクトを指定しても切り替わるだけである。

※ 例えば、0-tutoriale1内のフットプリント、MH-179Pを、0-Easy_FRA_V3へコピーして使いまわしたい時は 180919

以下のようにすればよい。

① フットプリント・エディタを起動

② 「アクティブなライブラリを選択」で、0-Easy_FRA_V4を指定

③ フットプリント・エディタ上ツールバー上の、「フットプリントをインポート」をクリック

④ フットプリント:MH-179Pを選択し表示させる。

⑤ 「アクティブなライブラリへフットプリントを保存」で保存

・シンボルの新規作成では、左ツールバーの単位は原則inchにしておく。(mmでも問題ない感じだが?) 180919

・拡大アイコンの吹き出し説明「シンボルに合わせズーム」は意味が分かりにくい。

ズームフィット:シンボル全体を画面にフィットさせて表示

が分かりやすい。

ここで言っているシンボル全体とは、name, valueも含んで全体と言っていることに注意。

偏って見えていても、シンボル本体のアンカーポイントが、(0,0)であれば問題無い。

・シンボルを置いた後、VALUE(CR類の定数・部品の型式名)を変更するには、ショートカット:'V'で開くダイアログ:フィールド定数の変更 180920

のテキスト欄を変更すればよい。

・空端子処理はシンボルでなく、右ツールバーにある「空端子フラグ」をピンに直接配置する。 180920

・オペアンプの分かち書きシンボルの、電源ピンブロックの、VALUEと、NAME(#REF)を非表示にするには 180921

VALUE→ ショートカット:"V"でダイアログの、[表示]項目の、非表示にチェックマーク

NAME(#REF)→ 右クリックで、[リファレンスを編集]→ フィールドリファレンスの編集ダイアログ-オプション項目の、非表示にチェックマーク

・シンボルのリファレンス名を編集するには、

右クリックで、[リファレンスを編集]→ フィールドリファレンスの編集ダイアログ-テキスト欄を編集 例 CN?→ TP?

・NETフラグ(矢形の中にNET)を使える。ダイアログで方向もシェープ(入力・出力・双方向等)も指示できる。Eagleはこれが出来なかった。

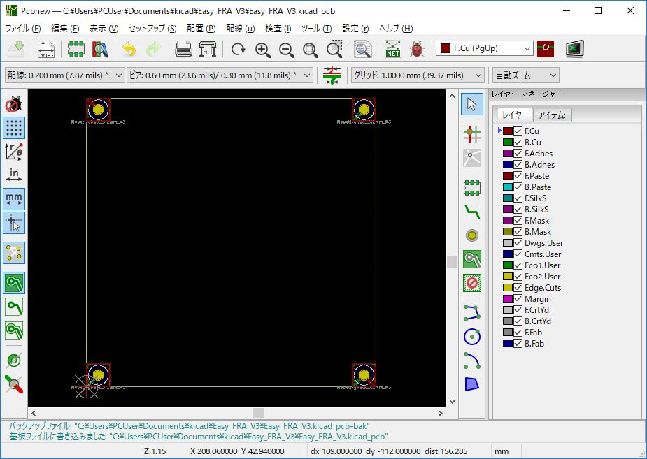

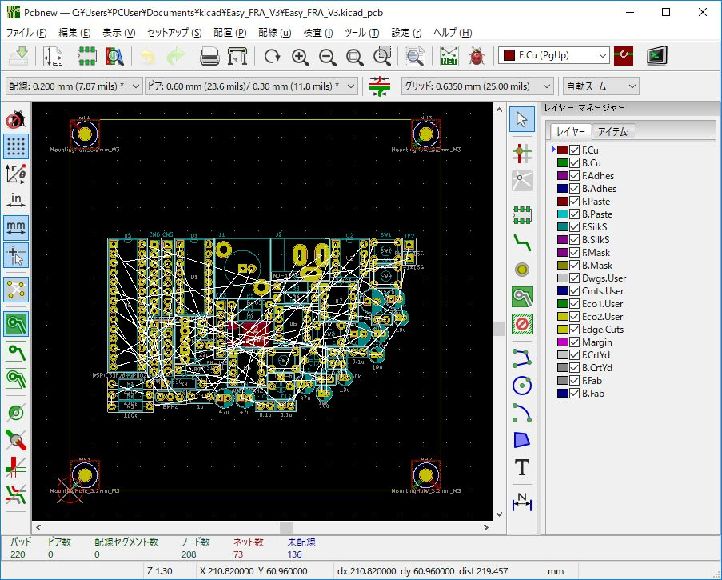

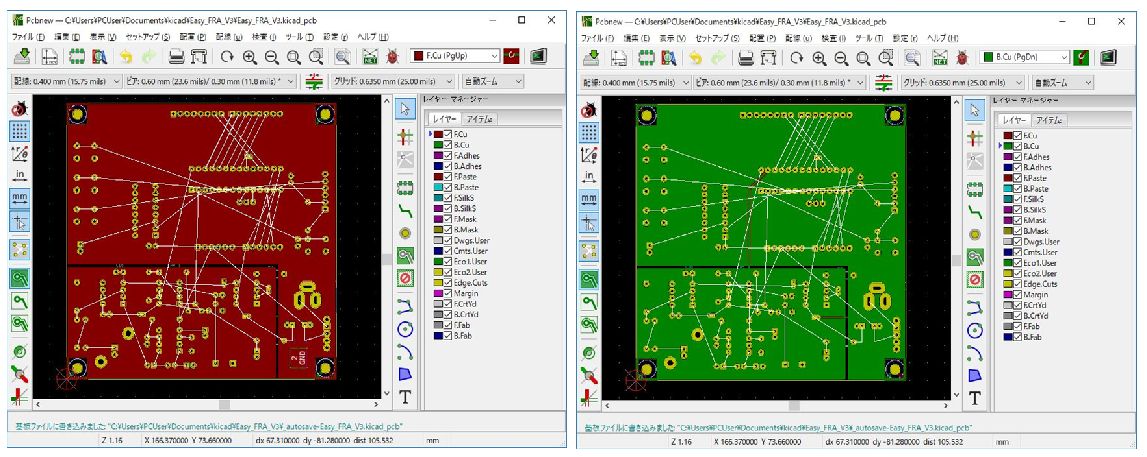

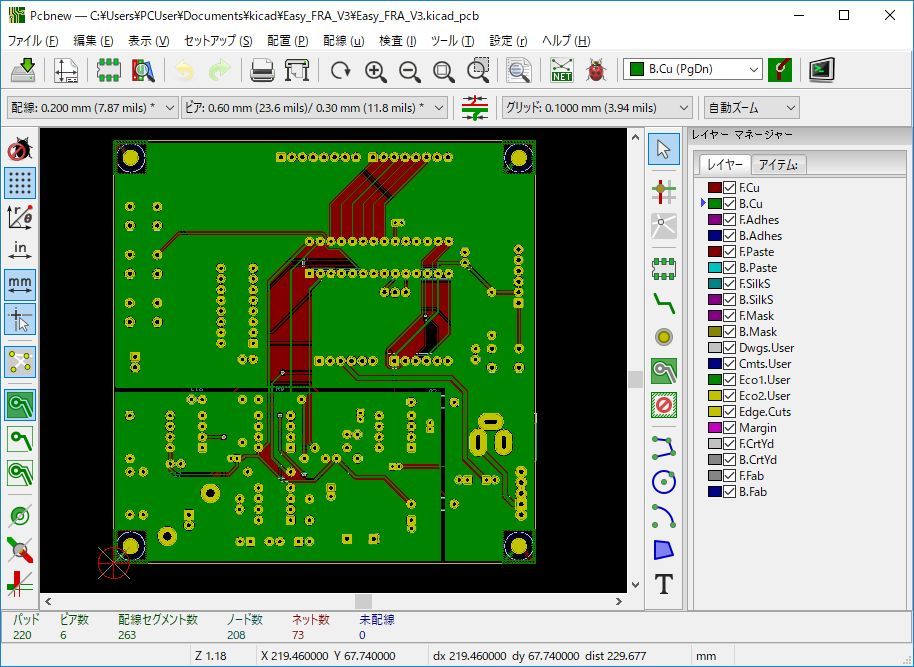

<PcbNew作業:180924~>

・作業原点設定について

図枠中央より、やや左下を作業原点:dx,dy=(0,0)に設定する。

ちなみに、図枠サイズは実測:297.18mm x 209.55mm あった。なので中央は、148.59x140.78

説明の図では、x,y=(115.57,115.57)を、dx,dy=(0,0)に設定してあった。

たぶんここは、やや左下であれば良いと思われる。何故こうしているのか詳細は今のところ不明。

→ <追記:180928>

原点マークにカーソルを合わせ、スペースキーを押して、dx,dy=(0,0)に設定する作業はボードを開く度に必要。

→ <追記:181006>

この設定を行わない場合や基板エディタの絶対座標でガーバーデータ出力をした場合、

ガーバービューアで確認すると原点が基板に対して離れたところに表示されて、

原点と基板の間に余計な余白ができてしまいます。

それでも製造上は問題ないかもしれませんが、なんとなく基板外形の端を原点ぴったりに合わせたいと

思うかもしれません。その場合はこの原点の設定を行ってみてください。

尚、この設定はベタ生成後に行ってもよい。(「iw回路設計」さんの、「基板作製プログ」より)

→ 図枠のセンターに基板外形のセンターが、だいたい一致する位置に作業原点を設定すれば良いだけと考える。

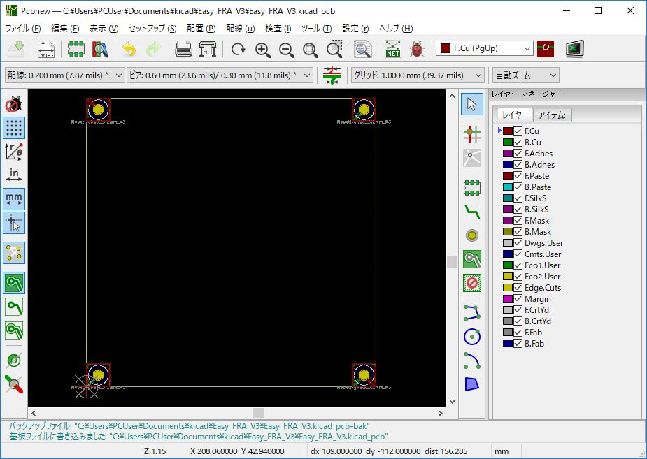

前回のtutorialの例では、基板サイズが、25x25だったので、x,y=(115.57,115.57)としていたが、今回は、100x100

なので、x,y=(97.06,154.94)位の位置で良い。見た目のアバウトで構わないと考える。

・複数の取り付け穴の配置について

説明の通リやったが、HOLEの複製(Ctrl+D)を置いて行くやりかたでは出来なかった。(ロックを無視している?)

一つ一つ、ウイザードから拾って配置して行けばよい。

ここでHOLEの番号は、1のまま変化しなくてよい。

・禁止帯の設定について

ハッチで四角のポリゴンを描いて行くが、最終位置のところで、「自己交差したポリゴンは許可されません」と赤字で

暫く表示されるが無視してダブルクリックしても何もエラーは出なかった。このまま進めて様子見。

・コンポーネント移動について

Mコマンドによる移動時の、基準位置は、カーソルで掴んだ位置になる。180928

・位置指定部品の配置

グリッドを細か目に設定し、相対座標値(dx,dy)を見ながら移動してセット。数値入力で出来ないものか? 180928

→ 数値入力で出来ないものか? 180929

フットプリントにポインタを合わせ、eコマンドで編集モード

プロパティダイアログ上の、x,y:絶対座標値(ただこれが絶対座標値:図枠左角上が原点)で指定

相対座標から変換して入力しないといけないので面倒。

・作業途中での回路図シンボル修正 180929

当該シンボル右クリック→ エディタでシンボル編集

・フォワードアノテーション:回路図修正をボードに反映 180929

<シンボルのピン番テレコ修正の例>

① まずシンボルを修正(新規シンボルなので名前は変えないで上書き)

② CvPcbで、再関連付けを行う。修正シンボルのみフットプリントの関連付けが消えているので再割付して回路図共にセーブ。

③ ネットリストを再生成

④ PcbNewを開く

⑤ 自動的に読み込むが、最初に読み込むファイルは、どうも修正前のリストのようで、修正前のラッツネット状態になっている。

⑥ そこで、再度読み込むと修正後の状態になる。

※ 本来説明によると、最初から修正したリストを読み込むはずなのに? バグかもしれない?

・ベタグランド生成作業 181001

今回は、GNDの島と、GNDAの島 2つ作成しないといけない。

注意点を以下にまとめてみた。

① Isolateは、tutorialの説明例では、クリアランスと称して[0.35mm](0.014インチ)だが、

ちょっと狭いので、Eagleで設定していた自分で決めた、[0.6096mm](0.024インチ)に変更。

と思ったが、tutorialの説明例と同じに狭めてみる。(上がってきた基板を見たが特に違和感はなかった。)

→ クリアランスの設定値は、パッドに対しては、パッド周囲クリアランスの合計がこの値になることに注意。

ラインに対しては、そのものの値がクリアランスになる。

② GNDと、GNDAの境界線間隔は、1.1mmとすること。fusion規格では0.8~1.0mmはクリアランスエラーになることをeagle時確認済。

③ グリッドを0.5000mm(19.69mils)にし、外形線の内側0.5mmにベタグラウンド領域を描きます

④ C20-マイナスピン:GNDと、U5-27:GNDAピンは、島から離れたところに位置するので、ここは近くのピンに

手配線でライン配線する。

その際のライン幅は、0.4mm(15.75mil)とする。

これは、Eagleの時の電源ライン中太の、16mil(0.4064mm/0.016inch)に相当。

KiCadの、標準ラインアップには、16milが無いため、これを使うことにした。

・freeroute.jarについて 181004

何も指定しなければ、配線幅は、0.2mmで引かれるので、デジタル配線には都合がよい。

<追記:181006>

・v5では、「フットプリントの自動配置」や「フットプリントの自動展開」など一部のコマンドは

デフォルト状態では使用できなくなりました。

<ガーバ作成作業:181006:「JA3OOK」

中村さんサイト記事より>

・設定ダイアログの『シルクをレジストで抜く』をチェックすると、半付けしたい箇所にシルク文字がある

場合にシルク文字を消してくれて半田付けができるようになるようだ。

(半田箇所とシルク文字が重ならない設計ならチェックしてもしなくても同じこと)

■ 2018.9.12

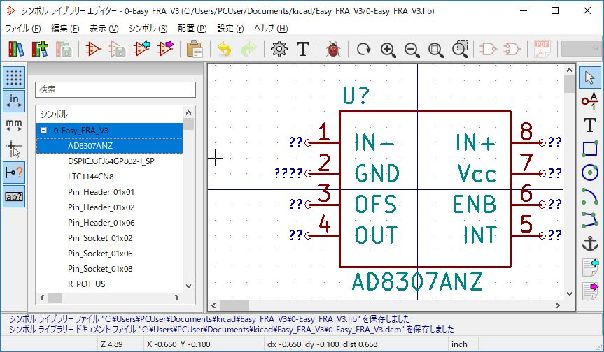

※1 続き DSPIC33FJ64GP802-I/SP(DIP28)のフットプリントから。

28pinICソケット使用:D(幅方向のピン間ピッチ)= 300mil= 7.62mmタイプ→ 標準にあった。

Package_DIP-DIP-28_W7.62mm_Socket

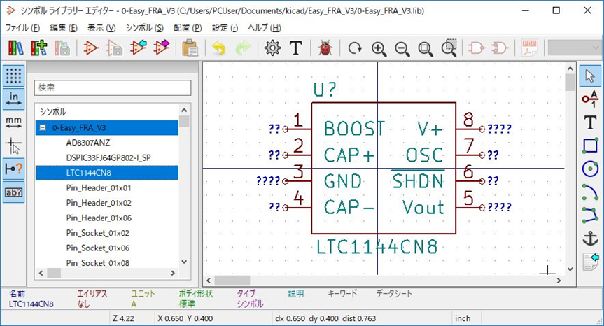

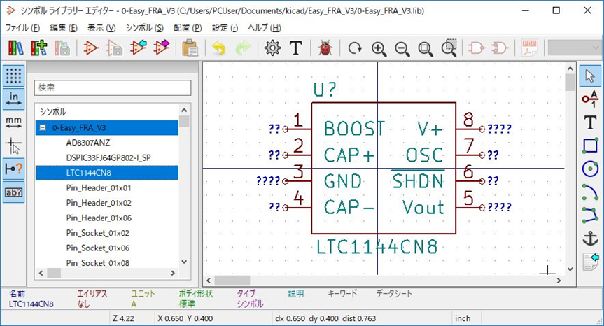

② LTC1144CN8(DIP8)

KiCadには標準シンボル無し。

新規作成することにした。

8pinICソケット使用:D(幅方向のピン間ピッチ)= 300mil= 7.62mmタイプ→ 標準にあった。

Package_DIP-DIP-8_W7.62mm_Socket

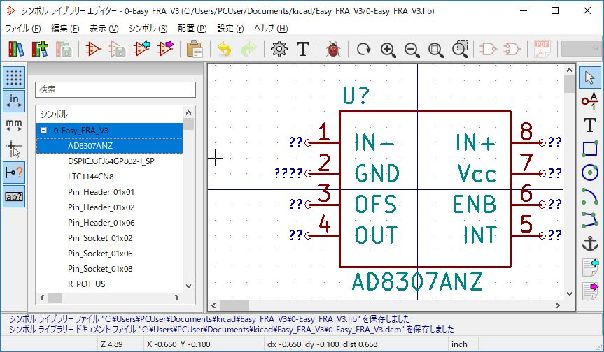

③ AD8307ANZ(DIP8)

KiCadには標準シンボル無し。

新規作成することにした。

8pinICソケット使用:D(幅方向のピン間ピッチ)= 300mil= 7.62mmタイプ→ 標準にあった。

Package_DIP-DIP-8_W7.62mm_Socket

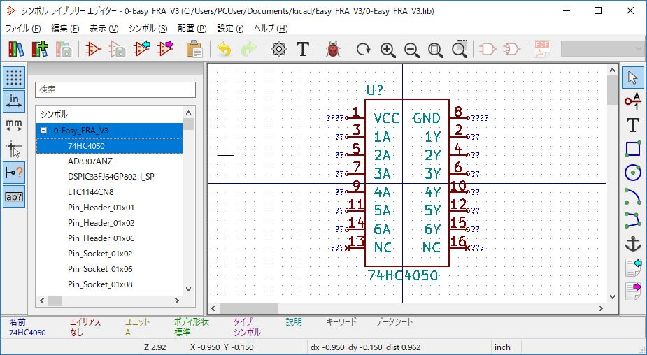

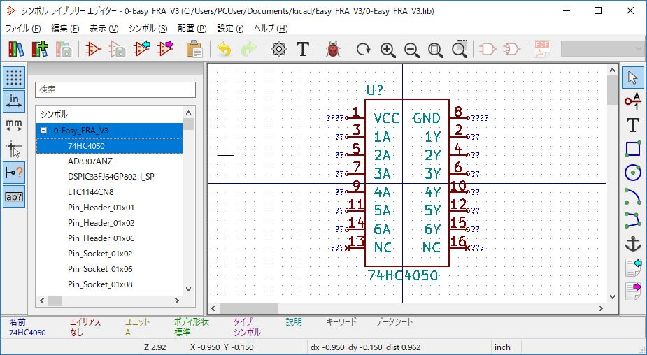

④ 74HC4050(DIP16)

KiCadには標準シンボル無し。

新規作成することにした。

16pinICソケット使用:D(幅方向のピン間ピッチ)= 300mil= 7.62mmタイプ→ 標準にあった。

Package_DIP-DIP-16_W7.62mm_Socket

⑤ LMC6482(DIP8):1パッケージ3個

KiCadには標準シンボル有り

KiCad標準シンボル:Amplifier Operational-LMC6482(LM2904のエイリアス:複製?としてあった)

■ 2018.9.13

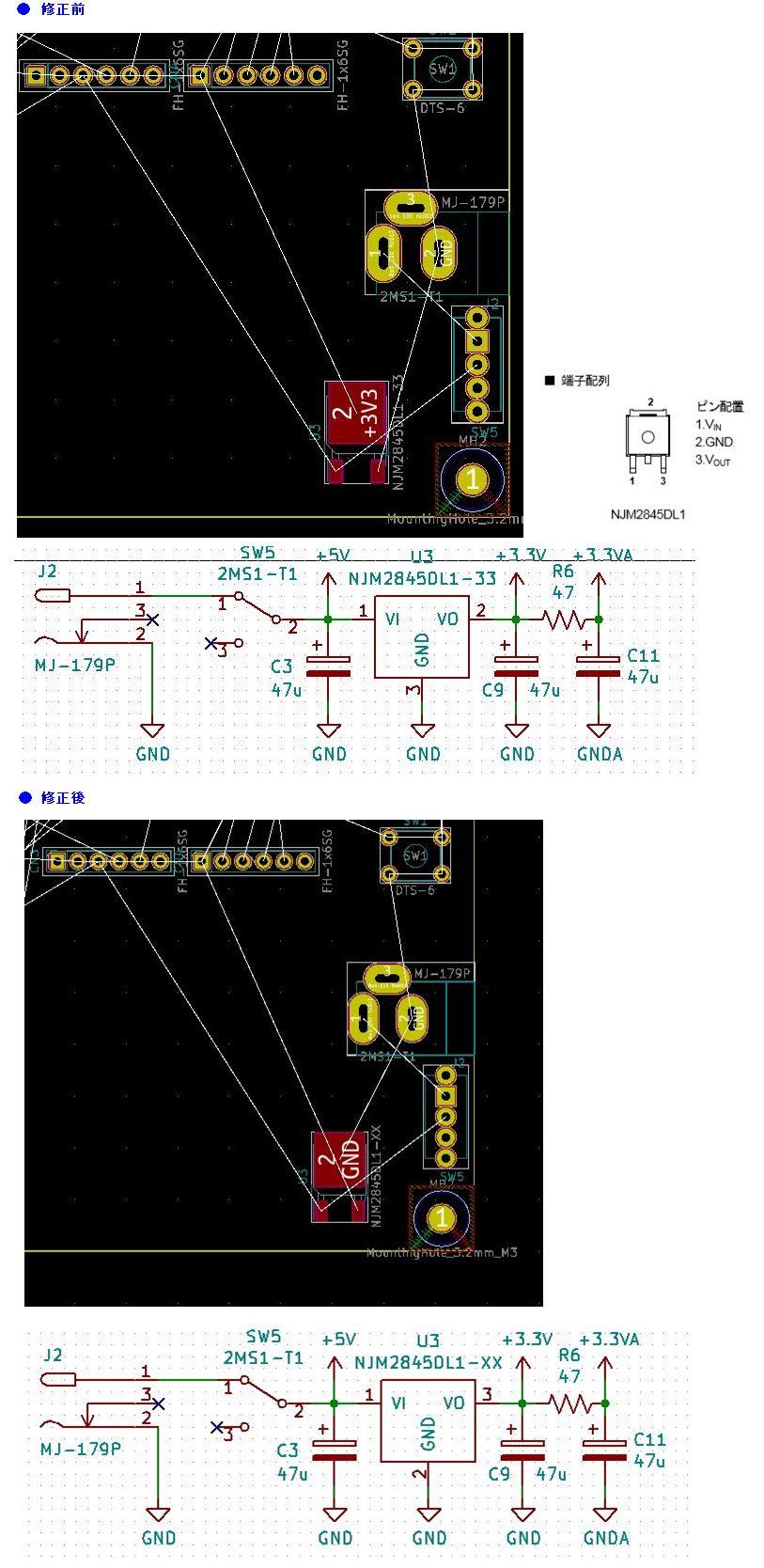

※1 続き NJM2845DL1-33(TO-252-2)から。

⑥ NJM2845DL1-XX(TO-252-2)

KiCadには標準シンボル無し。

新規作成することにした。

Package_TO_SOT_SMD-TO-252-2→ フットプリントは、標準にあった。

⑦ グランドシンボル→ gndフットプリントは、無い。(考えなくてよい)

次の、標準シンボルをつかうことにした。(どちらも同じ形なので、valueは表示しておく必要がある?)

・デジタルgnd:power-GND

・アナログgnd:power-GNDA

⑧ VCCシンボル→ vccフットプリントは、無い。(考えなくてよい)

次の、標準シンボルをつかうことにした。(どちらも同じ形なので、valueは表示しておく必要がある?)

シンボルの形としては、↑マークか、テストポイントみたいなマークしかないので、↑マークの方にした。

・+5v:power- +5V

・+3.3v:power- +3V3

・+3.3va:power- +3.3VA

➈ 積層セラ5mmピッチ:RDER71H105K2K1H03B "村田" 50V1u

DxW= 5.5x3.15mm

実装ピッチP= 5mm

リード径= 0.5φ

ドリル径= 0.8φ

KiCadライブラリ名:Capacitor_THT がDIPのコンデンサライブラリ

|- フットプリント名:C_Disc_D5.1mm_W3.2mm_P5.00mm が使えそう。

Cシンボルは標準を使う。

Device-C

Device-CP

■ 2018.9.14

⑩ 取り付け穴

※ 今回は、ネジ頭を、ベタGNDに落としたいので、回路上にホールを置きGNDに接続してみる。

KiCadライブラリ・シンボル名: Mechanical-MountingHole

KiCadライブラリ・フットプリント名: MountingHole-MountingHole_3.2mm_Pad_Via

↑

と思ったが、今迄通り、ホール周辺のネジ頭径+α分は禁止帯設定にしてやってみる。

自分で、KiCadに於ける、禁止帯設定の方法を模索してみたが、どうも禁止帯を丸で描くことは難しいのか?

出来ないようだ?

矩形の禁止帯でも問題ないのでそうしてみる。

なので使うマウンティング・ホールのフットプリントは→ Mounting_Hole-Mounting_Hole_3.2mm_M3

→ 追記:181006

禁止帯を丸で描くことは難しいのか?

ベタ生成まで取り付け穴を置かないで、ベタ生成後取り付け穴を置き再度「全てのゾーンを塗りつぶす」を行

えば取り付け穴周辺のベタパターンを消すことが出来る。(「iw回路設計」さんの、「基板作製プログ」より)

次回から試してみる。

■ 2018.9.15

※1 今日は、プロジェクト・シンボル・ライブラリ:0-Easy_FRA_V3.lib への使用パーツシンボルの登録から行う。

■ 2018.9.16~ 2018.9.18

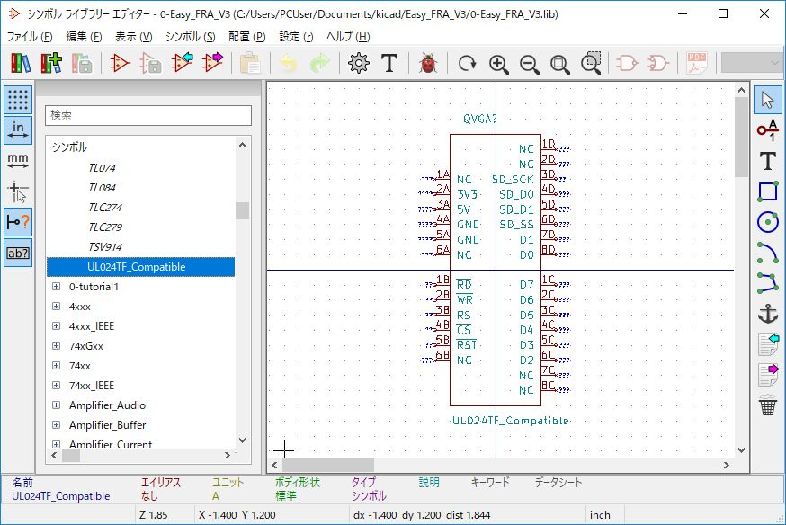

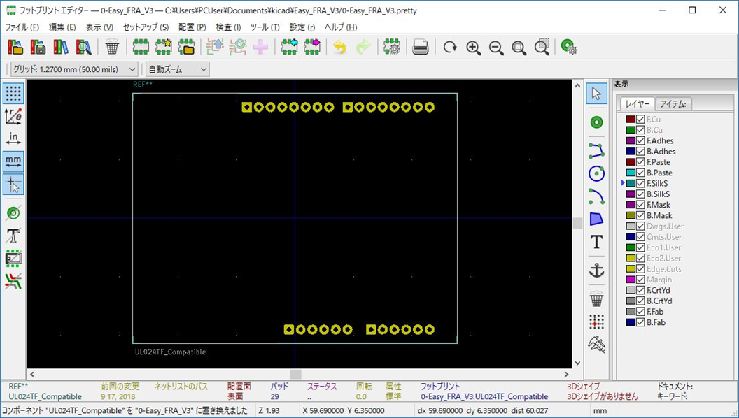

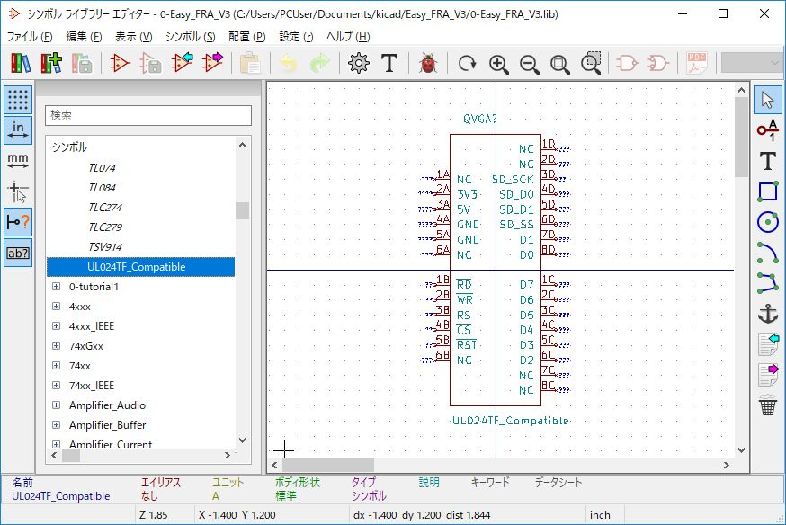

※1 2.4inchQVGAの、フットプリントを作ってみる。

コネクタを単に4つ並べる方法だと、位置決めが面倒なので、どうにかしたいと前から思っていた。

コンポーネントモジュールとして登録すれば、CAD画面上で、他部品との位置関係が直感的に解りやすくなる。

問題はシルク線をどうするかである。

QVGAブレイクアウトボードの下で、他の部品を実装する可能性が殆どないところのみに、アウトラインを引くことにした。

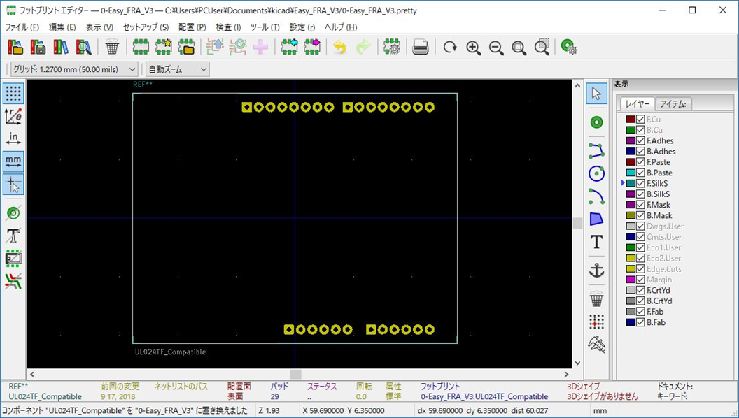

フットプリント名及び、シンボル名は同じにした:UL024TF_Compatible

ブレイクアウトボードは、JA1WBYさん作の、LCD-ADP-V2を使う前提で、寸法取りを行う。

※2 プロジェクト・フットプリント・ライブラリ:0-Easy_FRA_V3.pretty への使用フットプリントの登録保存を行う。

これには、取り付けホールも含む。以下にシンボルとフットプリントを示したが、結果的には何故か上手く行かなかった?

■ 2018.9.19~ 2018.9.20

※1 回路図作成開始

■ 2018.9.21~ 2018.9.22

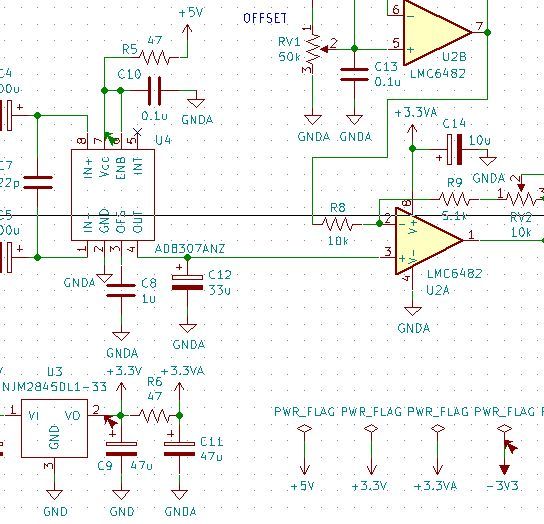

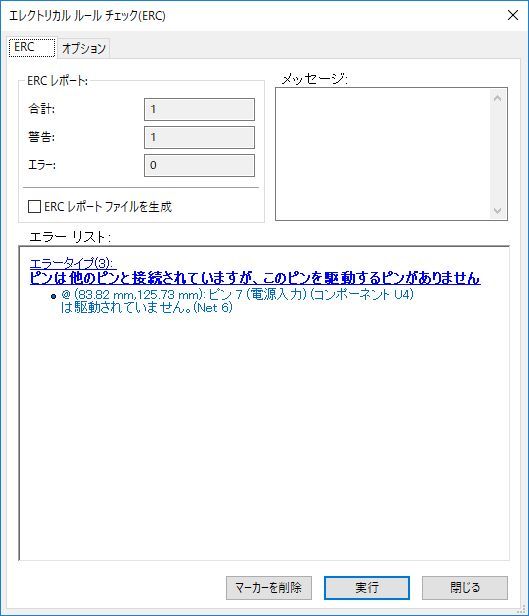

※1 回路図作成続行~ERC~NET LIST

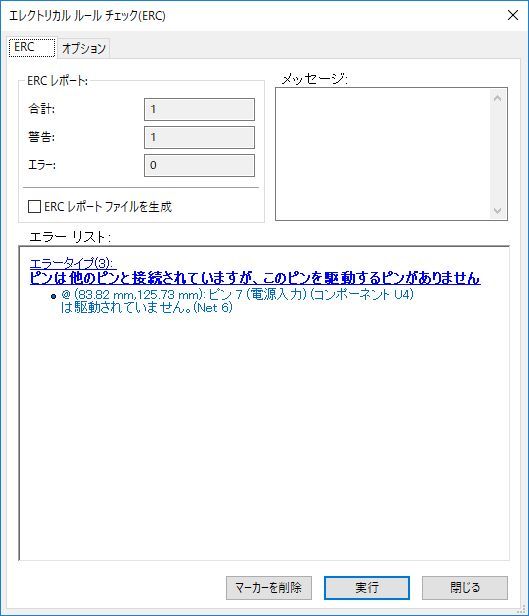

※2 ERC

(1) 最初のERC結果

① 警告:3点

・U4-7:電源入力ピンは駆動されていません。

→

5V入力ではなく、抵抗を介した電源供給のため。

意図的なので承認

・U1-3:入力ピンが、ピンヘッダのピンに繋がっているが駆動されない?

→

ピンヘッダのピンの属性が、入力になっている為。

これは自作したがコネクタのピン属性は、通常「パッシブ」(受動)

にするので修正。(今回新規作成したコネクタ全て修正)

・SW5-3:パッシブピンに、何も接続されてない?

→

単純ミス:'X^-"マーク忘れ

② エラー:2点

・3端子REG-VOピン

3.3V出力が、POWER

FLAG:電源出力に繋がっている?

→

これも新規作成したコンポーネント

3端子REG-VOピン

の属性を、単なる出力にしたため。

電源出力に修正。

ちなみに、REGの、VIピンも単なる入力にしてたので修正

また、GNDピンも同様に修正

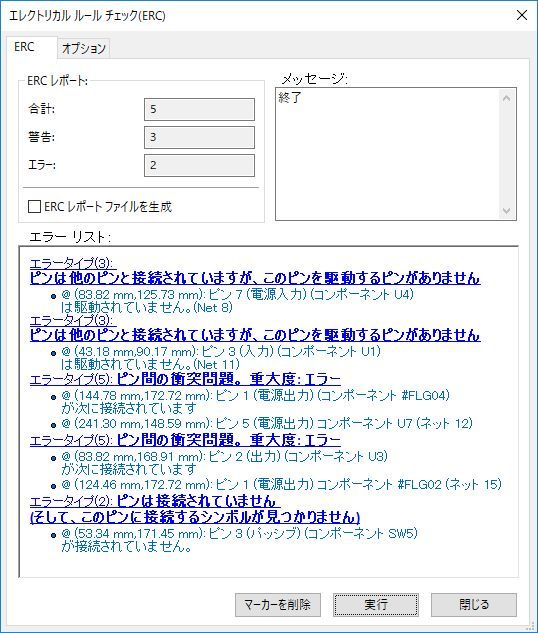

(2) 未だエラーになる。

修正後のERC

※

どうも、POWER

FLAGピン属性:電源出力に対し、相手のピン属性が

電源出力になっている場合に、出力衝突でエラーを出しているようだ。

そもそも、POWER

FLAGは、電源シンボル(ピンは電源入力)が、ERCに電源ラインに繋がっていることを

知らしめる為に使っているだけと考える。

試しに、エラーが出ている、3.3V(REG出力)と、-3.3V(LT1144出力)だけ、

POWER

FLAGピンとの接続の部分を削除すると、このエラーは消える。

だが、ネットは正しく繋がっている。(ハイライトで確認)

なのでこれであとネットリストをチェックして問題ないようだったら先に進めてみる。

・-3.3VLT1144-VOピンが、POWER

FLAG:電源出力に繋がっている?

→

これも上記と同様な考えで進めてみる。

※3 フットプリント割付け(関連付け:CvPcb)

※4 ネットリスト生成

■ 2018.9.23

※1 ネットリスト生成

心配していた、+3.3Vと、-3V3ネットだが、正常に繋がっていた。

また、OP AMP分かち書き部分のネットもOKだった。

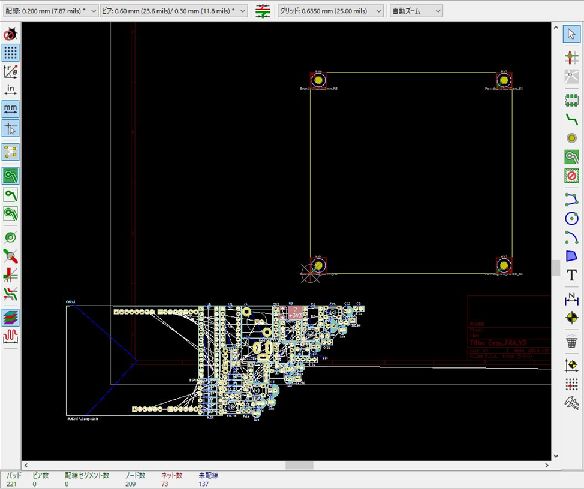

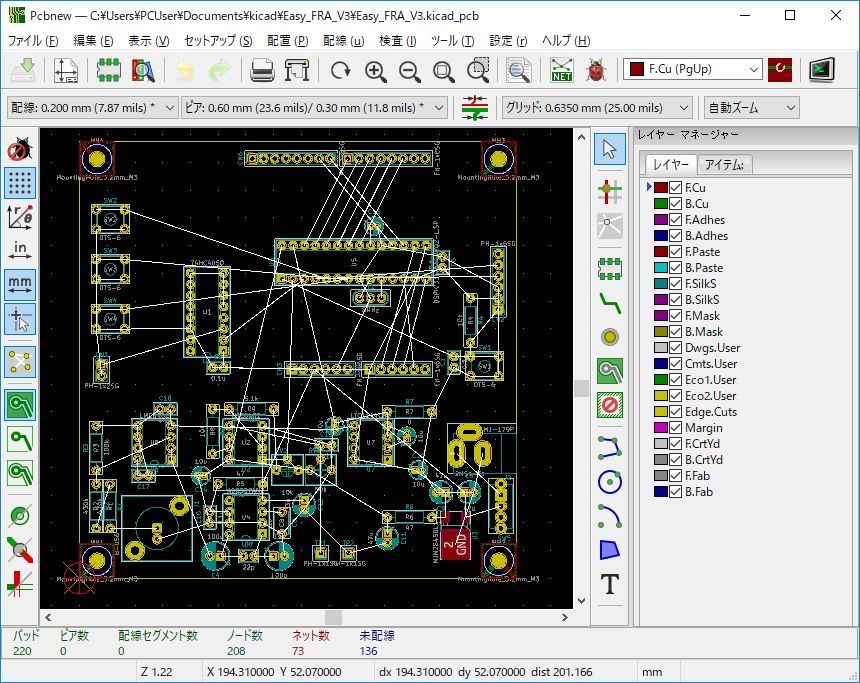

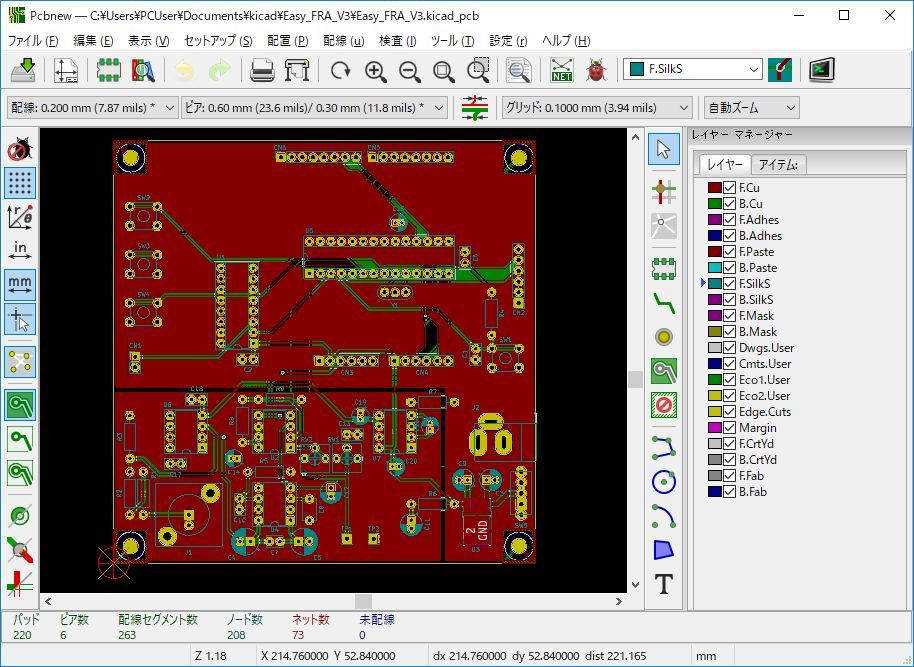

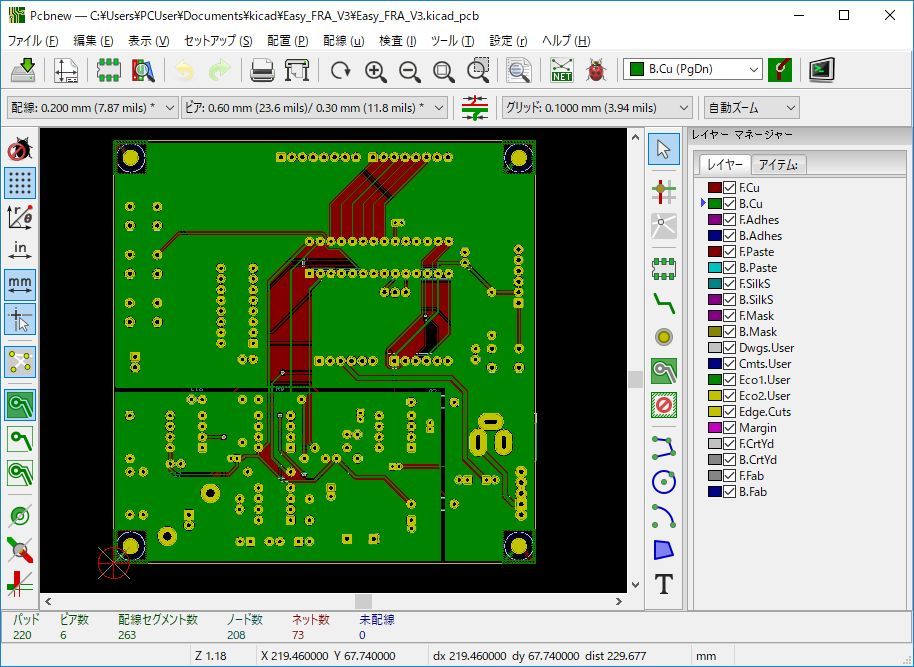

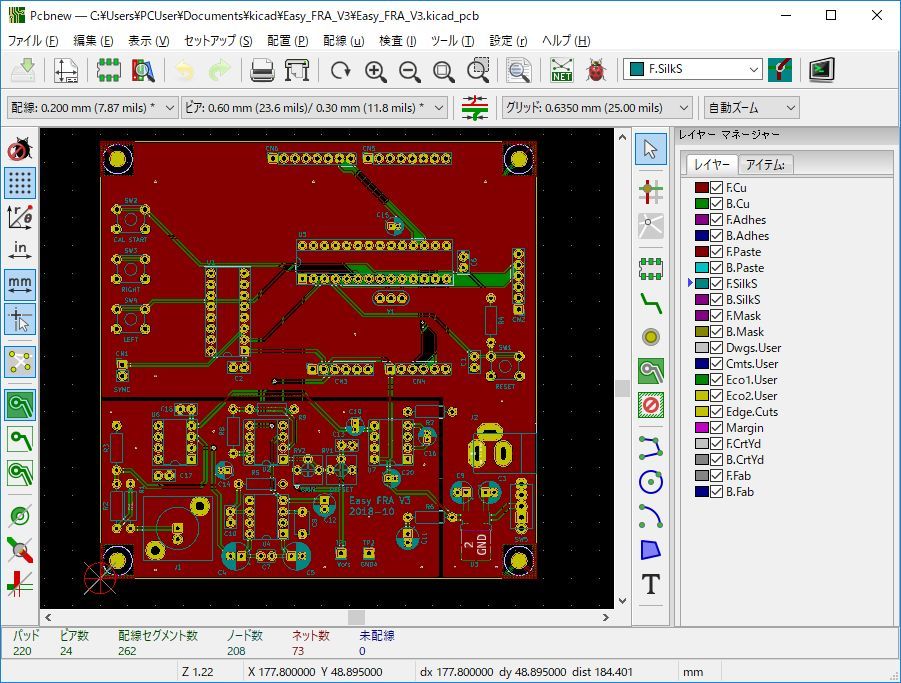

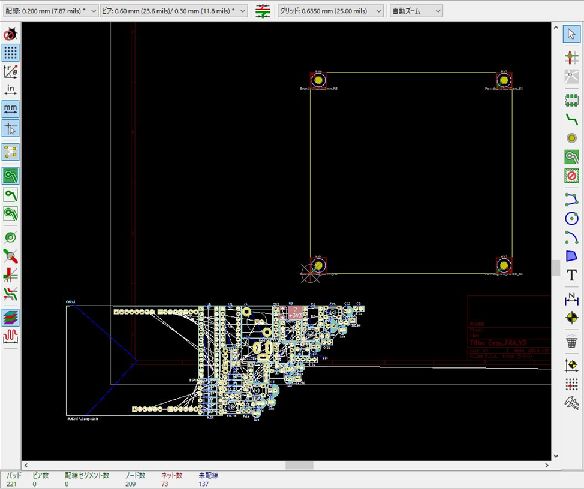

※2 基板レイアウト設計:PcbNew 開始

① 基板外形レイヤは、Edge.Cut

② 外形+取り付け穴+禁止帯

③ ネットリスト読込み(グリッド=0.635mm(25mil)

読込んだら、塊が現れたが、何故か、U5-12:RST/(→ QVGA1-5Bに繋がるだけ)

だけ余計な行先が無い長いラッツネットが表示された。(小規模なtutorialの時は、この現象起きてない)

→ 回路図上でも、ネットリスト上でもネットを確認したが、余計なところのネットは無いことを確認した。

また、ネットリストを読込んだ時点でのエラーが無いことも確認済。

→ 試しに、QVGAを移動してみたが移動中は余計なネット消える。→ 勘違いだった。移動しても一緒に付いてくる。180926

→ 試しに、回路図に戻って一度、RST/のネットを削除後、再配線してセーブ。

この状態で、ネットリストを再生成。(再生成後、RST/ネット正常を確認)

これを読込んでも同じだった?

→ ネットリスト上の、ネット総数(net (code **) **の最終番号= 72なので、ネットリスト上の、ネット総数=72

ところが、レイアウトエディタ上でのネット総数は、ネット数= 73と一つ多い。→ ネット000が含まれるからだと考えるが、意味不明。180927

あと、ネットリスト上の、net code番号と、レイアウトエディタ上でのネット番号は一致しない。

~RTSネットは、net code= 52/ネット番号= 43

行先の無いラッツネットは何故発生したか不明

無視してもよいかはわからず?

■ 2018.9.24~ 2018.9.25

※1 昨日の問題未解決?原因不明?→ 試行錯誤したが、ボードデータは、外形+取り付け穴+禁止帯の状態から、ネットリストを

読込んで、塊を確認しているだけで、保存はしてない。ボードデータは、外形+取り付け穴+禁止帯の状態のまま保持。

<疑問点整理:PcbNew>

① メニューに[検査]-ネット数というのがある。

net listを読込む前に、これを実行しても、最初から、ネット数ダイアログに

ネット名 パッド数

[ネット000][ ][---] が表示される。

これは何を意味するのか?

② また □ ゼロパッドネットを表示のチェックボックスは、チェックが入っているが、これを無しに

して[ok]し、再度このダイアログを開いてもチェックが入ってしまう?このネットを非表示にはできなものか?

※2 何かとwebに、KiCad V5 の情報が少なく、疑問点が解決できないが、たぶんnet listに行先のないネットは

含まれてないので、このまま進めてもokだと思うが・・・

たとえ駄目でもトレーニングと割り切って、ガーバー前までは進めようかと思っている。

→ いや駄目そう。

[検査]-ネット数で、当該ネットのパッド数を見ると、3になっている。

ハイライト表示で見えているのは確かに、2なのに? 行先のないネットの先にパッドは見えない?

※3 これと並行して、この件web上で質問出来ればと思っている。

KiCadのユーザーコミュニティというサイトがある。

KiCadme-メーリングリスト にアドレス登録中(待ち)

■ 2018.9.26

※1 [検査]-ネット数で、当該ネットのパッド数を見ると、3になっている。

ハイライト表示で見えているのは確かに、2なのに? 行先のないネットの先にパッドは見えない?

→ 3つ目のパッドが何処かに存在するのだろうか? 実際見えないが?

もしかしたら、QVGAのフットプリントの当該パッドの下にダブルでパッドが重なっているのか?

そんなことだとしたら作成時エラーが出るはずだが?

エディタを開いて確認してみたが重なってはいなかった。

※2 KiCad V5の、リファレンスマニュアルを探したが、NET上に存在しない。

KiCad V5 メニューのヘルプからリンクされているのは、2014年3月17日 発行の、V4のもので古い。

日本語翻訳版で詳細に説明されているので手掛かりになると思ったが・・・・

※3 これまで、PcbNewでネットリストを

読込んで、塊を確認しているだけで、保存はしてない。ボードデータは、外形+取り付け穴+禁止帯の状態のまま保持。

※4 新規作成したフットプリントが悪さしているのかと思い、ネットリスト読込後、同じダイアログ上の[フットプリントをチェック]

をクリックしてみたところ異常なさそう。

・重複はありません。

・欠落したフットプリントはありません。

・取り付け穴はネットリストに含まれません。

※5 ネットリストをもう一度確認してみた。

[~RST]で検索して余計なネットが無いか再確認→ 以下の結果の通り異常なさそう。余計なネット(パッド5Bピン)は無い。

フットプリントの当該ピン割り付けもよさそう。

なのに、PcbNewのボード上では、不要と見えるラッツネットがウインドウの端まで伸びていて、そこにはパッドなどない。

これは何を意味するのか不明だが、折角ここまで来たので、ガーバー前までは作業を進めて様子を見ようと思う。

結果駄目でも、最初なのでトレーニングと割り切ることにした。

<結果>

(libpart (lib 0-Easy_FRA_V3) (part UL024TF_Compatible)

(fields

(field (name Reference) QVGA)

(field (name Value) UL024TF_Compatible))

(pins

(pin (num 5B) (name ~RST) (type input))

(nets

(net (code 52) (name ~RST) → この52番ネットは、ここにしか出てこない。ダブりはない。

(node (ref QVGA1) (pin 5B))

(node (ref U5) (pin 12)))

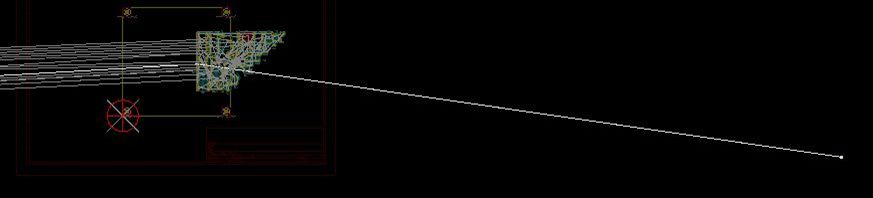

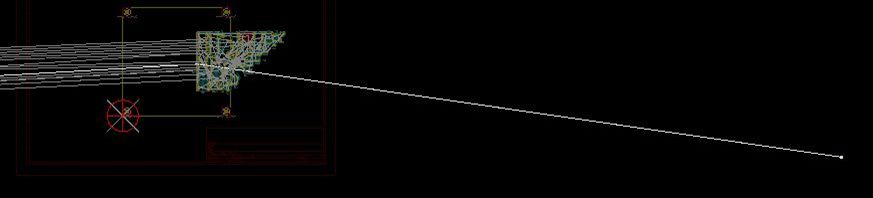

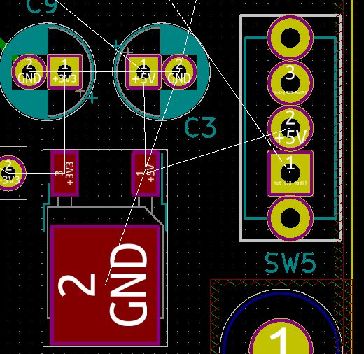

※6 少しだけ調査進展。

3つ目のパッドが何処かに存在するのだろうか? 実際見えないが?

と思っていたが、QVGAシンボルを思い切ってウインドウ最左端に移動したら、当該ネットは右端に移動した。

これで右にスクロールして追っていったら、何と独立した、RSTパッドが、そのネットに繋がっていることを発見した!!

しかし何故こうなったかは不明。

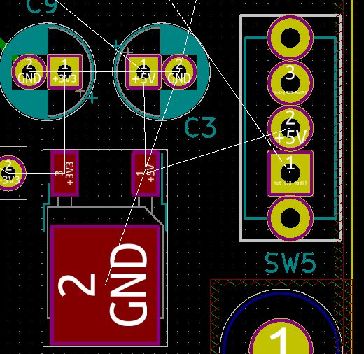

※ 上画像をクリックすると、余計なパッド部が拡大されます。

※7 ネットリスト読込時、ダイアログに進捗情報が都度出力される。

このレポートファイルを保存してあったので、QVGA1-5Bパッド:~RSTのところを検索チョイスして確認してみた。

以下の結果の通り、何故か、パッド "5B" のネット名を "" から "~RST" に変更

が2回出てくる。これがダブり??

最後のパッド "5B" のネット名を "" から "~RST" に変更は本来出てきてはいけないはず。

<QVGA1-5Bパッド:~RSTのところを検索チョイス>

・情報: ネットリスト、シンボル、フットプリント "QVGA1:/5BA1F133:0-Easy_FRA_V3:UL024TF_Compatible" をチェックしています。

・プットプリント "QVGA1:/5BA1F133" パッド "5B" のネット名を "" から "~RST" に変更しています。(←動作レポートになる。)

・新しいシンボル "QVGA1:/5BA1F133" フットプリント "0-Easy_FRA_V3:UL024TF_Compatible" を追加しています。(←動作レポートになる。)

・プットプリント "QVGA1:/5BA1F133" パッド "5B" のネット名を "" から "~RST" に変更しています。。(←動作レポートになる。)

尚、エラー・警告メッセージは出力されてない。情報・動作項目だけ出力されている。

※8 余計な3つ目の、5Bピン"~RST"パッドだが、これを削除すると、QVGA1まで削除される。

また、このパッドを移動してもQVGAと一緒に移動するだけで、個別移動しないことから、余計なパッドシンボル(フットプリント)でなく

QVGAのフットプリントの一部とも考えられるが、普通フットプリントに最初からラッツネットが付いてくるはずないので、異常な状態だと思う。

■ 2018.9.27

※1 普通フットプリントに最初からラッツネットが付いてくるはずないので、異常な状態だと思う。

ちょっと理由・原因が解らなくなってきた。

※2 これまで、PcbNewでネットリストを

読込んで、塊を確認しているだけで、保存はしてない。ボードデータは、外形+取り付け穴+禁止帯の状態のまま保持。

なので、シンボル・フットプリントの修正をして再関連付け後、再ネットリスト生成して読み込んでも問題ないはず。

※3 気になるのは、エラーは出ていないが、QVGAのピン番号・パッド番号の振り方である。

グループ分けするため、1A・・・ 1B・・・1C・・・ 1D・・・のように振っていたが、規則では、列挙の頭の文字はアルファベットで

その後番号のようだ。(A1・・・ 既存のシンボル・フットプリントで確認。尚、ピン名は自由のようだ。)

この辺が関係あるかもしれない。

らちがあかないので、上記を試してみる。

現在のシンボル・フットプリントは残しておく。

名前を変える。

末尾に、_Rev2を付けることにした。(UL024TF_Compatible_Rev2)

→ しかし・・・と思ったが、何故5BだけNGなのか不可思議。4文字以内の英数字ならOKと説明があった。

その中に、AN0DもOKとなっていたので、5BもOKと思える。これを試すのはやめた。

※4 試行1

回路図上で、QVGA-5B:RST/ピンのネットを削除、U5-12:RST/ピンのネットを削除してNCにし、

ネットリスト再生成してボードに展開しても、QVGA-5B ⇔ U5-12のネットは無くなるが、

相変わらず、QVGA-5Bピンに、長いラッツネットが表示され、その先に5B:NCのパッドがもう一つ現れる。

※5 試行2

QVGAのフットプリントに戻り、5Bパッドを削除して再度置き直しセーブしネットリスト再生成・再読み込みでも同じだった。

※6 試行3

QVGAシンボルやめ、ソケットコネクタに変更したが、CvPcbで関連付けをやり直ししボードで

読み込んだが、関連付けされてないとワーニングが出て、そのコネクタが出力されない。

ネットリストを読み込んだ後、必ずセーブしないとダメなのかもしれない?

方針変更

子規模プロジェクトで、qvgaシンボルのみ確認検証してみる。

→ と思ったが、せっかくここまで進めたので、やはり無駄にしたくない。

※ 試行4

webを見ると、一度回路図に戻って、シンボルを削除、新たなシンボルを追加して回路修正し、再度割付けを行った後、

ネットリストを再出力し、レイアウトエディタで読込んだ時、よくある事象のようだ。

そういう時は、もう一度、回路図に戻って、ネットリストを再々出力すると、読込時のエラーはなくなるようだ。

これを試してみた。(参考サイト:jaco.ec.t.kanazawa-u.ac.jp/edu/vlsi/kicad/05.html)

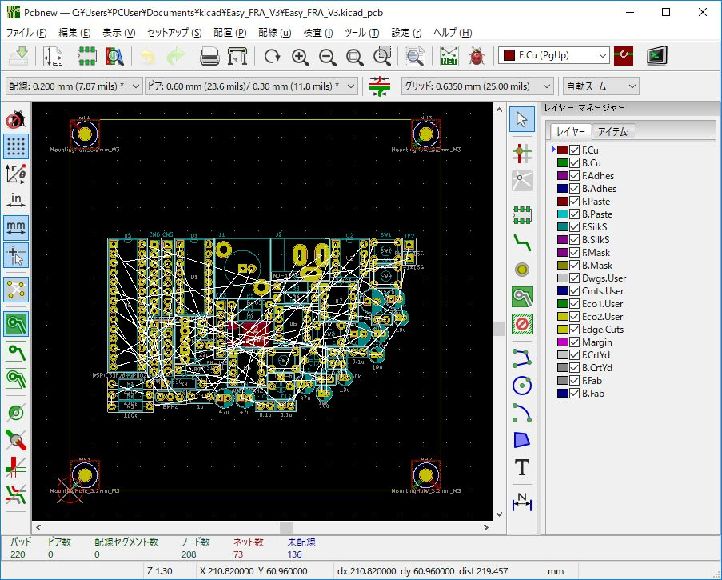

→ 結果、上手く行った!! よかったよかった!!! QVGAのシンボル・フットプリント一体化の問題は次回以降の課題にしたい。

■ 2018.9.28

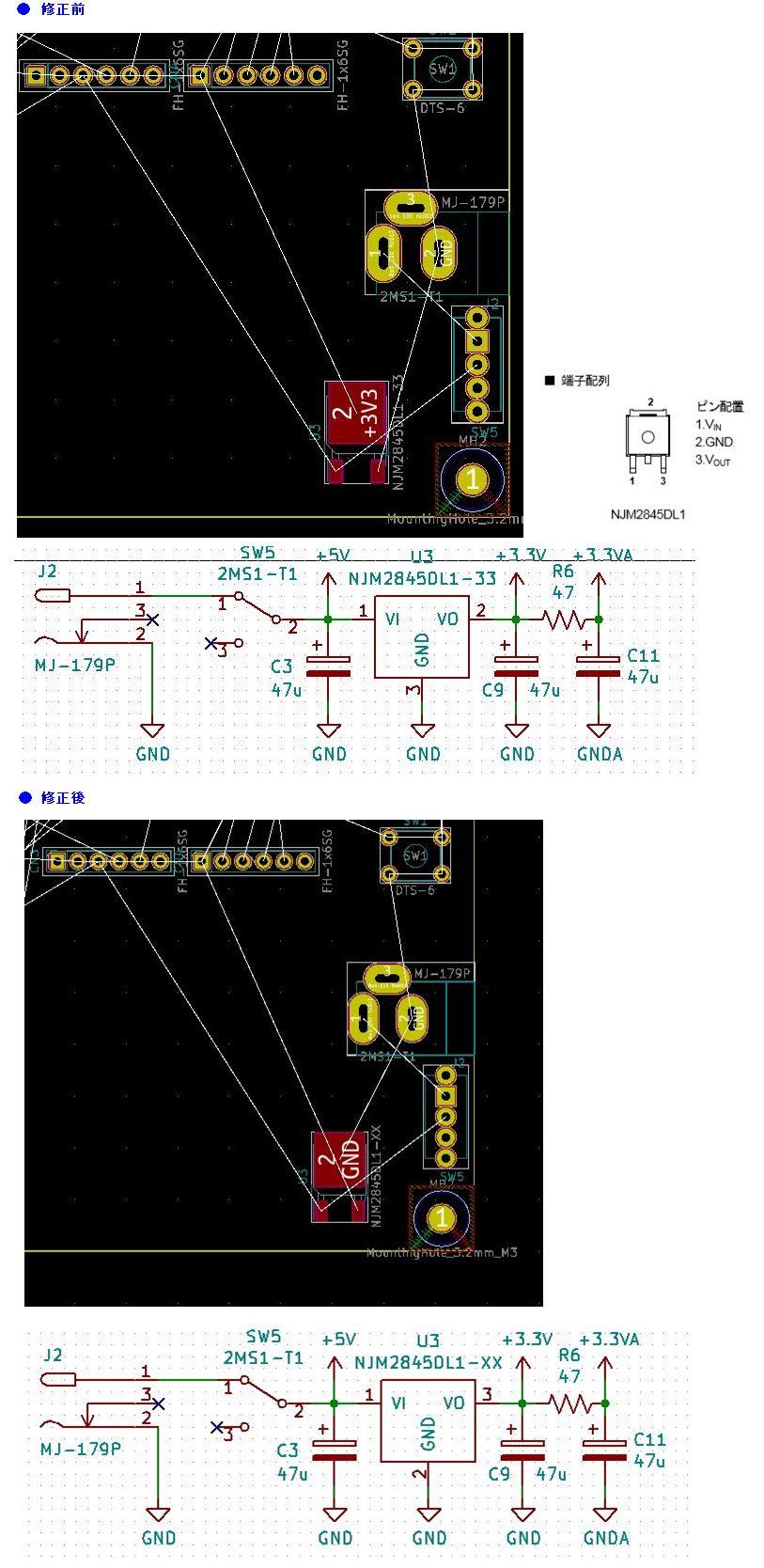

※1 部品配置の途中で、NJM2845DL新規シンボルのピン番ミスに気が付く。(メーカーデータシート上のピン番が基本)

2:VO→ 3:VOが正解

3:GND→ 2:GNDが正解

尚、フットプリントは標準:TO-252-2 で、2pinがグランドタイプを使用でok

なのでシンボルを修正する必要がある。その後、割付けてネットリスト生成

<ミス原因>

Eagleの時は、パッケージは標準のを使っており、2:VO, 3:GNDだった。

シンボルのピン番は、デバイスファイルを生成する時、connectでパッケージとシンボルの信号名の対応割付けを

行うので問題なかったが、KiCadではそのシンボルを見てピン番を振ってしまったのでミスした。

<既に、PcbNew作業進行中に、修正が必要になった場合の処置について調べてみた>

① CvPcb でフットプリントを新しいもの(例えば、1/8W 抵抗を1/2W に変更)に置き換えて基板を修正する場合、

新しいフットプリントをPcbnew が読み込む前に古いフットプリントを削除しておくことが必要です。あるフットプリントを

既存の別のフットプリントに置き換える場合は、置き換えたいフットプリント上でマウスの右ボタンをクリックして“パラメータの編集”

を選び、“フットプリントのプロパティ”から“フットプリントの変更”を使うとより簡単に変更できます。(PcbNewマニュアル July 18, 2018より)

→ 今回の場合、フットプリントは標準:TO-252-2 で、2pinがグランドタイプを使用したが、3pinがグランドタイプ

が標準にあればと思ったが無かった。この方法が安全簡単でよさそうだが・・・メーカーデータシート状のピン番が基本の方針

を崩すことになる。

② 4.3 - プリント基板の更新手順 (プリント基板が生成された後に)回路図が修正された場合、

次のステップを繰り返されなければなりません:

• Eeschema を使用して新規ネットリストファイルを生成します。

• 回路図の修正が新規コンポーネントを含んだものである場合、Cvpcbを使用してその対応するモジュールを割り当 てなければなりません。

• Pcbnewを起動し、修正されたネットリストを再読み込み(モジュール選択情報を含んだファイルを再読 み込み)します。

Pcbnew はその時、新規モジュールを自動的に読み込み、新しい接続を追加し、冗長な接続を削除します。

この処理はフォワードアノテーションと呼ばれ、PCBを作成し、更新する場合の極めて一般的な手順です。

(KiCadリファレンスマニュアル日本語版: 2012年11月18日発行より)

■ 2018.9.29

※1 昨日の②の方法で修正することにした。シンボルのピン番修正を行う。今回は、KiCad標準を使うので

これに合わせシンボルピン番を修正。

→ 修正、上手く行く!!

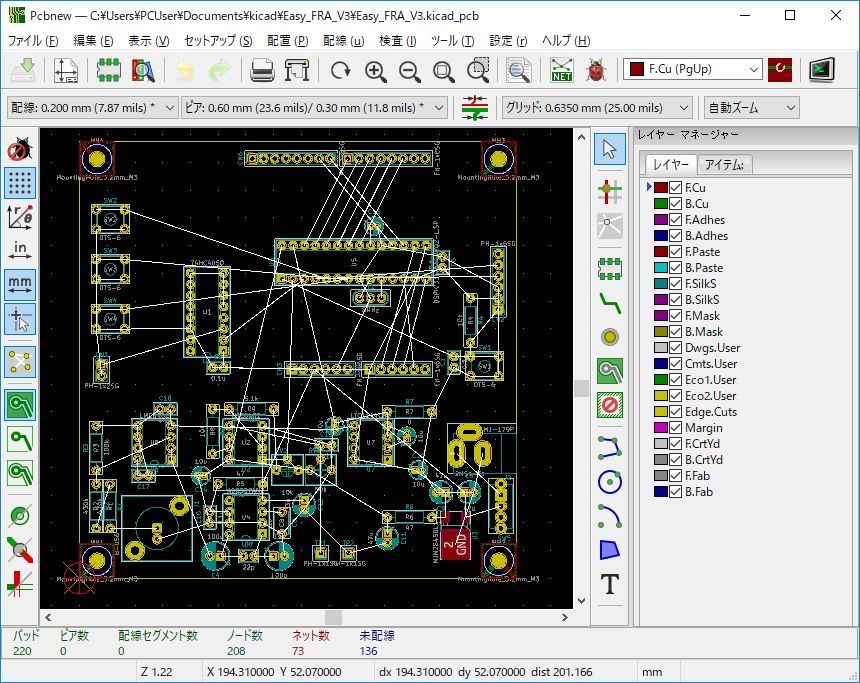

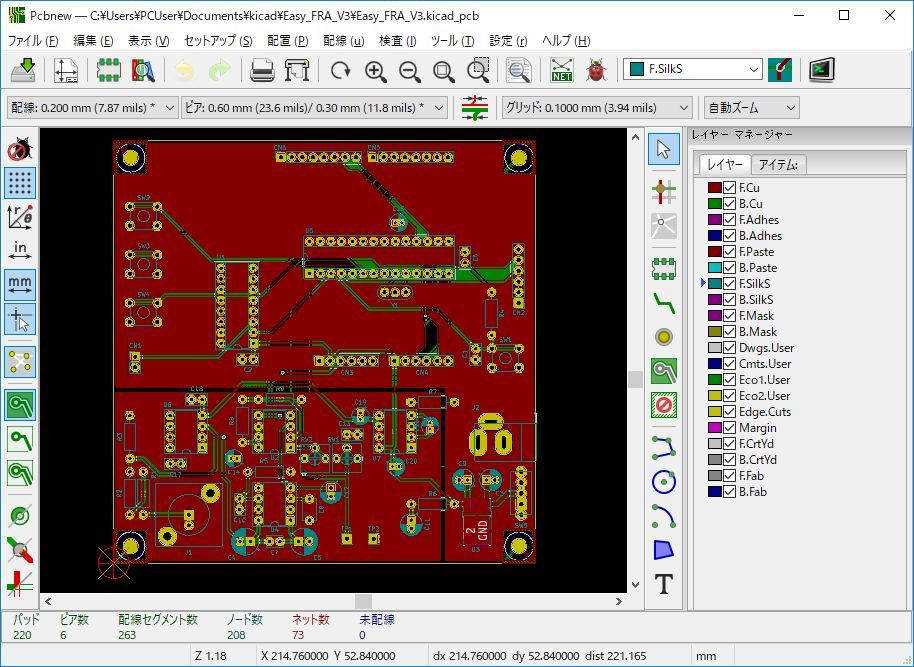

とりあえず、全部品の暫定配置まで終了。

ちょっと心配なのは、GNDと、GNDAのベタが上手く行くかどうか?

位置的にベタから離れているピンは途中まで普通のラインで引いて置けば、ベタ生成時、その先がベタと

繋がってくれると思っているが・・・

■ 2018.9.30

※1 とりあえず、全部品の暫定配置まで終了

ここまでのボード状態を、原寸でプリントアウトし、位置指定部品:QVGAのフットプリントが合っているか

現物と照合してみた。→ OKであった。

■ 2018.10.1

※1 部品定数の非表示 ,部品番号の移動から

※2 ベタ生成まで無事終了

■ 2018.10.2

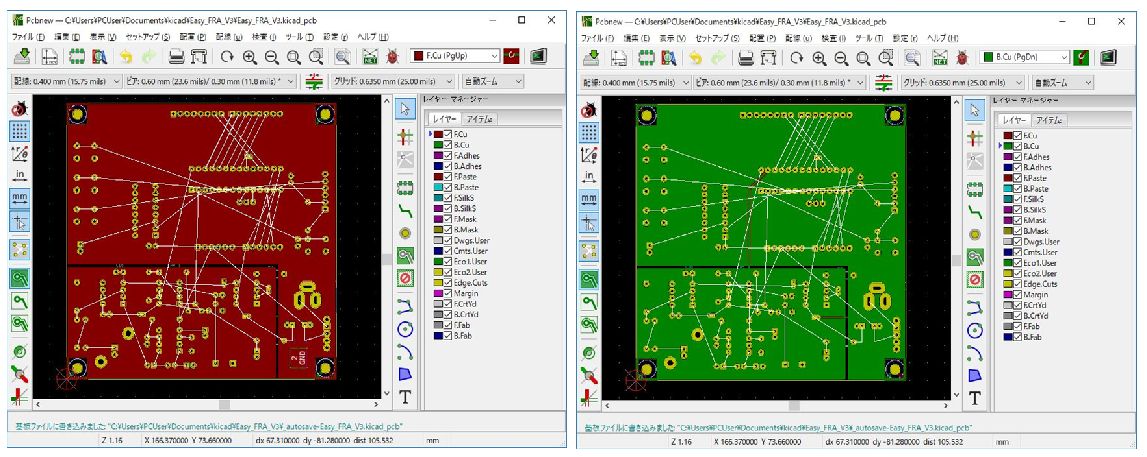

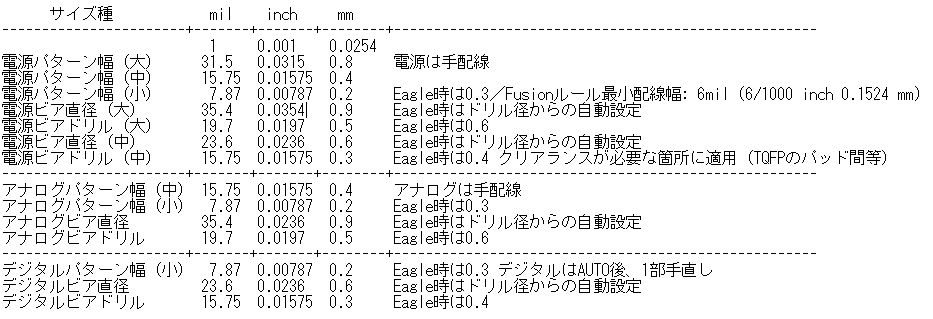

※1 手配線開始前に、

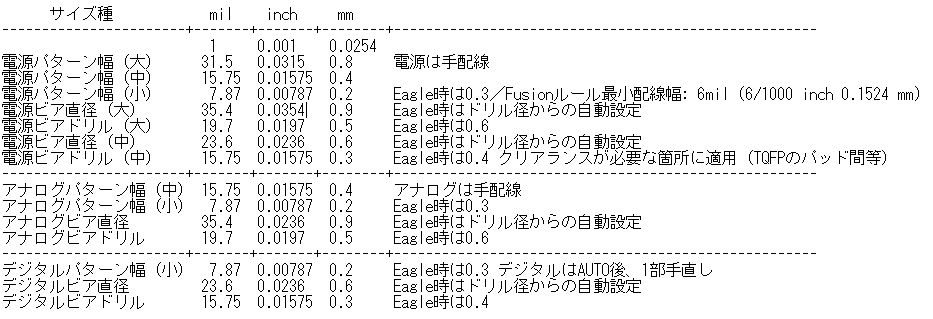

KiCadでの、My パターン幅・ビア径の使い分け設定について決めておく。

KiCad pdf小坂氏の、FusionPcb向けのデザインルールダイアログの設定値に従うことにした。

この設定値がそのまま、レイアウトエディタのプルダウンメニュー(カスタムサイズ)になる。

※2 とりあえず、入力dcジャック周辺の、power swを含めた、+5Vラインを引いてみた。

作業途中で、power swの配置不適当に気が付く。

使ったシンボルは、KiCad標準のもので、eagleの時のものとは、ncピンと、noピンの番号が

逆さになっていることに気が付かず置いてしまったので、レバー上で、offポジションになっていた。

回転させ修正済

■ 2018.10.3

※1 デジタル信号ライン以外の手配線終了

※2 オートルータにてデジタル信号ライン引く。

※3 気に入らない配線修正後、ベタ再確認

■ 2018.10.4

※1 ピア打ち

KiCad pdf小坂氏の説明通り、使用ビア直径=0.6mm(23.6mil)/ビアドリル=0.3mm(15.75mil)としてみる。→デジタルラインのビアと同じ。

(Eagle時は、ビアドリル=0.6096mm(24mil))

※2 配線とビアのクリーンアップ(必要のないもの・違反するものの削除)

必ずベタ表示の状態で行う。さもないと、追加したビアとネットが削除されてしまう。

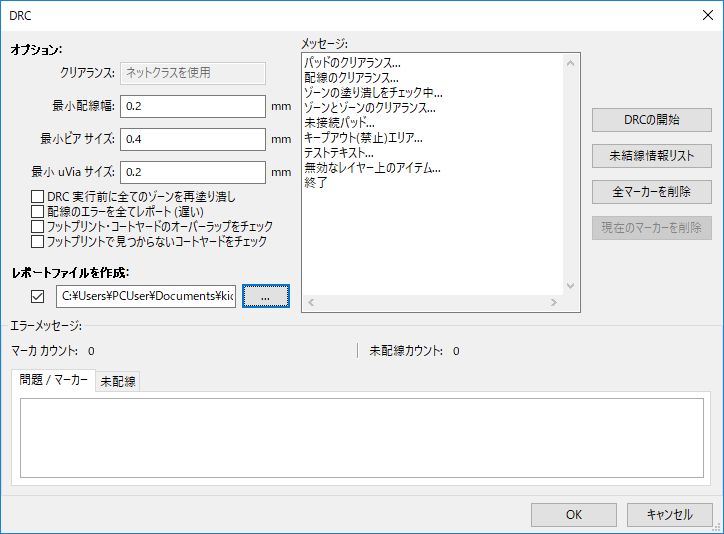

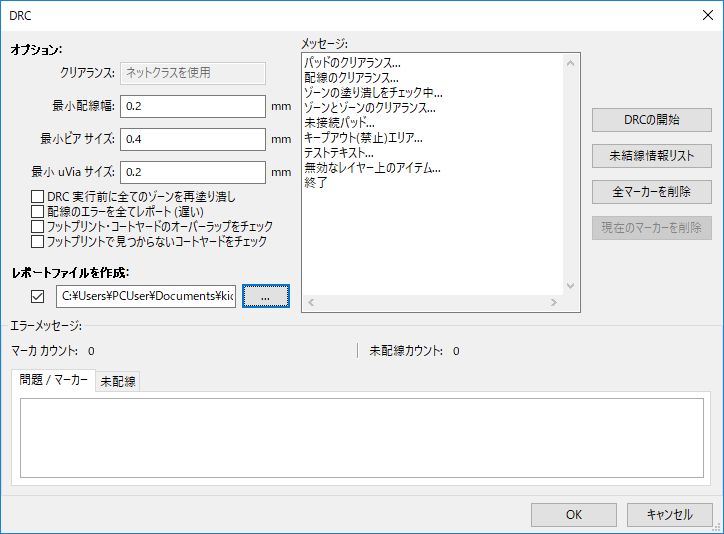

※3 DRC→OK

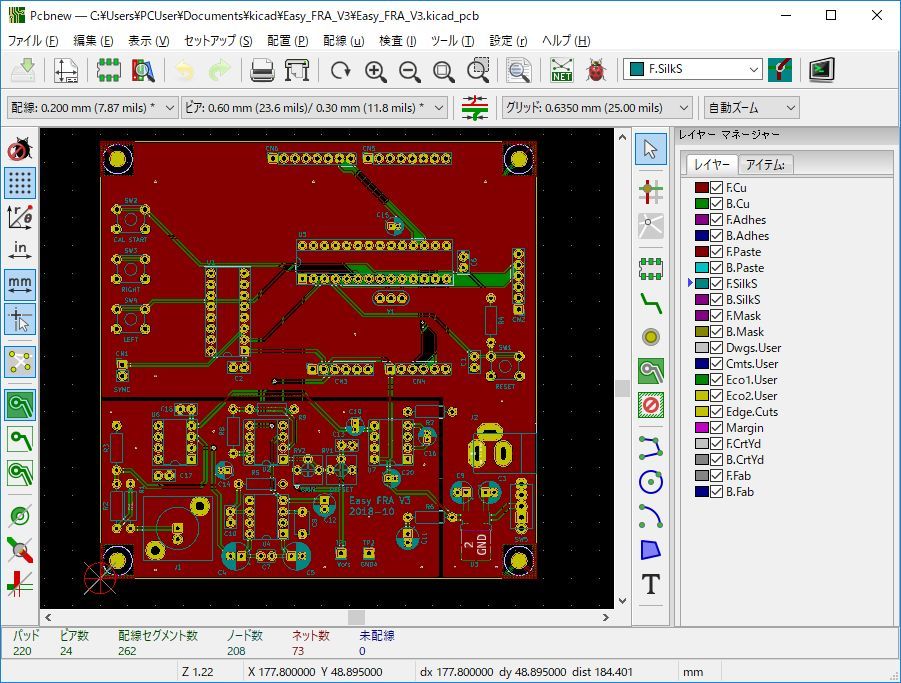

※4 TEXTの挿入とシルク最終整理

Eagle時の字高等設定

Textコマンドで入力

タイトルと日付けは、字高:0.07inch(1.778mm)/ 字体:Vector で入力

その他は、0.05inch(1.3mm)で入力

文字太さ:7mil(0.1778mm)

KiCad時の字高等設定

Textコマンドで入力

タイトルと日付けは、字高:1.5mm/ 文字太さ:0.3mm で入力

その他は、字高:1mm/文字太さ:0.15mm

※5 アーカイブの保存

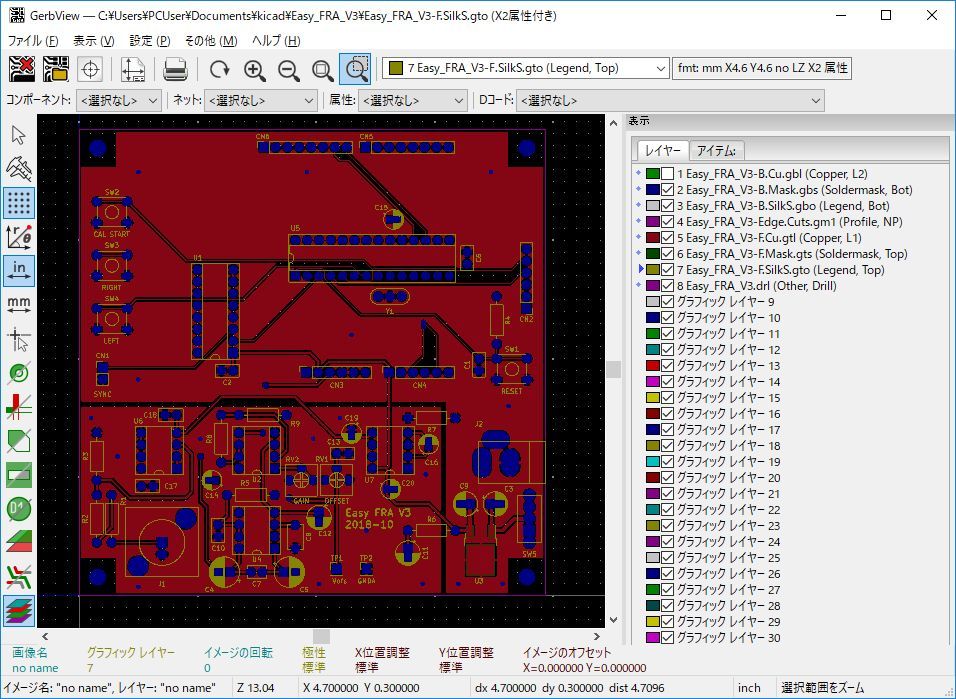

※6 ガーバー出力

単体基板の外形線レイヤは、Edge.Cutsになるので注意(面付の場合は、Eco2.Userになる)

最初間違って、面付の場合の外形線(小坂氏pdf説明例の面付基板の)を読込んでしまっため

基板の外形線が本体から外れた形に表示されたが、後で気付いてEdge.Cutsに修正した。

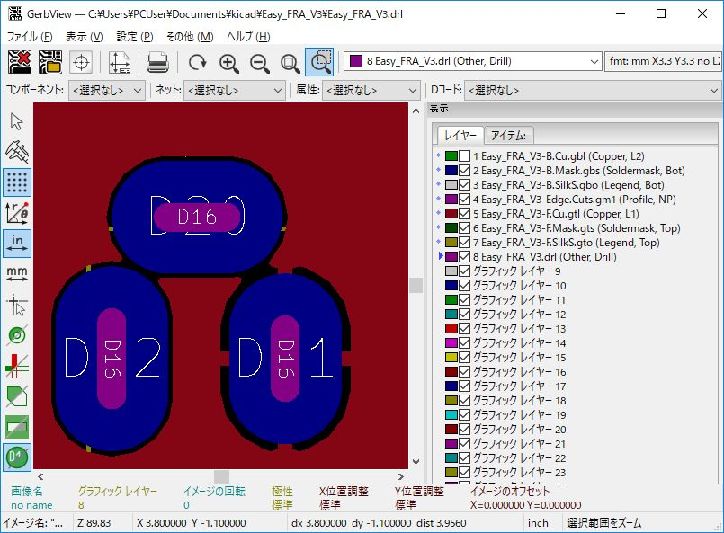

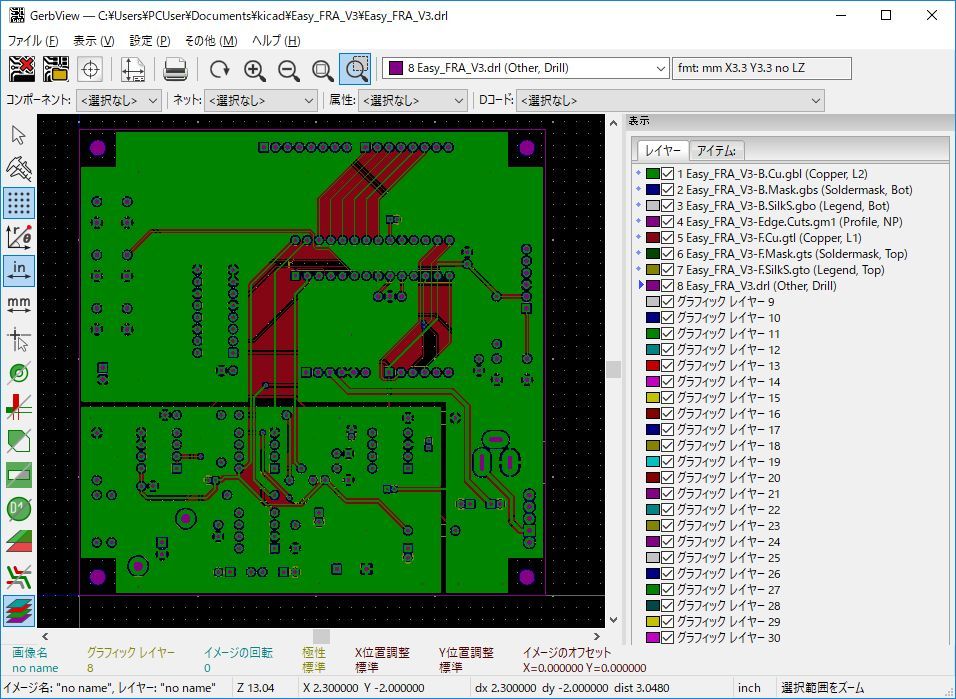

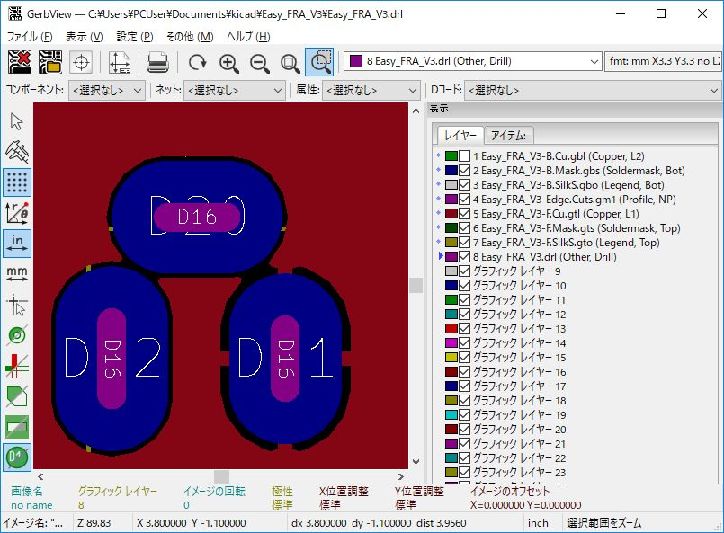

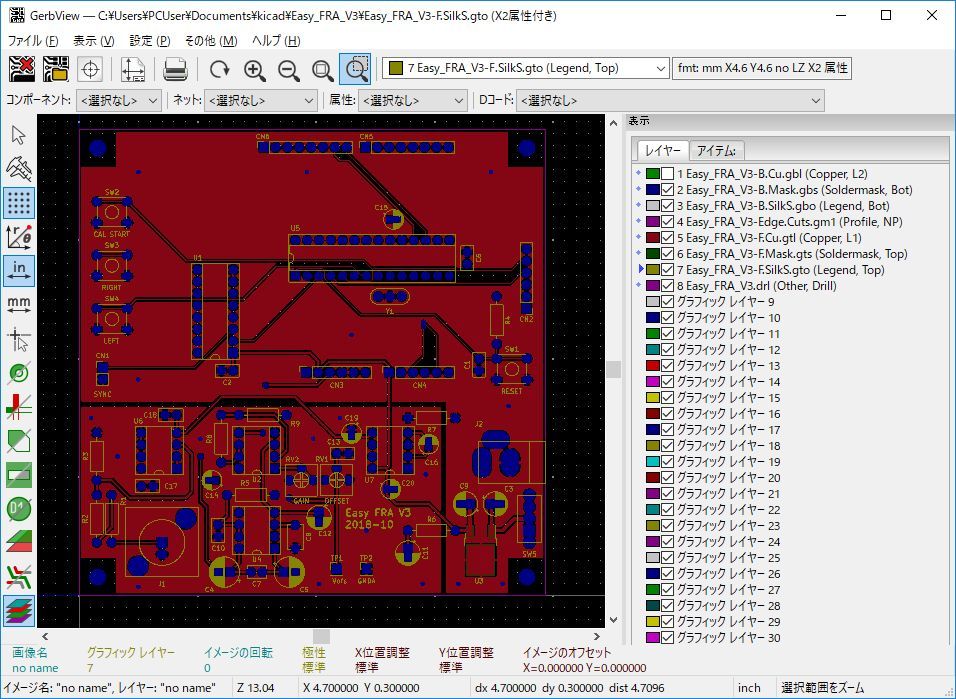

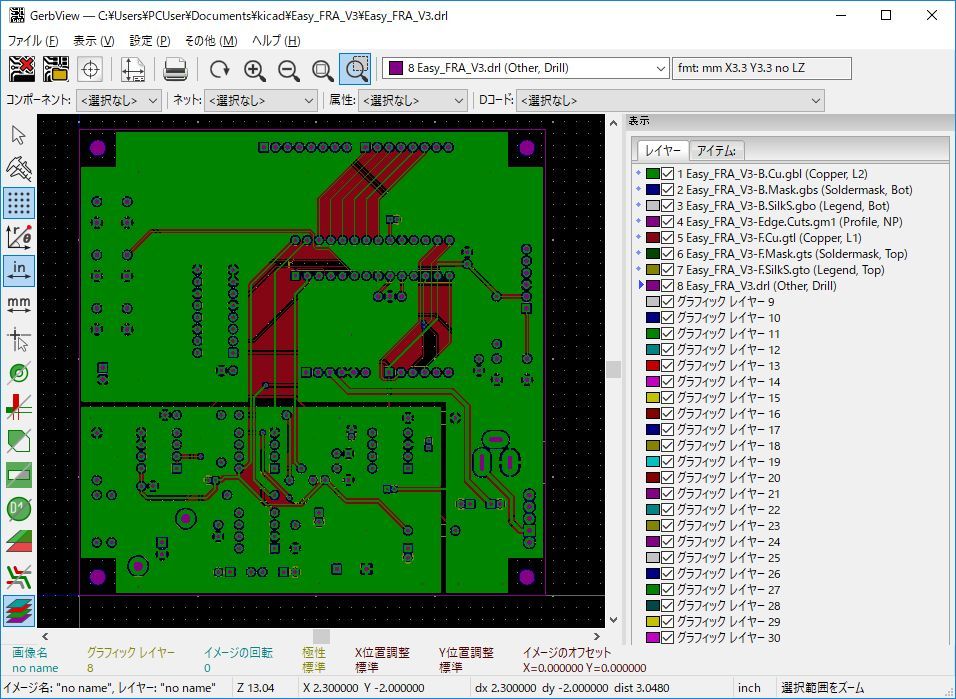

※7 ガーバービューワでの確認

KiCad標準のビューワだと、バカ穴・スルーホールの表示は、パッドにD番号が表示されるだけで

スルーホールの形は確認出来ないようだ? ただ、バカ穴は確認出来た。

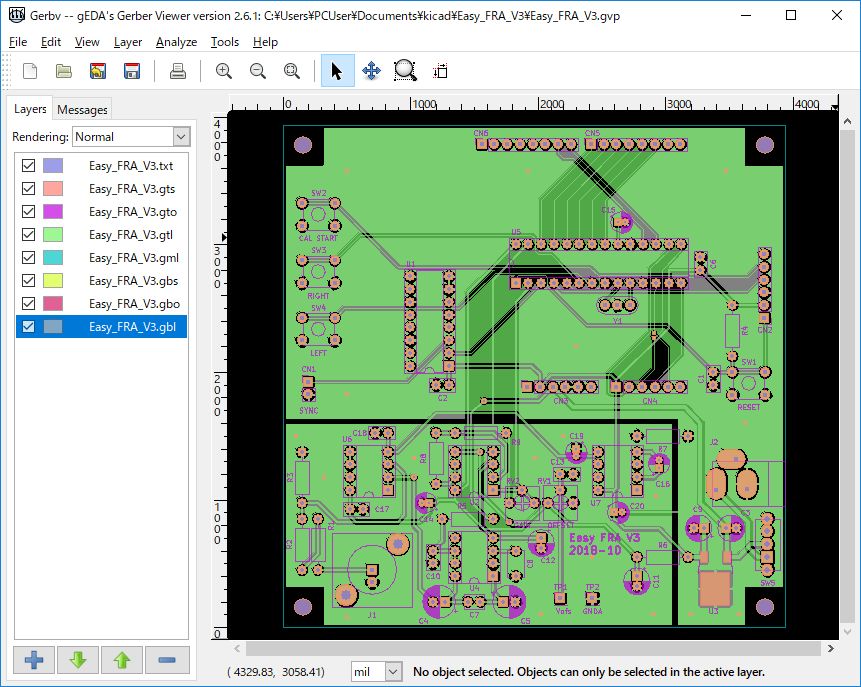

なので、ガーバービューワは今迄通リ、Gerbvを使った方が良さそう。

→ いや違った。

drlレイヤを選択し拡大して行くと見れた。

KiCad標準のビューワ:GerbViewでは、長丸スルーホールが確認出来た。

※8 ファイル名と拡張子の変更

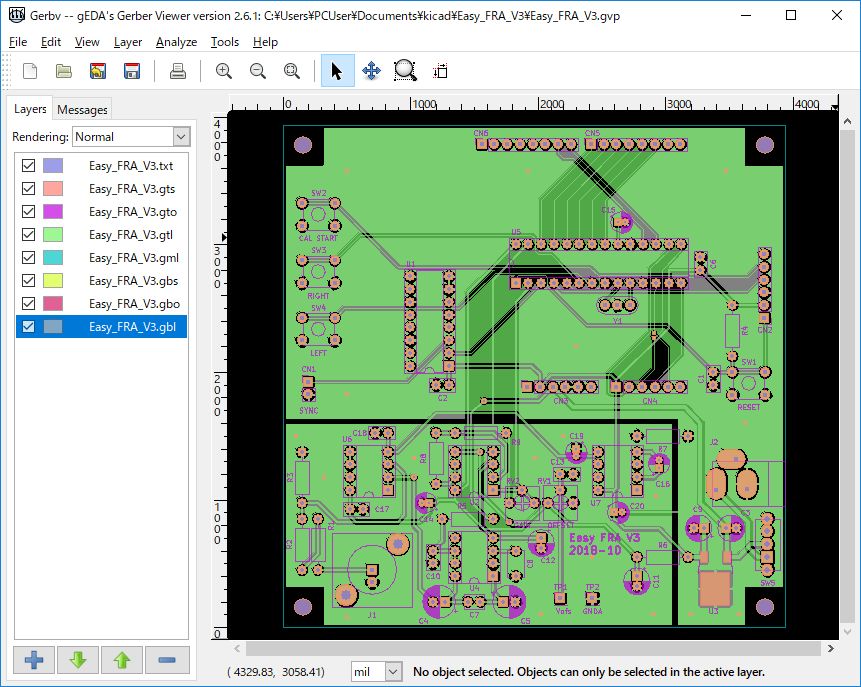

FusionPCBの発注時仕様に合わせファイル名と拡張子の変更を行った。

※9 標準でなく何時も使っている、Gerbvにて確認

何故か、長丸スルーホールが正しく表示されない。端に1個しか丸ホールが表示されない。

→ WEB検索すると、同じ経験をされている方がいた。

一つは、Gerbvではないが、

スイッチサイエンスさんのガーバービューワで見た例だが、そうなっていた。

しかし、上がってきた基板は正常だったらしい。

このサイトの記事です→ 「iw回路設計」さん

<このようなサイト記事もありました>

[so-netプログ:電子工作]

タイトル:KiCadで設計した長穴のフットプリントをFusion PCB (Seeed studio)に注文してみる

GerbvやFusion PCBのGerber確認画面では正しく表示されません…

が、ドリルファイルを見ると以下のように正しく?指定されているようでは有ります。

G05

X122.609Y-138.173G85X121.609Y-138.173

G05

X126.865Y-149.43G85X125.865Y-149.43

G05

X129.242Y-142.13G85X129.242Y-143.13

G05

X131.72Y-140.297G85X131.72Y-141.297

G05

X138.271Y-145.373G85X138.271Y-146.373

G05

X139.119Y-138.173G85X138.119Y-138.173

G05

X143.375Y-149.43G85X142.375Y-149.43

G05

X145.752Y-142.13G85X145.752Y-143.13

G05

X148.23Y-140.297G85X148.23Y-141.297

G05

待つこと二週間ちょい。けっこう速く届きました。

きちんと長穴で仕上がっていました。

→ 自分が生成した今回のドリルファイルの同じような部分を以下に示す。G5で検索

G05が、3回出てくる。長穴は3個なので合ってそう。上の例は10個

G05 // Select Dril Mode Gコードは準備機能を表す。

X90310Y33475G85X88310Y33475

G05

X92360Y27575G85X92360Y29575

G05

T0

M30

※ またfusionpcbのQ&Aページには、こんな記載も・・・だいじょうぶそう。

Q:注文ページのガーバービューアで基板が正しく表示されない場合、製造できますか?← よくある質問(Fusion向け)

A:基板外形やガーバーファイル書き出し時の設定によっては、基板が正しく表示されない事があります。

ガーバービューアは簡易的に基板の内容の確認していただくためのものです。

ガーバービューアの表示と製造の可否は関係ありませんので、安心してご注文ください。

■ 2018.10.5

※1 KiCad標準のビューワ:GerbViewでは、長丸スルーホールが確認出来た。

なのでドリルデータ・外形線データに反映されていると考える。

※2 FusionPCB向けファイル名に変更する時、一つ勘違いをしていた。

小坂氏pdfの、ガーバ生成法の説明は、単体基板のものではなく、面付基板のものであった。(単体基板のものの説明は無し)

基板外形以外はokだが、単体基板外形の拡張子は、KiCadの場合:.gm1→ FusionPCBの場合:GML(面付基板では、GKO)

が正解と思われる。 (xxxEdge.Cuts.gm1)

※3 上記未だ修正してないGKO状態で、Gerbvにて、GBO:裏面シルクを読込んだ時、何故か読込エラーが出たが

裏面シルクは無いはずなので問題ない??

|→Most likely found a RS-274D file...trying to open anyways

↑

274X:拡張フォーマットに対して、274Dは初期の標準フォーマット

だが、KiCadデフォルトでは274Xなはずだが?

■ 2018.10.6

※1 ガーバー作成段階で幾つかの疑問点を抱えている中

昨晩、WEBを検索していたところ、単体基板の場合のガーバー生成手順について記載しているページを見つけた。

「iw回路設計」さんの、「基板作製プログ」-「[KiCad5.0対応版]DCジャック変換基板の作成」がそれ。

これが参考になりそうなので読んでみる。

→ <参考になった事>

・オプションの「原点に補助座標を使用」を選択すると、『ガーバーデータ出力前に座標原点の設定』で設定した座標原点が適用されます。

これを選択しない場合は、基板エディタ上の左上が原点とした絶対座標で出力されます。

・FusionPCBのファイル名に変更は以下

トップレイヤの名前 : pcb_name.GTL

ボトムレイヤの名前 : pcb_name.GBL

表面のソルダレジスト : pcb_name.GTS

裏面のソルダレジスト : pcb_name.GBS

表面のシルク : pcb_name.GTO

裏面のシルク : pcb_name.GBO

ドリルデータ : pcb_name.TXT

基板外形 : pcb_name.GKOまたは.GML→ ※ 説明によると、.GKOでも.GMLでもよさそうである。でもGMLにしておく。

※2 基板外形データの拡張子を、GKOからGMLに変更して、再度Gerbvにて確認してみたが、変更前と同じく、長穴は

正しく表示されなかった。どうも、Gerbvでは駄目なようだ。

FusionPCBのガーバビューワで見てOKだったら発注作業を進めようと思う。

■ 2018.10.8

※1 FusionPCBのガーバビューワにて確認してみた。長穴が心配だったが、それは正しく表示されていた。

しかし、何故か、他のホールがパット上に表示されず、左下角の取り付け穴上に重なって、長穴以外のホールが

まとまって、重なって表示されている。

あとシルク文字の太さが若干細く見える。→ Eagle時と同じく、7mil(0.1778mm)にするか?今は、0.15mmだが・・殆ど変わらないはずなのに?

まあこれは置いといて、ホール問題をなんとかしないと。

何故、KiCad標準ビューワと、Gerbvでは正常に見えるのに、FusionPCBのガーバビューワだと駄目なのか?

たぶんドリルデータ出力時の設定の問題と思われる・・・

現在のプロジェクトのバックアップを取っといて先に進めようと思う。

<試行>

① ドリルデータ出力時の設定の問題と思われる・・・

設定はFusionPCBサイト通りであったので問題ないと思う。

② FusionPCBサイトの説明では、拡張子であるが、

ドリルデータは、.drl

外形データは、.gm1

となっていた。

今は、.txt, .gml

修正しても同じだった。

③ 結局、「iw回路設計」さんのドリルファイル生成設定の通りにしたら、FusionPCBのガーバビューワにて正しく表示した。

どうも、FusionPCBサイトのビューワは、リーディングゼロサプレスに対応してないようだ。

ゼロの扱い:小数点フォーマット→

先頭ゼロ省略(リーディングゼロサプレス)からの修正

ドリルマップファイルフォーマット:ガーバー→ これはPostScriptでもよいのかもしれないが試してない。

※2 シルク文字の太さが若干細く見える件だが、今回はこのまま行って出来栄えを確認し次回考えることにした。

→ 上がってきた基板を見たが特に問題はなかった。

※3 FusionPCBへ発注済→ 2131円

・100X100 3枚(1$キャンペン中)なのでデフォルトのままでよい。

・今回は、FidExの方が、DHLより運送料安くなっていた。香港から4~8日

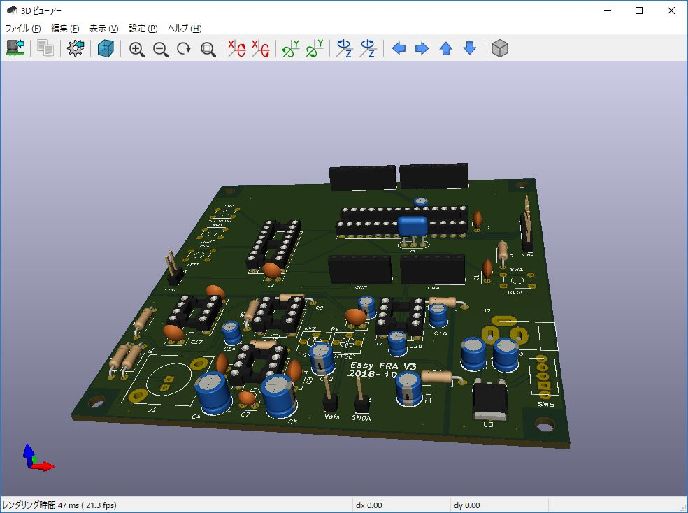

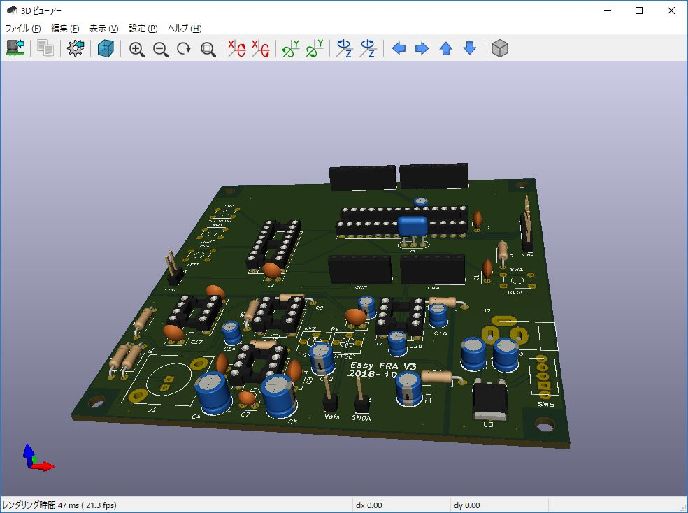

※4 3Dビューワでも確認してみた。当然標準で用意されていないパーツは表示されないが、それでも

このビューワは興味をそそる。自分でモデルを作るソフトもあるらしいし・・・

■ 2018.10.9

※1 ドキュメントを整理している途中で、BNCコネクタの、B-056のフットプリントが間違っていることに気付く。

位置決め用のピン位置が180°反転していた。

メーカーの寸法図が、BOTTOM、TOP VIEWを、ごりゃまぜにして書かれている為、信号ピンと、GNDピンの位置

は問題無かったが、位置決め用のピン位置が反転してしまった。現物合わせがやはり必要だった。

あとボードに置く位置もちょっと問題だった。

全体を180°回転して置いてしまった為、結果的に位置決め用のピン位置は辻褄があって問題なくなったが

GNDピンの位置が、信号ピンに対しY方向下になってしまった。これだと、正規な実装位置にならず実装出来ない。

GNDピンの位置を信号ピンに対しX方向右に修正が必要になった。

※ 1箇所のみ、1φの穴加工をし、そことGNDピンのランドをストラップする修正が必要になる。

今回は試作で1枚のみ実装する予定なので、この修正で逃げることにした。

P板のバージョンアップはこのプロジェクトではやらないことにした。

この次に、Easy_FRA_V4として、DDS部を一体化したハードを作る予定なので、その時に、

フットプリント名:BNC_Vertical_COSMTEC_B-056_REV1として作り直つもり。

明日、部品を先行手配しておく。

秋月で集める。ただし抵抗は標準だがマルツにした方が送料+手数料がかかっても割安。

但し、IC類はUNVから抜いて使う。

■ 2018.10.10

※1 部品手配済→ P板:2131円(1$ 3枚キャンペーン)+部品代:756+1610= 4497円

■ 2018.10.22

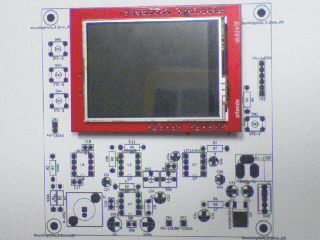

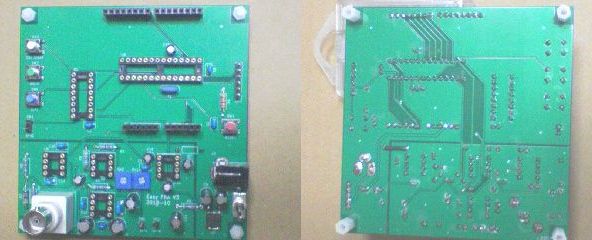

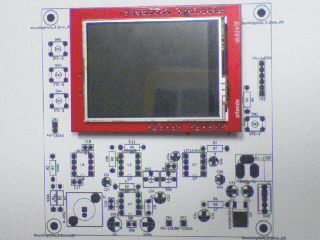

・FUSION PCBから、P板届く。

FedEXにより、午前中に着いた。(発注から約2Wで到着)

■ 2018.10.24

・BNCフットプリント・ミス修正作業

① 90°回転させた、X方向に信号ピンの穴:0.9φをピンバイスで開ける。

② BNC実装後、信号ピンと、元のGNDAビアをメッキ線にて接続。

・実装終了

・V3デバッグ開始

(1) ショートチェック→ OK

+5V-GND

+3.3V-GND

+3.3VA-GND

-3V3-GND

(2) ICはLTC1144のみ実装 QVGA未実装にて電源確認

+5V:5.22V

+3.3V:3.29V

+3.3VA:3.29V

-3V3:-3.29V

(3) MPU実装し、HEX書込み(尚、ソフトは、ユニバーサル版:easy_fra_v3.c

で動きます。)→ OK

(4) IC全て実装 QVGA未実装にて電源確認

+5V:5.21V

+3.3V:3.28V

+3.3VA:2.96V(= Vref)

-3V3:-3.18V

(5) IC全て実装 QVGA実装(稼働状態)にて電源確認

+5V:5.21V

+3.3V:3.28V

+3.3VA:2.95V(= Vref)

-3V3:-3.18V

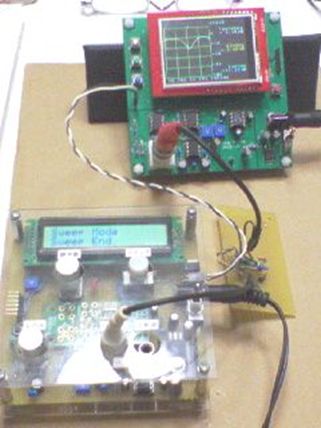

(6) 動作確認

① DDS繋げないで単体で、P_ONした時、スタート・メッセージが出る。→ OK

② DDS繋げないで単体で、P_ONし、CAL SWを押すと、スケール画面になり、ドット描画開始する。→ OK

③ LOG AMP部の調整:F=1kHz DDS:フリーラン

・とりあえず、Vofs(オフセット)を、1.87Vに合わせ、GAINトリマは中央付近の位置にしておく。

-40dB(0.010Vrms)入力し、CAL SW ON

・-40dBラインに、ライン描画が一致するように、GAINトリマを調整

・入力を-30dB(0.0316Vrms),-20dB(0.100Vrms, -10dB(0.316Vrms),0dB(1Vrms)と可変していた時

各描画dB軸に、一致しているか確認する。偏差は±1dBまでは、OKとする。

→ 大方、OKのよう。

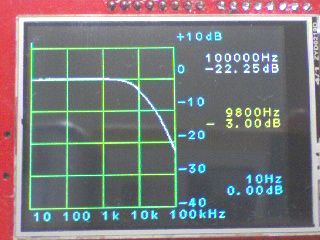

④ DDSを、スイープモードにし、F特描画を確認

被測定フィルタには、パッシブCR=1000p x 10k/ Fc=159/CR= 15.9kHz を使用。

F特描画は正常だが、-3dB表示が、9800になっている。

_V2の時のデータでは、12000になっている。

まあ、パッシブCRの場合、理論値と実測値にかなりの違いがあることを体験しているが、ちょっと気になる。

_V2の、LOG AMP部の調整時の資料は以下

● コンディションを実測してみた。(Vofs=オフセット電圧/以下測定には自作AC電圧計を使用)

① Vref(AVCC)= 2.94V

② Vofs= 1.86V ADC入力

③ 0dB(1Vrms)入力時の、ログアンプ出力(4pin)= 2.03V : 後段アンプ出力(IC2A-1pin)= 2.24V

-10dB(0.316Vrms)入力時の、ログアンプ出力(4pin)= 1.79V : 後段アンプ出力(IC2A-1pin)= 1.73V

-20dB(0.100Vrms)入力時の、ログアンプ出力(4pin)= 1.55V : 後段アンプ出力(IC2A-1pin)= 1.21V

-30dB(0.0316Vrms)入力時の、ログアンプ出力(4pin)=1.31V : 後段アンプ出力(IC2A-1pin)= 0.71V

-40dB(0.010Vrms)入力時の、ログアンプ出力(4pin)= 1.08V : 後段アンプ出力(IC2A-1pin)= 0.22V

今回との違いは、ADCのVref(AVCC)= 2.94V→ 2.95V/ Vofs= 1.86V→ 1.87V で殆ど変わらないはず。

回路も、使っている素子も_V2から外したものをそのまま使っているので同じはず。

回路の転記ミスはないようなので、抵抗の実装ミスか、CAL調整の微妙な違い??

スイープモードのステップは、9800→ 10000→ 12000となっているので、GAINが低め設定かもしれない。

■ 2018.10.25

・LOG AMP部の調整を、やり直してみる。

今度は前回資料の、ADC入力電圧に合われば、ソフトは同じなので、描画も3dB点も同じになると思う。

ADCのVref(AVCC)= 2.94V→ 2.95Vで殆ど同じなので。

→ 被測定フィルタが、パッシブCR=1000p x 10k/ 理論値:Fc=159/CR= 15.9kHz 但し、C[uF],

R[kΩ]

では、結果は変わらず、実測Fc=9.8kHz@-3dBであった。

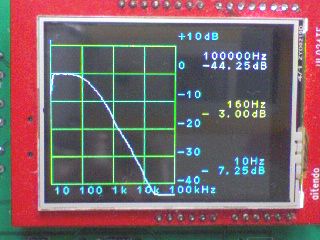

ただ、パッシブCR=0.1u x 10k/ 理論値:Fc=159/CR= 159Hz

では、実測Fc=160Hz@-3dBとほぼ合っていた。

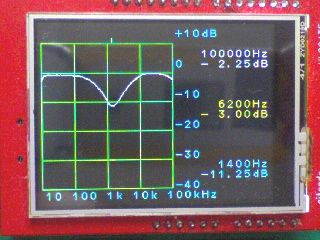

また、パッシブノッチの C=1000p R=100k/ 理論値:Fo= 1.5k@-12dBも、実測Fo=1.4kHz@-11.25dBとほぼ合っていた。

→ パッシブCR=1000p x 10k/ 理論値:Fc=159/CR= 15.9kHzが合わない原因だがよくは判らない。

定数の温度変化位しか考えられない。

試しに、手取りで、DDSと、AC電圧計だけ使って、F特を確認してみたところ

Fc付近の周波数では以下のようになった。→ この付近の落ち方は緩慢。

8k 0.8V

9k 0.76V

9.8k 0.76V

10.7k 0.70V→ これが-3dB周波数なので、FRAもどきの結果と極く近いので良しとした。

11k 0.69V

12K 0.66V

・各SW機能チェックも、OKなので、これでまとめに入ることにした。

<回路図>

・こちらから、どうぞ→ 「Easy_FRA_V3」

← 実験テーマ1に戻る TOP

PAGEに戻る 実験テーマ110へ →