◆PSM3DのドキュメントINDEX

とりあえず、てっとり早く動かしてみたい方は、こちら

◇はじめに

本ドキュメントの本文や図や表は、RTLやCソースを読む時の参考とお考えください。

ソースの内容と、ドキュメントの内容は、なるべく一致させるよう努力するつもりですが、もし一致しない部分がありましたら、ソースの方が正しいです。

◇PSM3Dのプログラミングモデル

こちら

◇命令セット

32bit固定長です。

筆者にとっての作りやすさを重視してます。 たとえば、レジスタ指定のフィールドは4ビット境界をまたがないとか・・・

こちら

◇プロセッサコアの構成

こんな感じです。

◇プロセッサコアのブロック図

こんな感じです。(でかい図ですみません)

◇FPGAの全体

こんな感じです。

◇周辺も含めたメモリマップ

こちら

◇周辺回路のレジスタ表

こちら

◇VGA-IFに関して補足

2面を合成しながらVGA(640×480)出力します。

◇内部バスのプロトコル

シングル転送しかできないSBUS1と、これをバースト転送できるように拡張したSBUS2があります。

SBUS1

SBUS2(1/2)

SBUS2(2/2)

◇デバッグ機能について

UARTを使って、PCからFPGA内部へアクセスできるようにしてます。

こんな感じです。

dbgUart部の詳細

通信コマンド表

この部分に関しては、汎用性が高いので、いろんな部分に応用できると思います。

このdbgUartを使って、オンチップデバッグ機能(FPGA全体ブロック図中のP3dDbg)をアクセスして、デバッグ機能を実現しています。

P3dDbgのレジスタ表はこれです。

◇DDR-IFについて

6マスタのDDRメモリインターフェースです。

各マスタの優先順位は固定です。

CPU側のクロックと、DDRのクロックが非同期の為、アービタとDDR-IF部の間にFIFOを挟んでます。

このFIFOはライトバッファとしても機能するので、ライト側の性能はそこそこですが、

READ側は、コマンドの行きと、READデータの戻りで非同期FIFOを2回通過するので、レイテンシが大きいです。

このため、キャッシュOFFだとCPUの性能が悲しいほど低下します。

また、VGA-IFでは、この問題を回避する為、READデータの到着を待たずに、連続してREADコマンドを発行することで帯域を確保しています。

DDR-IF部のブロック図はこちら

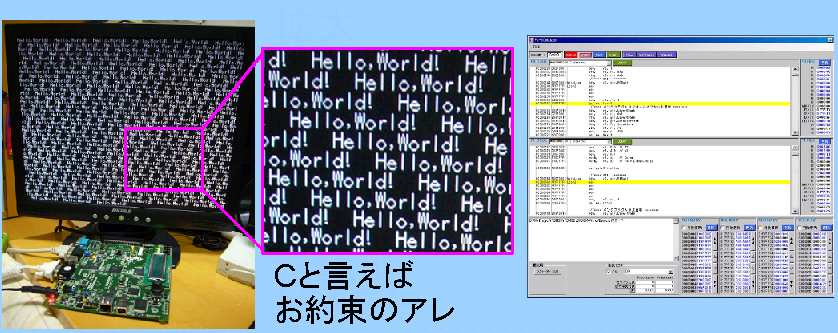

◇デモプログラム

Cコンパイラが使えるようになってきたので、Cコンパイラで開発しています。

プロセッサ0で、タイマ割込みを使い定周期に”Hello,World!”の文字列を表示用テキストデータバッファへ書き込み、

プロセッサ1で、上記のテキストデータバッファの内容をビットマップフォントに展開してフレームメモリへ書き込んでます。

◇デバッガ(ICE)

初めてC#を使って書きました。

#defineで定数を定義しようとして、いきなりコケる所からスタートしました。

これが無いとデモソフトが動かせないので公開していますが、はずかしいのでソースはあまりジロジロ見ないでください(汗)

使い方はこちらを参照してください。

◇FPGAのコンパイルの仕方

こちらを参照してください。