● 実験テーマ94

「dsPIC33F_QVGA心電計の、P板化」

(PIC16F1983(8bit/16MHz)でQVGAを扱うには、多少無理があったので、16bit/40MHzのPICで、P板化し実験してみました。)

以下、この実験の顛末記です。

■ 2017.7.4

・メモリに余裕のある、dsPIC33FJ64GP802(FLASH:64kB/SRAM:16kB)を使用して

QVGA表示心電計の実験をしてみることにした。

今回は、P板設計→ FUSION PCBへ発注手配から先に行うことにした。

(実験に使い易い適当な、ユニバーサル実験基板が無い。最初に、ユニバーサル作る位なら

最初から、試作ということで、P板にした方が良い。とにかく格安の、FUSION

PCBなので、

気楽にオーダー出来る。)

■ 2017.7.5~ 2017.7.7

・今回のCAD作業の方針

→ アナログ部のパターンは、そのまま動かさないで前回(PIC16F_ECG_BOARD)のを流用できそう

なので、回路図を最初から作成するようなことはしない。

・この今迄の回路パターンを流用して作業を進める方法は、Eagleでは初めて。

自分なりに試行してみることにした。

① プロジェクト名:ECG_BOARD_V4にして、ワークフォルダを作成

② PIC16F_ECG_BOARD.sch→ ECG_BOARD_V4.sch

PIC16F_ECG_BOARD.brd→ ECG_BOARD_V4.brd

にリネームして、①のフォルダ下に保存

③ 回路図を立上げる。(自動的にボードも立上る。)

④ 回路図から、PICを削除。

その他、変更になる液晶コネクタも削除。

使うパーツのみ残し、ネットを極力カット。

→<ここまでの結果>

・カットしながらボードを見ると、連動して消えてゆく。

・この時点で回路図をセーブ→ 何もエラーは出なかった。

・そしてボードを閉じる。ここでもエラー無し。

・一回、Eagleを立下げる。

・再び、Eagleを立上げる。ここでもエラー無し。

⑤ デジタル部は、パーツを残してネットも削除。変更するJ1も削除。

デジタル部のビア打ちも削除。

IC4の電源を、3.3Vに変更するので、8pinの+5Vネットも削除。

⑤ ここで、回路図に追加部入力。

全て追加したら、ERCを掛ける。

エラー:14個(Supply pin overwritten with more than one

signalと、Unconnect INPUTエラー)

ワーニング:38個(overlaps pin等)

が出たが、全て承認できる内容なので、OKとした。

この後の、ネットリスト目視チェックで問題無し。

⑥ 3.3Vレギュレータ追加と、J1の変更、QVGA化により以下のパーツの移動が必要になった。

これらの位置決めを行い、予めX-Y座標を計算しておく。

QVGAコネクタ・READY SW・AUTO/SING.SW・SEC/D SW・READY

LED

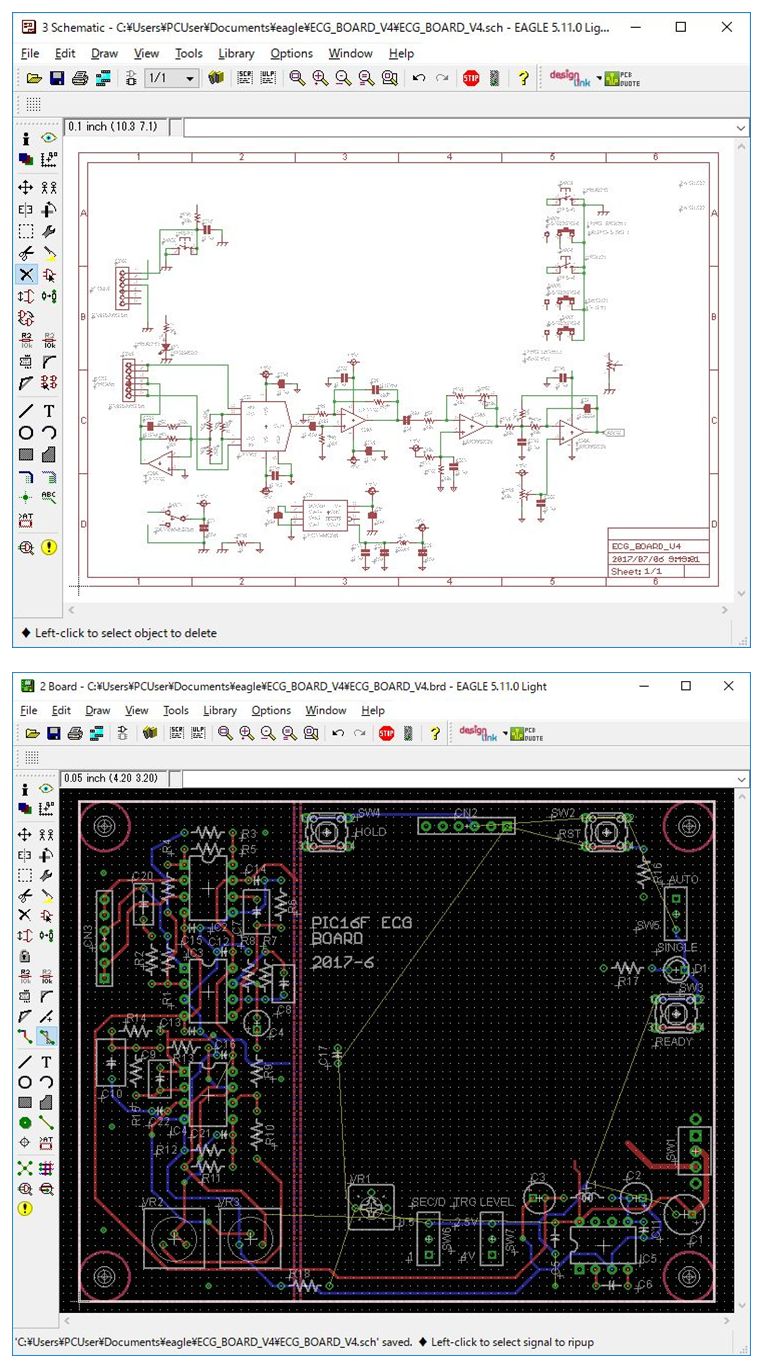

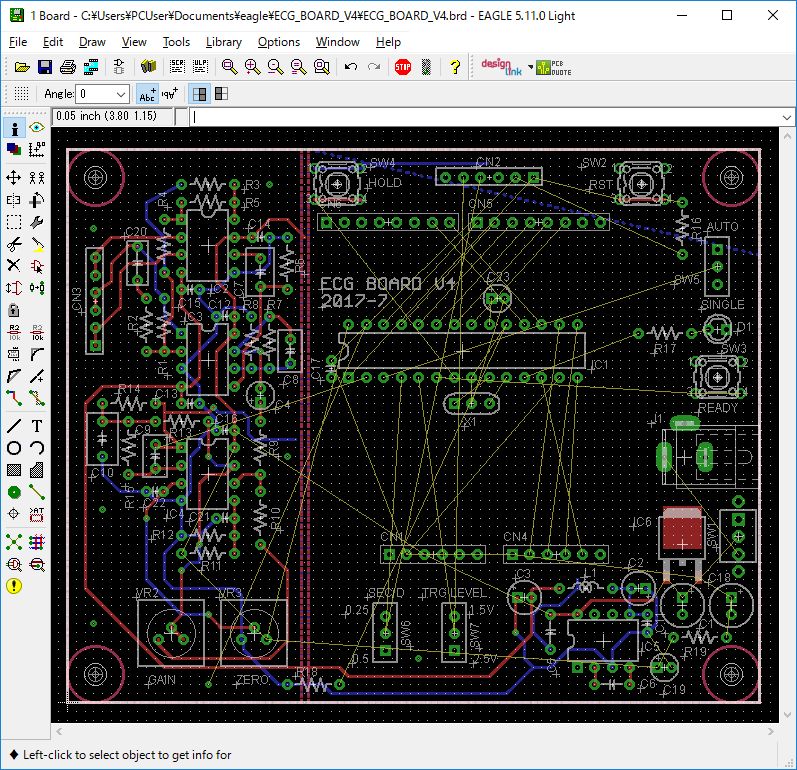

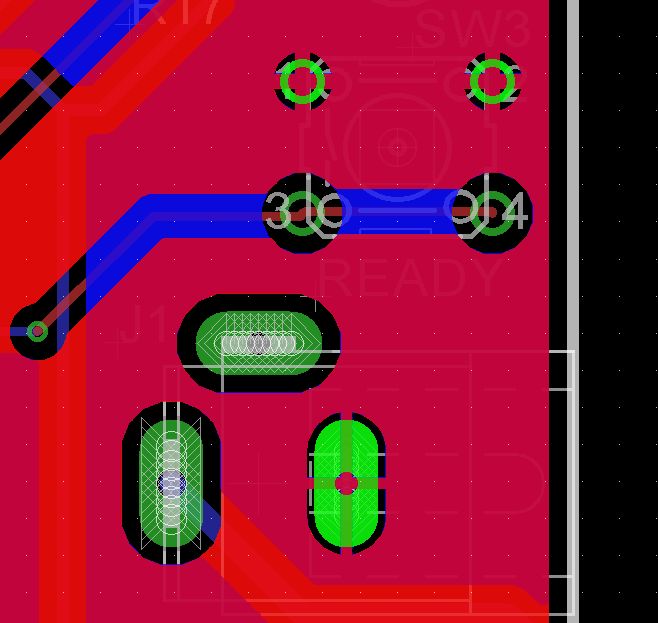

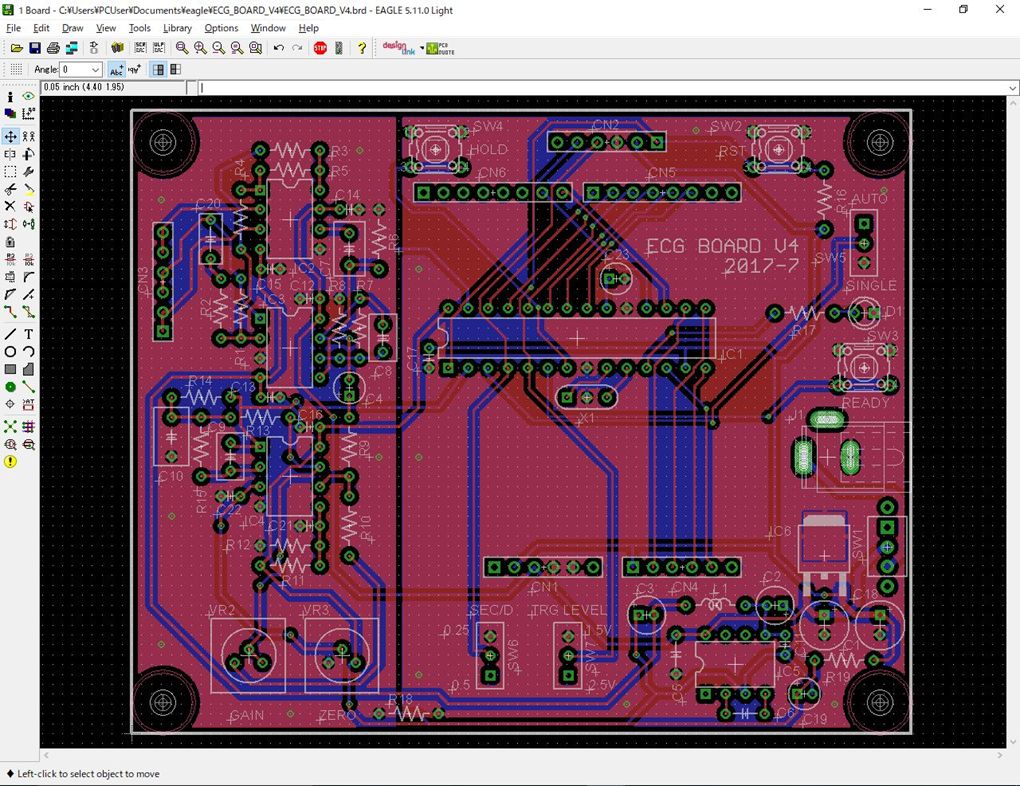

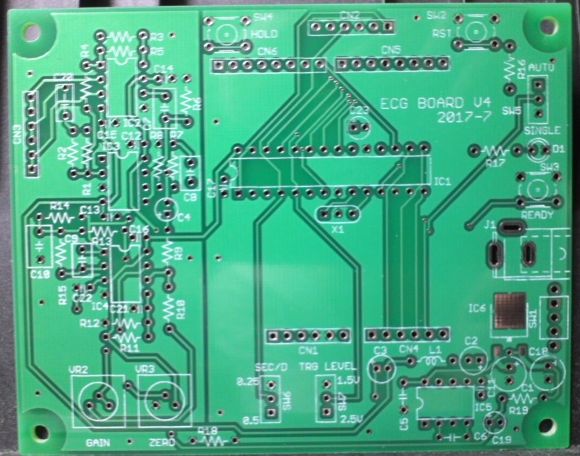

以下にここまでの、ボード状態を示す。

■ 2017.7.8

・変更・追加部品の配置まで終了した。

・QVGA液晶のフット・パターンが合っているか確認。

■ 2017.7.10

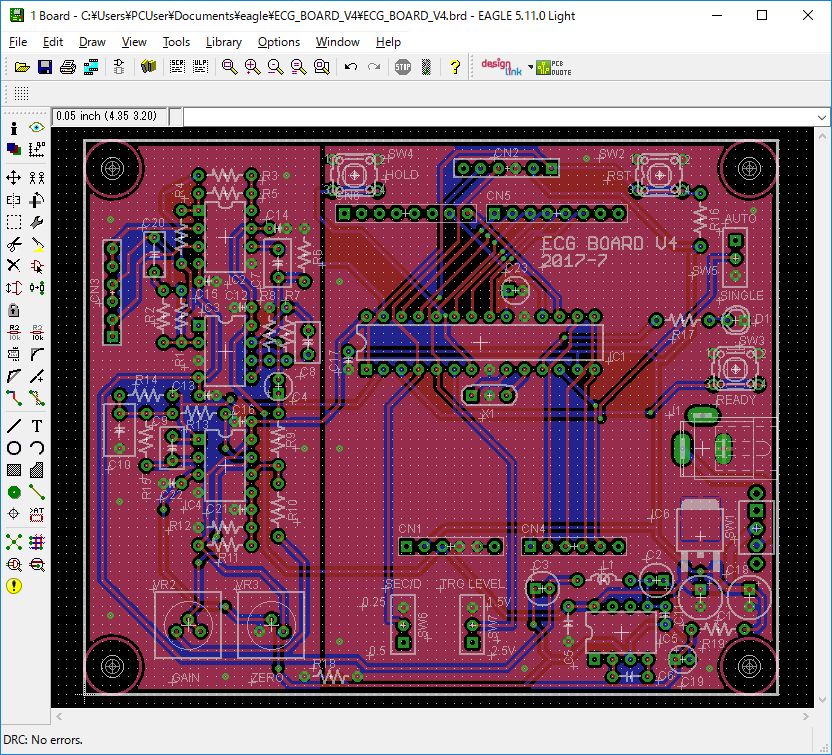

・AUTOルータ+手直し+ビア打ち+ベタ+DRCチェックまでOKになる。

■ 2017.7.11

・今回の一番の懸念は、J1の長穴(メッキ有り)3個が、FUSION

PCBの方で問題無く製造出来るか?である。

今迄、国内の基板屋さんに発注していた時は、Eagleライブラリに付いてくるパッケージをそのまま使うと

ボード及びガーバービューア上では、長丸Padの中心に、1個のスルーホールが表示されるだけあるので、

別途、長穴スルーホールである旨、その寸法を指示した図を添付して製造して頂いてた。

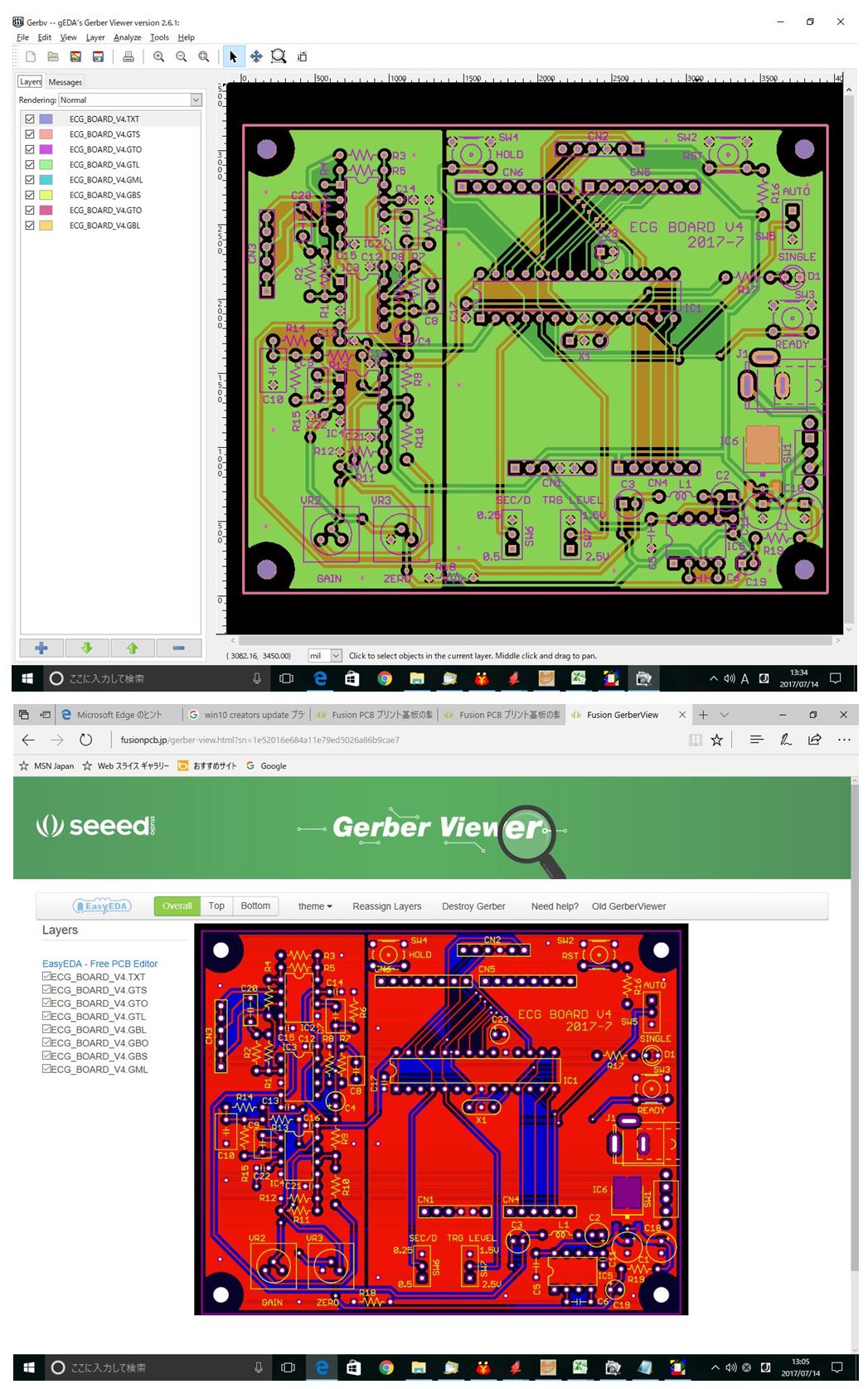

しかし、FUSION PCB提供の、CAMプロセッサを使うと、GMLファイルに外形データと共に、長穴(ミーリングレイヤ)

データも生成されるようなので(自分で確認した。)このまま、ガーバーデータを生成して、一度、gerbvと、

FUSION PCBサイトのビューアで、長穴表示されるか確認してみようと思った。

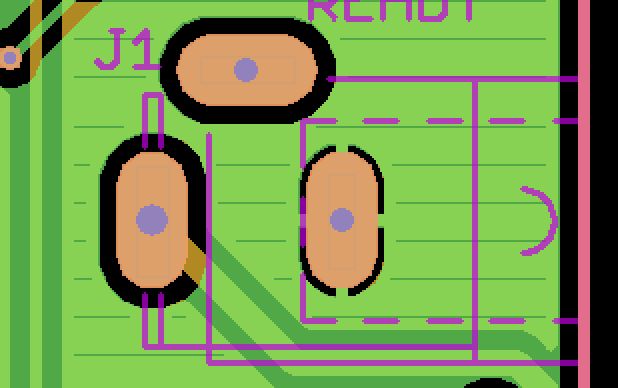

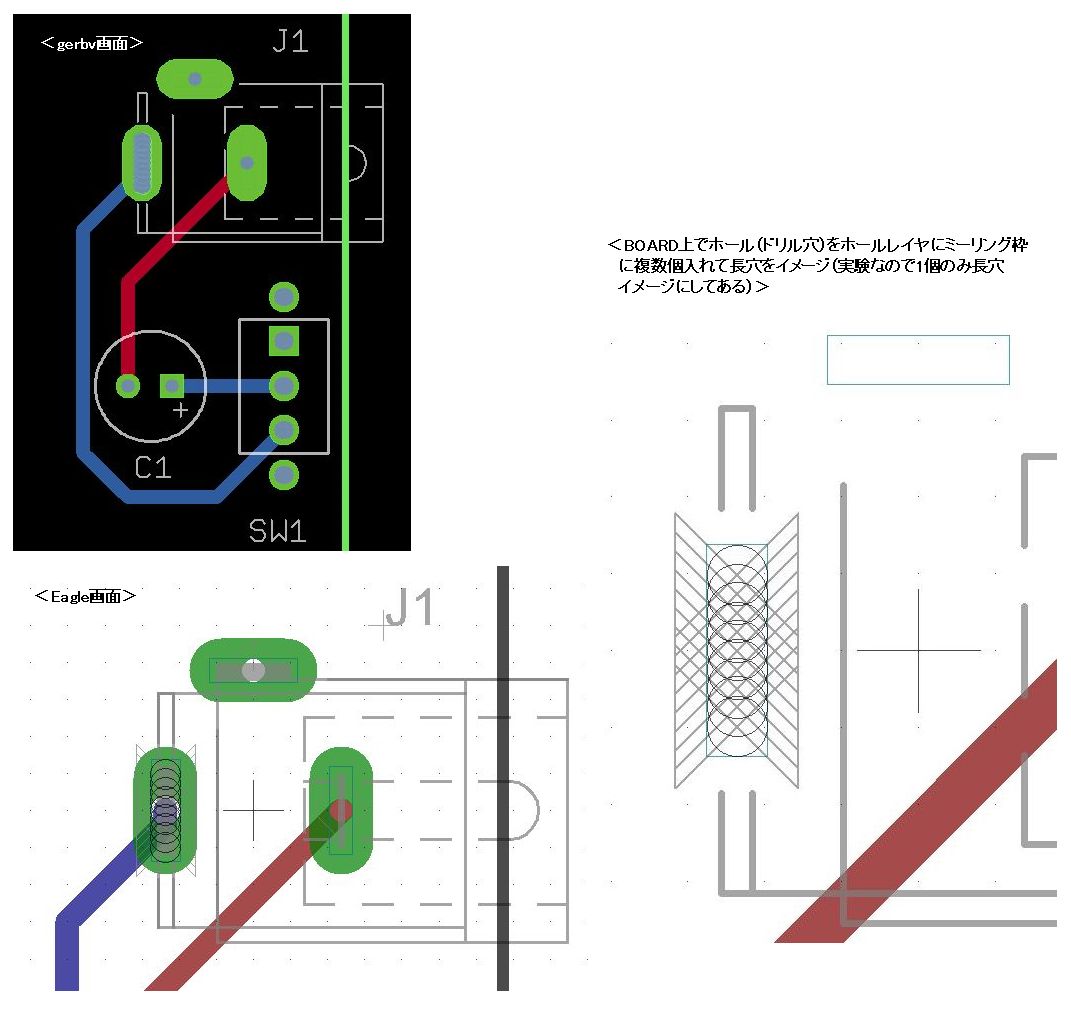

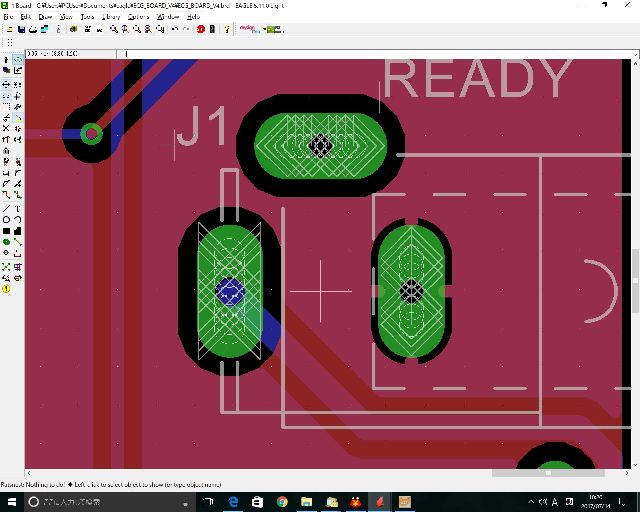

gerbvでの、J1部の拡大図を以下に示した。

御覧の通リ、長穴にはなってない。

しかし、見ずらいが、薄い紫で、ミーリングレイヤの、四角い枠が表示されている。(このままで製造してくれるだろうか?)

FUSION PCBサイトのビューワでも確認してみたが同じだった。

・不安だったので、FUSION PCBに、このガーバーデータ一式を添付して、問合せのメールを出してみた。

夜回答のメールが届いた。

「長穴スルーホールには1個だけの円穴があるので、できるだけドリルレイヤでもっと多くの円穴をあけ、

長穴スルーホールのイメージを表すのをお勧めします。ファイルを直してください。」

とのこと。

■ 2017.7.12

・ただこの方法は手探りでやるしかない。

WEB上では、スイッチサイエンスさんのサイトとか、ここのサイトに、長穴作成についての説明書きが

あったが、長穴パッドを一つのデバイスとして作成するので、回路図シンボルが、J1とイメージしずらいし、

もう一方のサイトの例は、たぶんKiCADの例で、とても面倒で、やる気にはなれなかった。

回答メールの内容を素直に理解すると、ミーリング加工と同じように、より多くの円丸を置いて、長穴の

イメージを表現すれば良いように思う。

添付されてきた参考イメージを拡大すると、ミーリングレイヤに沿って円丸が多数配置されているだけ

に見える。無限に並べている訳でないので、長穴の周囲はゴツゴツになっている。

あくまでイメージすればよいのかな?

・この長穴イメージは、ボード上でやっても、J1のパッケージ上でやっても、どっちでも良い。

後者の方が、毎回ボード上に置くだけでよいので、後者にするべきだが、最初は、実験的に、

Eagleのボード上で、45-Holesレイヤに、Milling枠に沿って、Hole(ドリル)を複数個配置して、

イメージを作った。

本来は、メッキ有りの長穴なので、44-Drillレイヤを使って、Drill(スルーホール)を複数個並べたい

のだが、Eagleのメニューには、Drillは無く、Pad(これには、Drillマーク?が含まれる)がこれに

相当するが、例えば、長丸パッドを置いて、Drillレイヤを表示すると、Drillマークのようなものが

表示される。

ところが、これをコピーとか、infoしようと思っても出来ない。(尚、Eagle

V5.11.0を使っています。)

そこでしょうがないので、イメージなので、Hole(つまりはバカ穴)を置く方法にして、メッキ有り長穴

ということを別途指示することにしました。

Hole(ドリル)を複数個配置するので、druチェックで、Dimensionエラーと、Drill

Disranceエラーが多数発生

しますが、これは無視してもよいようです。(後でこのデータを送って、FUSION

PCBに問合わせました。)

以下に、別プロジェクトでこの実験をした時の、パターン図を示しました。

実験なので、JIの長穴3個の内、1個だけイメージしてみました。(ただしベタGND無し)

■ 2017.7.13

・今日は、パッケージ上で長穴イメージを追加する方法(本番はこっち)を試してみた。

現行のJ1(JACK_PLUG:SPC4077.pac)を、FUSION用長穴対応パッケージに修正。

Pac名:「SPC4077_FUSION.pac」として、Pacを作成し、これをテスト・プロジェクトに置いて

上手く行くか試す。(ベタなし)

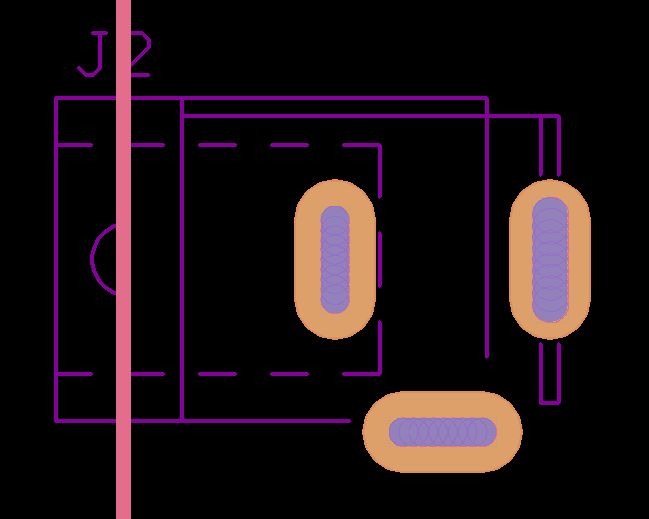

回路図上に、JACK_PLUG:SPC4077.pacの、シンボル:J2を、J1の反対側に置くだけで

何も配線しない。これで試した。

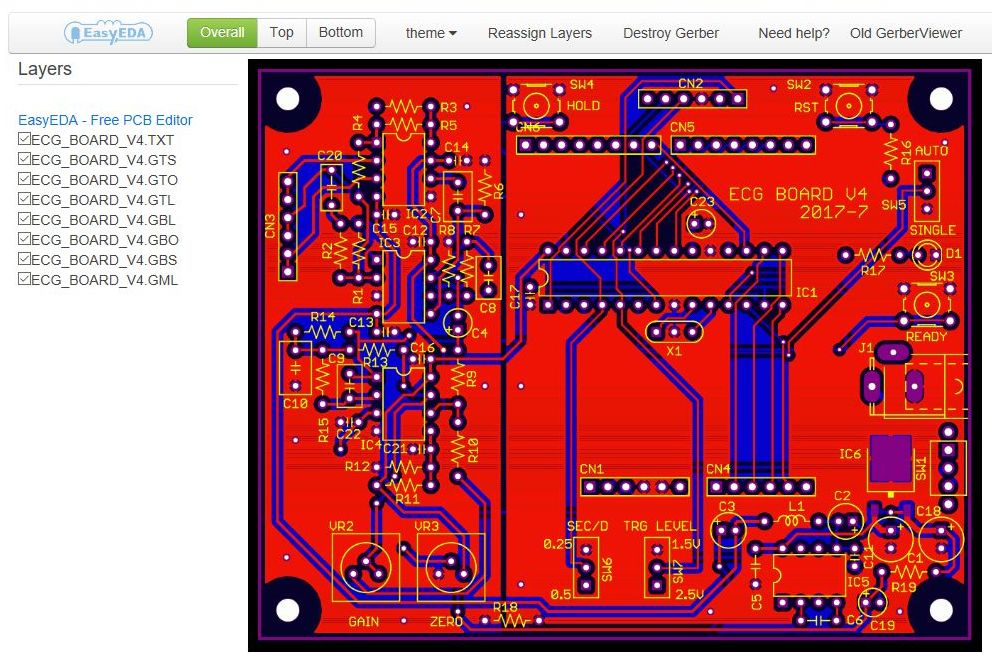

以下のように、綺麗に長穴パッドがイメージされた。

・これを、本番のボード上でやってみる。

回路図上で、旧J1シンボル(SPC4077.pac)を削除すると、ボード上から、J1は消えるが、それに接続

されている+5Vネットが全て、エアーワイヤに戻ってしまう。

これはボード上で、J1を削除しても同じ。

なのでここでは、Replaceコマンドを使う。

ボード上で、J1を右クリック→ Replaceを選び、開いたリストから、JACK_PLUG_FUSIONを選び、

リプレースすればよい。

これで、ネット(パターン)が繋がった状態で置き換わる。

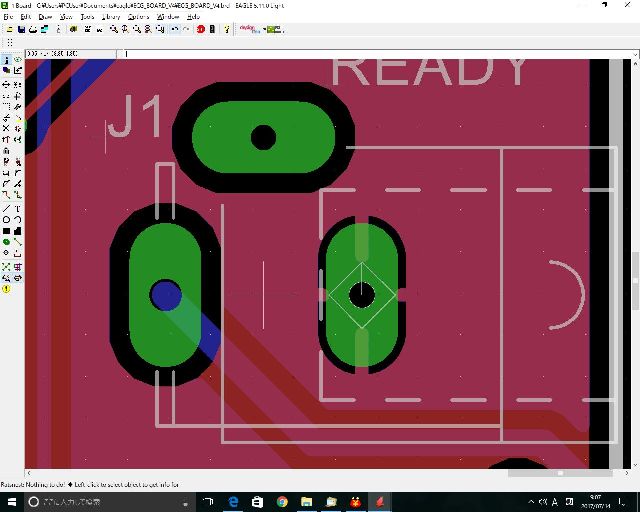

ところが、Ratsnestコマンドで、ベタGND表示させると、ベタGND(DGND)に接続されている、J1のピン

のネットのみエアワイヤに戻ってしまうのです。

ベタ表示させた状態で、Replaceすれば、その時は、上記のようなことは起こりません。

以下のように綺麗に、DGNDベタに接続されています。

しかし、1度、Eagleを立下げ、再度ボードを立上げて(この時点では必ず、ベタ非表示になる)再度、

Ratsnestコマンドで、ベタGND表示させると、ベタGND(DGND)に接続されている、J1のピン

のネットのみエアワイヤに戻ってしまいます。

・ここらでPCを切り、14時頃出かけて、夜帰宅、PCを立上げたら、何やら、Windows10の大幅な更新(Creators

Update)

があるらしく、更新通知のダイアログが表示された。

とりあえず、[再通知]のボタンをクリックして無視した。

ここでEagleを立上げ、J1の修正前デバイスファイルと、長穴イメージ追加修正後のデバイスファイルに何か差異

が無いか比較しようと思って、Eagleのメイン画面で、My_Libを立上ると、そのディレクトリ下にあるライブラリファイルが

見えないのである。

入力が済んでいる回路図・ボードは正常に開け表示も異常ない。

また、Eagleの標準ライブラリは一覧が見られる。肝心の自作ライブラリが何故かこのタイミングで見れなくなった・・・

しょうがないので、PCを再起動してみることに。

そしたら更新があるようなので、更新して再起動を選んで、再起動。

この後も、直ぐ新しい更新があり、再び再起動。

この時、再通知にしたはずなのに、勝手に、Creators

Updateのインストーラがダウンロードされ、インストール

されてしまった。(クリエータ向けアップデート。Edge機能追加・セキュリティ強化らしい)

■ 2017.7.14

・勝手に、Creators

Updateが実行されてしまった。(後にしようと思ったのに・・・)

以前に比べると違和感が数点ある。webにも紹介されている。

ブラウザ:Edgeの字体が変わってしまった。太目で、行間隔が広めのフォームに。

まあ見易くなったと言えばそうは言えなくもないが・・・(慣れの問題か?)

・ところで、My_Libが見えなくなった問題だが、アップデート後は、正常に見えるし開けている。

ほっと一安心。

たぶん、開けなくなったのは、その作業中に、このアップデートの為の、事前ダウンロードが複数回

重なっていた為と想像する。

・J1のベタGNDがエアーワイヤになる問題に戻る。

いろいろ調べてみることに。

① J1ライブラリを修正して、新たに長穴イメージ追加のライブラリを作ったので、そこに差異は無いか?

→ Pin名も、Pad番号も、ネットリストも問題なし。差異は無い。

② J1を元のJACK_PLUGに戻しボード上でGNDピンの中心のみにHOLEを重ねてRatsnestコマンドで、ベタGND表示

→ Padの一部とベタの十字部の一部は重なるが、丸穴とは切れる。再度Ratsnestしても、DGNDネットから

切り離される。エアーワイヤが残る。

しかし、他のベタGNDに繋がらないPadのネットは正常である。

③ JACK_PLUG_FUSIONの長穴イメージを作り直す。

3個のPadともに、中心には、Holeを置かない。(ドリルのみにする。)

→ これでも同じ。

④ JACK_PLUG_FUSION修正2:GNDピンのみDRILLに重なる度合いを少なくするため中心から上下2個のHOLEを削除

→ これでリプレースし、Ratsnestすると、エアーワイヤにならず、Ratsnet:Nathing

to doになる。

但し、中心までは十字に突っ切らないが、Padとベタの一部が上下左右の一部で重なっている状態。

エアーワイヤにはなってないので、DGNDネットにはベタ接続していると判断。(DGNDネットをハイライトすると繋がっていた)

・ようやく、J1長穴化の、Eagle作業終了。

ガーバー出力→ FUSION PCBのビューワで確認した時に、シルクの位置が悪い個所発見。

液晶コネクタの、CN8と、その上にあるSW4の枠シルクが重なっている。

また、液晶の内側に部品番号があると、液晶を装着した時にそれが見えなくなるので、外側に修正した。

修正後の、ボード画面は以下。

・ガーバー出力~ gerbvと、FUSION PCBのビューワで確認。

・これでよさそうなので、正式発注を済ませる。

■ 2017.7.20

・FUSION PCBからの、P板待ち状態。

本日の夕刻、ステータスが、出荷済になり、運送業者の、FedEXにその情報が送信されたとの

ステータス更新があった。

データに問題は無く、無事製造してくれたようだ。

・ソフトが未だなので、dsPIC33FJ64GP802での、ソフトを検討する。

PIC16F1938とは、だいぶハード構成が異なるので、大幅な変更になる模様。

とは言え、WAVPlayer, easy_audio_fft_analyzerプロジェクト等で、使用実績があるので、

それらのソースを思い起しながら記述していけば、何とかなりそうである。

変更が必要な事柄を整理してみた。

① 液晶へのポート割付けが、大幅に変更になる。

② QVGAライブラリの適用

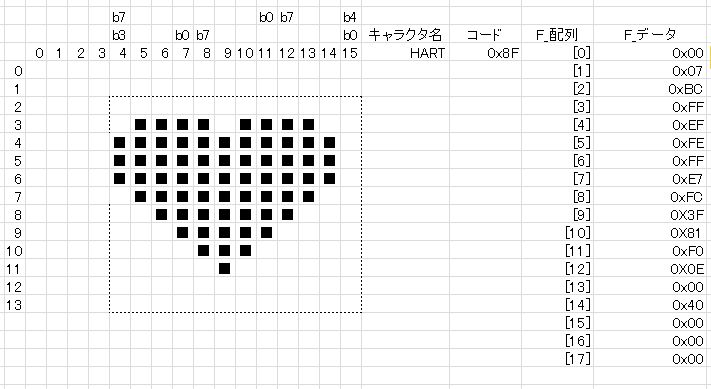

③ アスキーフォント・データ(ASCII12dot.h)に、心拍を示す、ハート・キャラクタを追加

④ ADC設定変更

T3タイマーに同期した、繰り返しAD変換を使う。

⑤ T3タイマーの設定

⑥ SW割込みを、CN割込みで記述(割込みは、これと、ADC割込みの、2種類になる。)

⑦ トリガ検知のアルゴリズムが異なるので、心拍数表示までの手順が異なる。

■ 2017.7.21

・昨日までに、心拍数表示以外は書き上げた。

今日は、③をやって、心拍数表示の部分を追加してみた。

以下の計画図のようなハート・キャラクタをテーブルに追加した。

・ソフトの記述が全て済み、ビルドOK~ HEXまで準備できた。

■ 2017.7.26

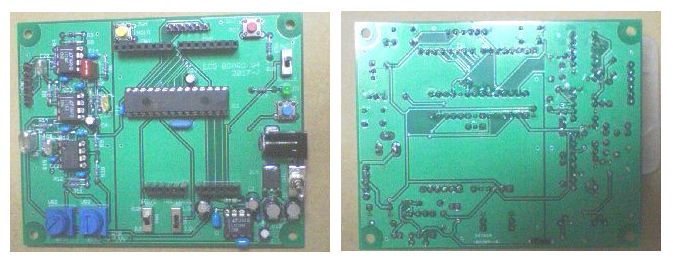

・午前10:30に、P板が届いた。

発注から12日で届いた。前回と同じである。

早速、開封して目視チェックしたが、前回よりも何故かシルクが、全体的に薄い。

(一番懸念していた、長穴(メッキ有り)3個は、問題無く綺麗に仕上がっていた。その他問題ない模様)

・写真では判りずらいかもしれないが、前回のと比較すると、シルクが薄い(シルク文字・線の太さが細い?)

のが判ります。

送信したガーバーデータ(GTOファイル)を再確認したがシルク文字・線の太さは、前回と同様に

最小サイズ=7mil(0.007inch)に指示してあることを確認。

気になったので、「つくり直しサービス」の対象になるか、Fusion

Japanに確認のメールを出した。

■ 2017.7.27

・夜、7時頃、Fusion

Japanから回答があった。

「確認した結果、やり直しサービスの適応は無理です。

基板の生産はロットごとに製造を行うから、ロットが違うと、シルク用のインクは少し違います。

そうすると、生産した基板もちょっと違います。

この点について、何卒ご了承ください。」

とのこと。

データには問題無いようなので、一安心。

シルクの太さが細くなってたのではなく、インクの質にバラツキがあり、今回のは、薄目だったようだ。

個人的な実験基板として使うので問題なし。このことを了承した。

■ 2017.7.28

・今朝から部品実装に入り、午前中には終了。

・実装については大した問題は無かったが、QVGA液晶に、UL024TFを使うことを頭に置いて、

部品配置を決めていたせいで、JA1WBYさんの、代替PT基板を使った場合、幅が若干広い

(両サイド約1mmほどだが、これには今迄、気が付かなかった)せいで、一部、電解コン:C2=47uの

頭が、QVGAボードの角に接触してしまう。

また、ICSPコネクタと、QVGAボードのクリアランスが狭く、液晶を装着した状態では、PICkit2を

差せない。

UL024TFなら問題ないので、このまま進めることにした。(ただ、相変わらず、aitendoの、この液晶は、在庫無し状態が続いているが・・)

JA1WBYさんの、代替PT基板を使った場合は、一部電解コンを寝かせて実装したり、ICSPコネクタは実装

しないで、書き込み時は、PICkit2の方に、ピンヘッダを装着して、それを基板のランドに差して、

書込みを行うことが必要になると思う。

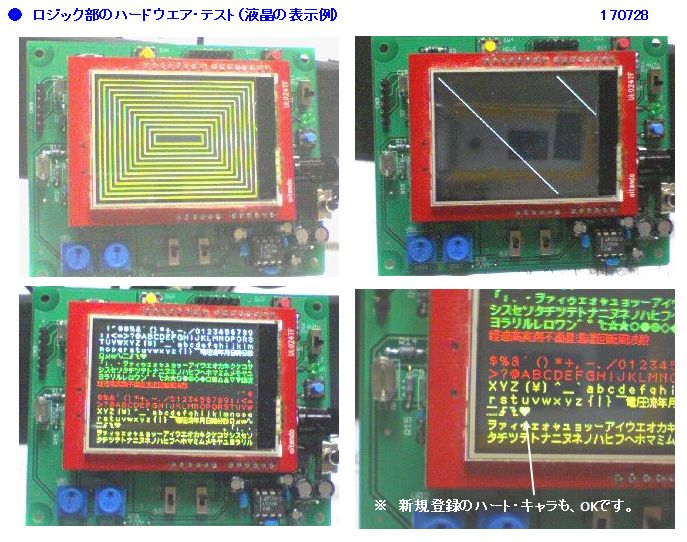

・ハードチェック開始

(1) 電源チェックと、ハードウエア・テスト(SW,LEDを絡ませた、QVGA液晶表示テスト)

① まず、液晶は実装しないで、ICは、LTC1144のみ実装

+5V→ 5.22V

-5V→ -5.20V

VCC→ 3.30V

AVCC→3.28V

各IC、CNの電源ピン全て正常供給を確認した。

② 次に、dsPIC33F実装(未だ、OP AMPは未実装)

①と同じ、測定結果 OK

この状態で、PICkit2を装着して、HEX(ハードウエア・テスト用:dsPIC33F_ECG_HW_TEST.hex)

を書込んだ。ここで注意が必要なのは、必ず、SEC/D

SWと、TRG_LEVEL SWは、下(open)の位置

にして、共用にしているPGCと、PGDラインが、DGNDに落ちないようにして書込むこと。

→ PIC認識・書込みOK

ロジック部のハードウエアは、全てOKを確認した。

尚、動作中の電源電圧は、以下の通り。

+5V→ 5.20V

-5V→ -5.19V

VCC→ 3.29V

AVCC→3.27V

■ 2017.7.29

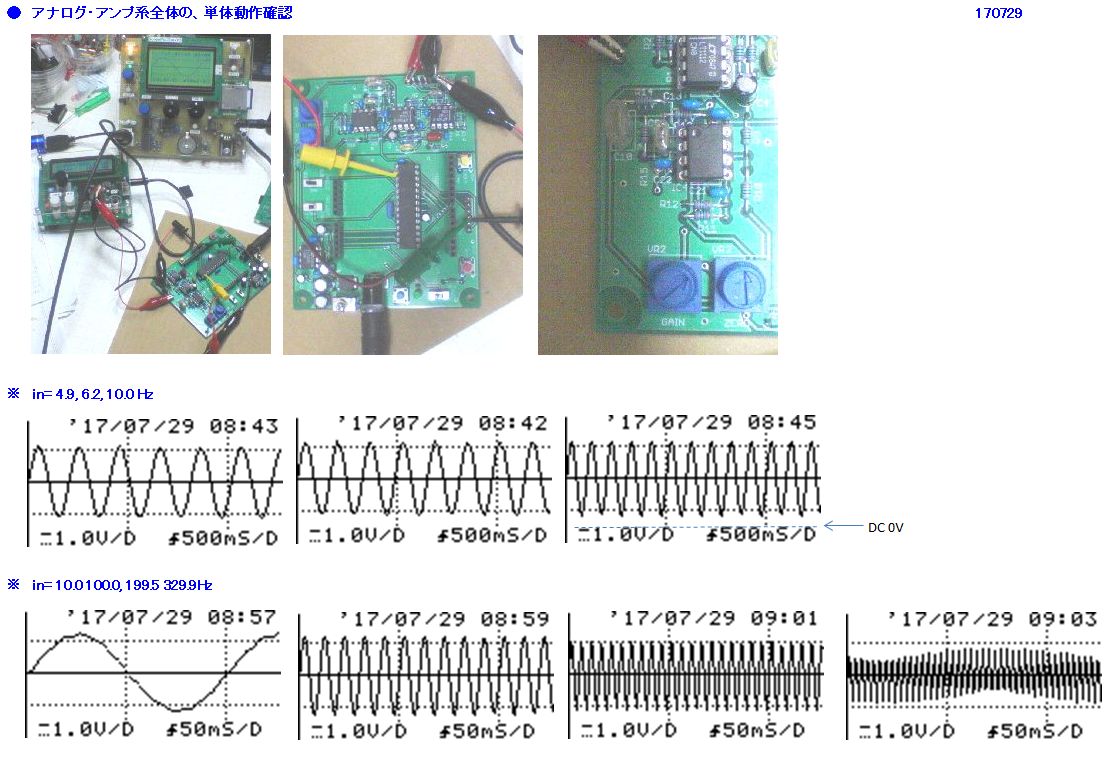

・ハードチェック続き。

(2) アナログアンプ部の単体テストと、電源確認

OP AMP 3個全て実装(PICは実装したままで、液晶は外す)

① この状態で電源チェック OK

+5V→ 5.21V

-5V→ -5.01V

VCC→ 3.29V

AVCC→3.24V

② 数mVオーダーの小電圧出力で、比較的、ノイズの少ない自作FG_V2を使い、アナログアンプ部の単体テスト

を行った。以下の通りこれも、OK(PICの、AN1ピンで波形を取得確認した。)

・本番ソフトを書込み、本番動作チェック開始

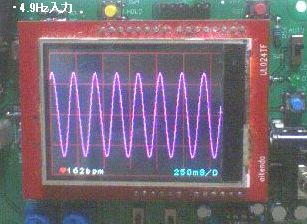

<最初の結果>

① FG_V2で、サイン波入力

条件: 4.9Hz入力・250mS/D・TRG LEVEL= 2.5V

結果:

・ 波形の周期・トリガレベルは、OKだが、bmp表示が正しくない。

サイン波入力に対しトリガ検知(立上り検知)をしているせいもあるが、多少表示が出力レベルの

変化でバラツキ、157~ 162bpmになる。正解は、294bpmなので、約半分の表示である。

・ 500mS/D、TRGレベル= 0Vの切替え動作はOK

・ ややHOLD SWが効きにくい。

波形描画が速くなったので、表示中に合わせて押すのが多少、難しいが、長押しして離せば

OKなので良しとする。

・ デジタル・フィルタは、OK(50Hz入力で完全に消える。)

② 先ほども書いたが、心拍数表示が、約半分になる。

これは、あきらかなプログラムの誤りがあった。

GLCDの時の、sample周期で、bpmを計算していた。

GLCDの時は、500mS/D→ 10mS/ 1S→ 20mSだったが、

QVGAの時は、250mS/D→ 5mS/ 500mS/D→ 10mS

でないと駄目。

これを修正してみた。

表示のバラツキが気になるが、約倍の表示にはなった。

例えば、FG_V2では、最小4.9Hzまでしか出せないので、

自作DDS_OSC(出力に、1/100のATTを入れて、DDS本体のレベルを上げることによってノイズを抑えた。)から

1Hzを入力すると、表示は、60~ 62bpm、又、2Hzを入力すると、表示は、124~

126bpmになる。

(DDS出力を微妙に変化させると、bpm表示もわずかに変化する。)

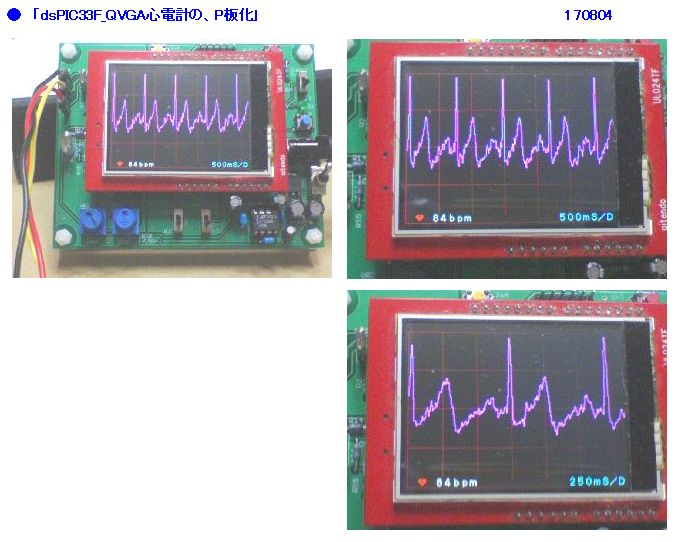

■ 2017.7.31~ 2017.8.4

・心拍数表示のバラツキは、疑似的にサイン波入力で実験していて、非直線部でエッジ検知を

しているせいとも思われるが、最終的に、PICの、AN1ピンの波形ノイズの影響もあると思う。

ノイズが多いと、AD生データを読込む際、読み値がバラツクはずである。

また、これを元に、デジタルフィルタの計算を行っている為、結果的に、波形の歪具合も変化し、

エッジ検知点が、ズレることによってもバラツクと考えられる。

この期間は、そのことについて確証を得るため、色々と試してきた。

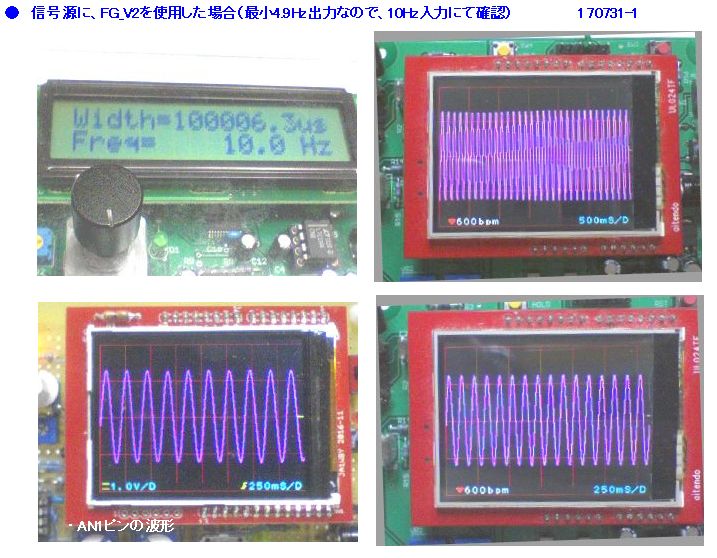

下写真は、比較的出力ノイズの少ない、自作FG_V2で、確認した例を示した。

PICの、AN1ピンの波形に、ノイズは殆ど乗ってない。

このFGの最小出力周波数は、4.9Hzと中途半端なので、10.0Hz出力に設定した。

ECGとしての、心拍数表示は、現実的ではないがバラツキも少なく、上手くトリガが取れると、

両レンジ(500mS/D・250mS/D)で、600bpmと表示し、OKである。

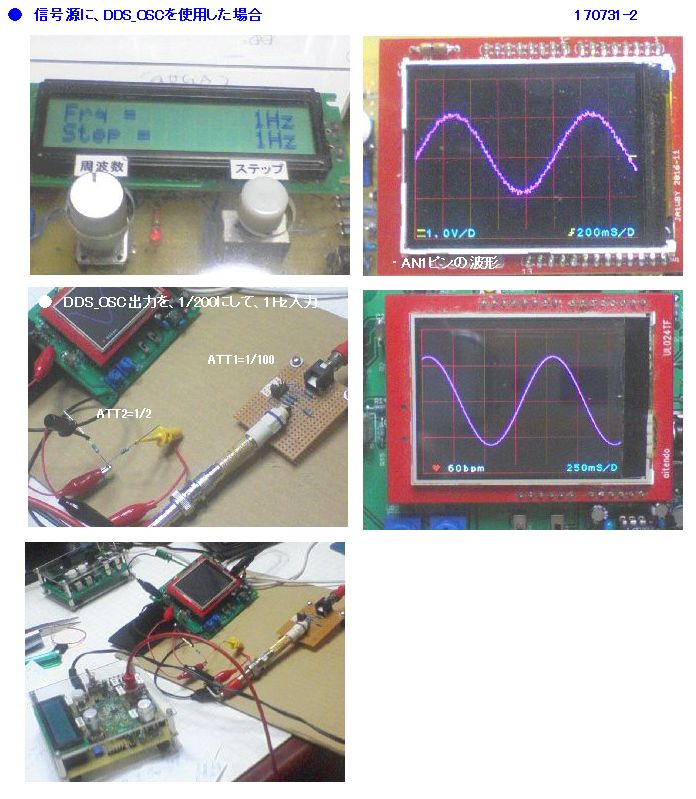

・一方、信号源に、自作DDS_OSCを使用し、出力に、1/200のATTを入れて、ECG入力をした場合

(このOSCは、小出力時のノイズが多いので、ATTを入れて出来るだけ本体のレベルを上げるようにしてみた。)

PICのAN1入力には、御覧のように、これでも目立つノイズが乗っている。

しかし、ECG入力後は、デジタルフィルタの効果で、綺麗な波形が表示されている。

まあ、上手くレベルが合ってトリガが掛かると、1Hz入力で、60bpm表示なので、これもOKとして良いだろう。

また、時々波形は見た目、正常に表示されているのに、0bpmと表示されるのが気になる。

・心拍数表示だが、時々0bpmになるのが気になる。

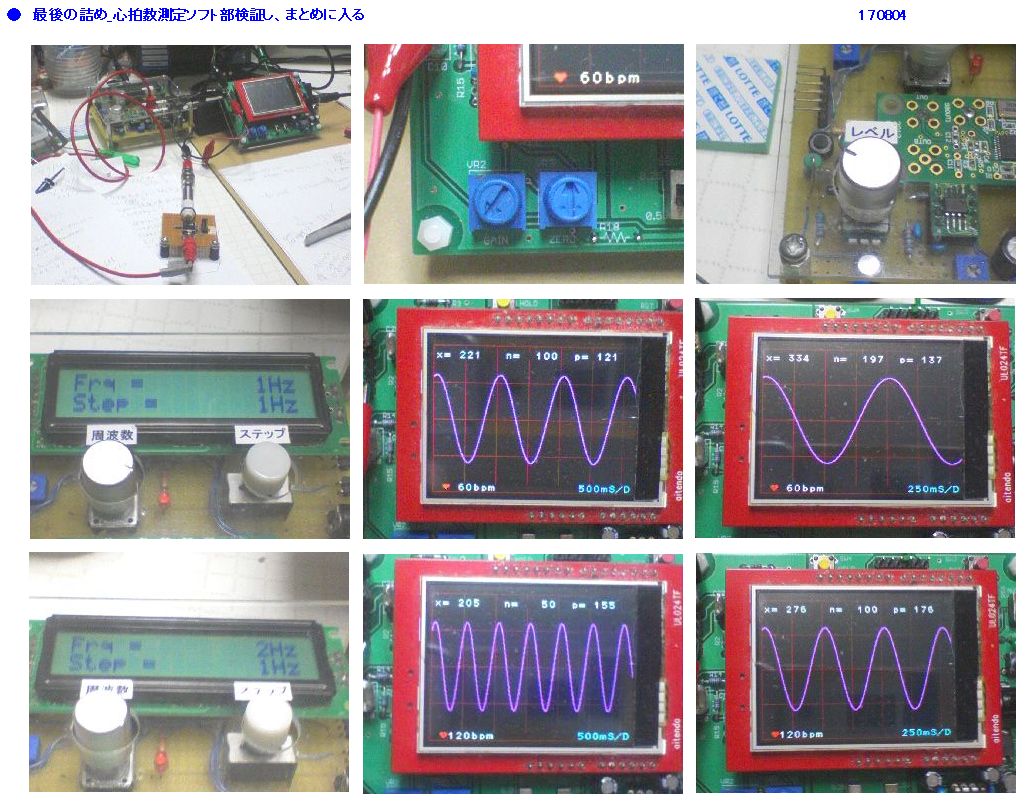

デバッグ用に、このルーチンに使われている変数の、x,

n, p(Point)を表示するようにして、もう少し

プログラムの挙動を確認してみることにした。

pは、初回のトリガ検知ポイント・ xは、2回目のエッジ検知ポイント・ nは、x-pで両検知点の間隔数である。

500mS/Dの場合、心拍数bpm= 6000/nで算出される。

今度は、さらに、DDS_OSC本体の、レベルを出来るだけ上げて入力しようと思い、DDS_OSC出力の、ATTは

1/100にし、ECG側の、GAINを、1倍に設定した。(今迄は、本番と同じ約3倍に設定してた)

これで何とか、時々0bpmになる理由が解った。

これが起きた時の各変数は、p= 189, x= 190, n= 1になることが確認出来た。

この時6000 bpm表示が正解だが、3桁表示としているので、0bpmとなる。

n= 1ということは、初回検知から、1サンプルの時間で次が、検知されたことを示す。

通常では起こらない現象だが、ノイズの影響で、起こっていると推測する。

この現象を避けるために、2回目の検知成立かつ、2回目検知が、1サンプル分の時間で起きたなかった場合のみ

心拍数表示をするようにソフトを修正した。

後、改善点として、最初のトリガか、2回目のエッジが検知されなかった場合は、心拍数が表示されていると

不自然なので、表示しないようソフト修正した。

以下に、1Hz及び、2Hz入力時の、各変数を確認した時の写真を示した。

1Hz入力、250mS/Dレンジの時、n= 197(理論値は、200)となっていて、60bpmと表示しているが、

これは、bpm= 6000/(5 * n)= 6000/(5 x

197)= 60000/985= 60.913 のところ、整数計算しているため

小数点以下が切捨てられる為である。

余り精度には、こだわってないので、これで良しとする。

・これで大方、ソフトも良さそうなので、シングルトリガにも、この心拍数表示アルゴリズムを適応し、

動作確認してOKとなる。

・稼働状態での電源コンディションを取ってなかったので取る。

<条件>

① 500mS/D

② 2.5Vトリガ

③ FG_V2より、4.9Hz入力

<測定結果>

+5V→ 5.20V

-5V→ -5.01V

VCC→ 3.29V

AVCC→3.14V

※ 入力消費電流≒ 0.13A(モバイルBAT使用: 4.97V 0.13A)

・最後に、人体に電極をセットして、ECGとしての動作確認をした。

心電波形も、心拍数表示(私の場合、平均して85bpm程度)も良いようである。

<回路図>

・こちらから、どうぞ→ 「ECG_BOARD_V4」

<最終ソース及びヘッダファイル>

・こちらから、どうぞ→ 「ECG_Scope_V4.c」

/// GLCDライブラリ

colorlcd_libdsPICVH.c

colorlcd_libdsPICVH.h

///

アスキーフォント

ASCII12dot.h