���@�����e�[�}73

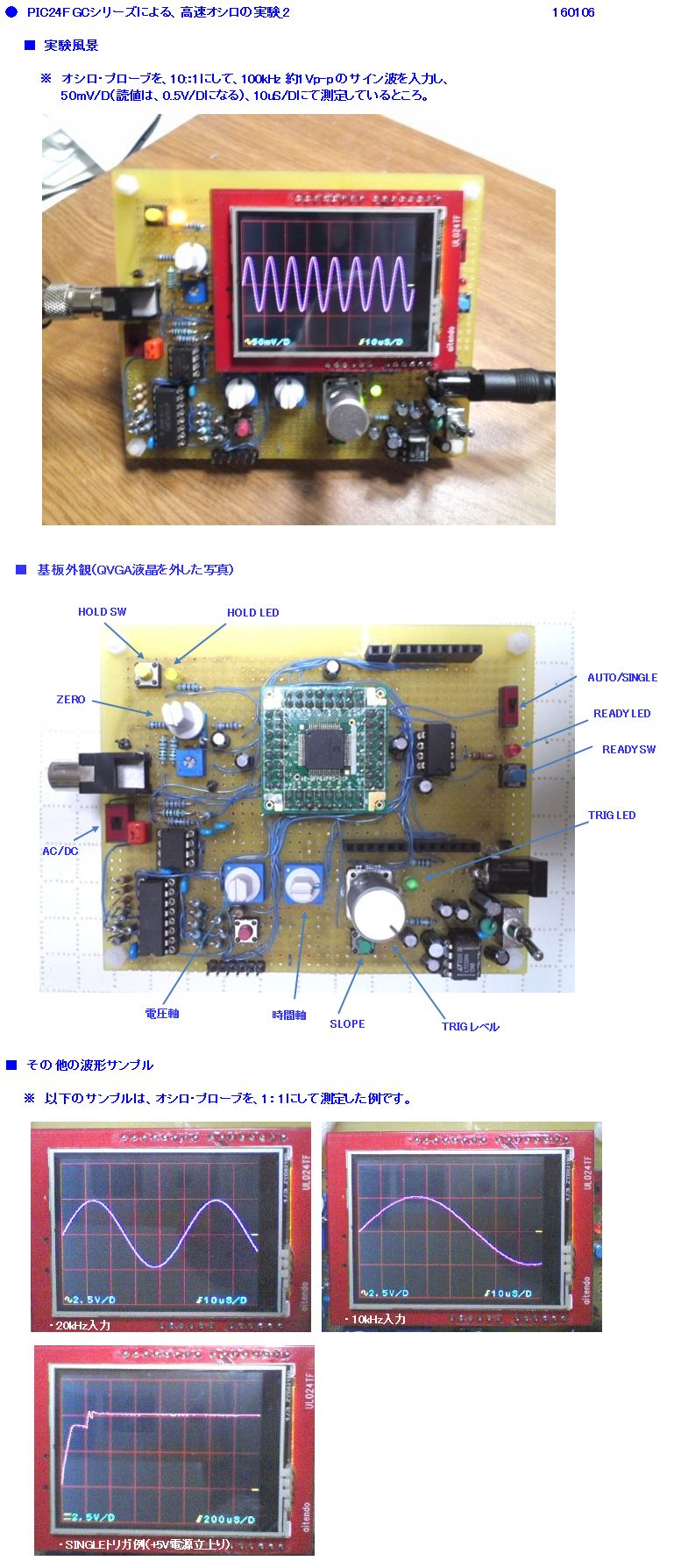

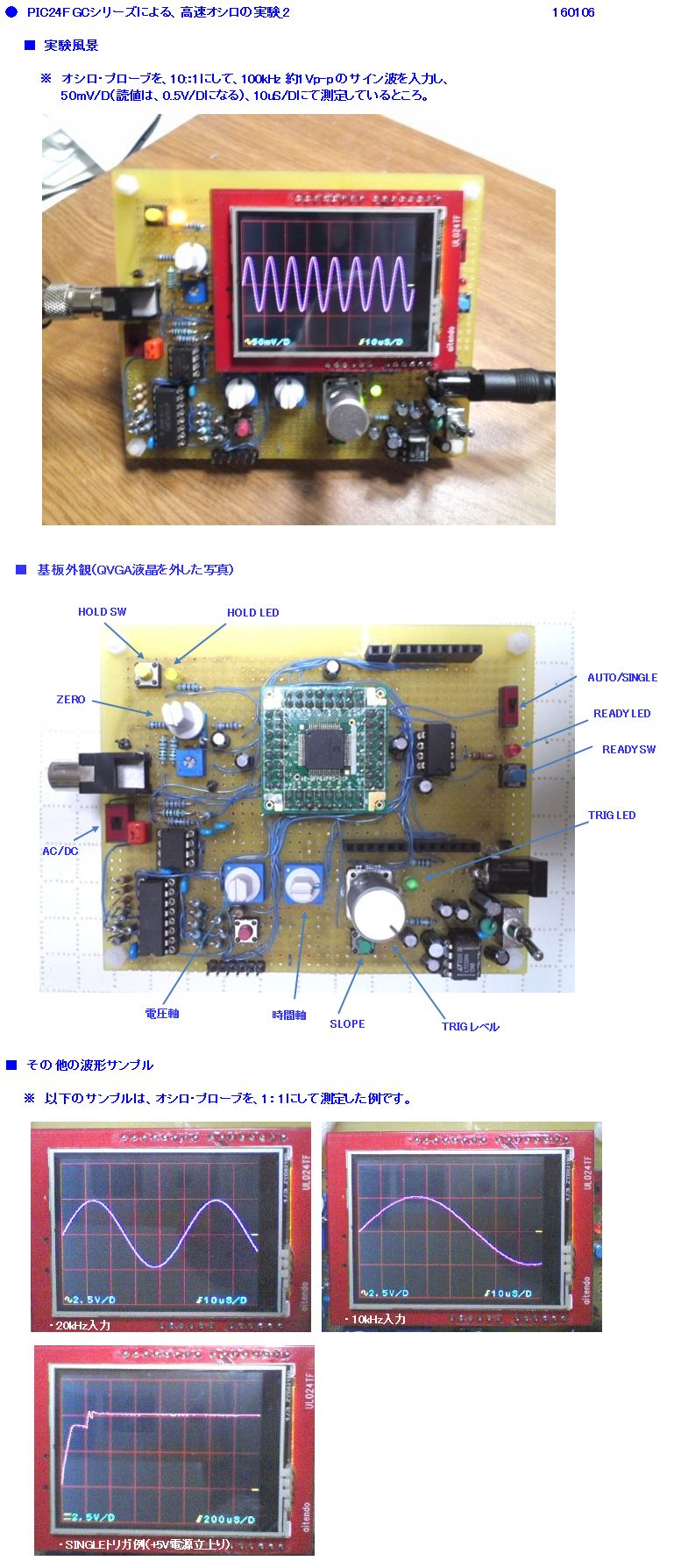

�uPIC24F_GC�V���[�Y�ɂ��A�����I�V���̎���_2�v

�i�O�e�[�}�̊�ɕ��i��lj��i�d�������W�ؑ֒lj����j���āA�����̎���I�V���̂悤�Ɏg����`�ɂ܂Ƃ߂Ă݂܂����B�j

�@

�ȉ��A���̎����̓^���L�ł��B

���@2015.12.21

�@�@�E�O�e�[�}�̎�����A�ŏI�I�ɂ́A�����̎���I�V���̂悤�ɋ@�\��lj����A�g����`��

�@�@�@���悤�Ǝv���A������x�́A�lj����i��z�肵�āA���i�z�u�����߂Ă��܂������A�G���A���m��

�@�@�@���Ă��܂����B

�@�@�@����ł��A���Ȃ�̒lj��ɂȂ�̂ŁA���ɃA�i���O���́A�L�c�L�c�̎����ɂȂ��Ă��܂������ł��B

�@�@�@���Ăǂ��Ȃ邱�Ƃ��E�E�E

�@�@�E����2�̃X�e�b�v�Ŏ�����i�߂悤�Ǝv���܂��B

�@�@�@Step1�F�@���[�^���E�G���R�[�_�iRE�j�ɂ��g���K�����@�\�̒lj������{HOLD SW �lj�����

�@�@�@Step2�F�@�A�i���O��H�S�ʉ����iAC/DC�ؑցE�d�������W�ؑ֒lj��j

�@�@�@�@�@ �@�@�@�V���O���E�g���K�E���[�h�̒lj�

�@�@�E�܂��́A�������ŁA��Step1,2�̒lj��@�\��S�Ėԗ�������H�}�̍쐬����J�n���A

�@�@�@RE�ɂ��g���K���x�������̎d�l���������邱�Ƃɂ����B

�@�@�@RE�ɂ��g���K���x�������@�\�́A���m�N��GLCD���g�����I�V���i�����e�[�}62�j�ō̗p���Ă܂����A

�@�@�@�J���[QVGA�I�V���ł́A���߂Ăł��B

�@�@�@�A�b�v�_�E��SW���g������́AQVGA�I�V��V4�̎��ɂ��邪�A�g���K���x���E�}�[�J�[�\���̈ʒu�́A

�@�@�@�ڈ����x�̂��̂ł����B

�@�@�@����́A�o���邾�����m�Ȉʒu�ɁA�}�[�J�[��\���������Ǝv���܂��B

���@2015.12.22

�@�@�ERE�ɂ��g���K���x�������@�\�d�l���l����B

�@�@�@Y�����𑜓x�F240dot�̐�������A�}�[�J�[�`�悪�A�ߎ��I�Ȉʒu�i���Ȃ�߂����E�E�j�ɂȂ���

�@�@�@���܂����A���Ԃo�I�ɂ͈�a���́A����Ȃɖ����Ǝv���̂ŁA���̂܂ܐi�߂Ă݂�B

�@�@�@Y�����̉𑜓x���A256dot����A1dot������AAD�ϊ��l�ŁA1024/256=4�ɂȂ�̂ŁA

�@�@�@0�`3V�܂ł̃g���K�d���������A�}�[�J�[�����m�Ȉʒu�ɕ\���ł��邪�A

�@�@�@240dot�̓��AY���W�����A233dot���g���ăt���X�P�[���Ƃ��Ă���̂ŁA1dot�������AD�ϊ��l��

�@�@�@4.395�Ɗ���Ȃ��B

�@�@�@�Ȃ̂Ń��x�������́A1024���A256�����Ƃ��A�}�[�J�[�\���́A233dot�������ł��Ȃ��̂�

�@�@�@���̕��̕\���݂̂Ƃ����B

�@�@�@����āA�������x�����A1.5V�i512�j�Ƃ��āA�|���́A��0.1�`�@�{���́A��2.9V�́A�g���K���x���͈�

�@�@�@�ƂȂ�B

�@�@�@�ȉ��ɁA�g���K�d�l���܂Ƃ߂܂����B

�@�@�@���g���K�d�l��

�@�@�@�@�E�����l=512�i�Z���^�[�F1.5V�����j�A1STEP

�}4�i��12mV�����j

�@�@�@�@�E�Z���^�[�F512�𒆐S�ɁA�}116�e�b�v�ɂȂ�B

�@�@�@�@�E117�X�e�b�v�ڂ́A+���́AY���W�̏��232���I�[�o�[�i233�j����̂ŁA

�@�@�@�@�@POT=976�i116�X�e�b�v�ڂ́A�g���K�l�j�Ƃ��A�|�����A117�X�e�b�v�ڂɁAY���W�̏��0���I�[�o�[

�@�@�@�@�@����̂ŁA POT=48�i116�X�e�b�v�ڂ́A�g���K�l�j�Ƃ���B

�@�@�E�������ɂ���H�}�쐬�����B

�@�@�@�܂��A�lj����i�̃��X�g���쐬�����B

���@2015.12.23

�@�@�E�lj����i�̎�z���ς܂���B

���@2015.12.24

�@�@�EStep1�̓��e�ȊO�ŁA�lj����悤�Ǝv���Ă������Ƃ��������̂ŁA�������邱�Ƃɂ���B

�@�@�@����́A�T���v�������̒Ⴂ���̃����W���A�������lj����邱�Ƃł���B

�@�@�@�ŏ��̎����ł́A�����I�V���Ƃ������ƂŒႢ���́A�Ȃ��Ă����̂����A����ł͎��p�I�ł�

�@�@�@�Ȃ��̂Œlj����邱�Ƃɂ����B

�@�@�@�n�[�h�I�ɂ́A�ؑ�SW�Ɏg���Ă���A10�i�̃��[�^���E�f�B�b�vSW���A16�i�̂��̂�

�@�@�@�ύX���K�v�ł���B

�@�@�@�����Č��݊��t�����Ă���A0�`9�ȊO�́A10�`15�ɁA���̒Ⴂ�����W�����t���邱�ƂɂȂ�B

�@�@�@�Ⴂ���̊��t���͈ȉ��̂悤�ɁA���߂��B

�@�@�@�@10�F20mS/D�iSMP= 500u�j

�@�@�@�@11�F50mS/D�iSMP= 1250u�j

�@�@�@�@12�F100mS/D�iSMP=2500u�j

�@�@�@�@13�F200mS/D�iSMP=5000u�j

�@�@�@�@14�F250mS/D�iSMP=6250u�j

�@�@�@�@15�F500mS/D�iSMP=12500u�j

�@�@�@�������ɁAT2�́APR2�ƁAPS2�̐ݒ�l�����߂čs���悢�B

���@2015.12.25

�@�@�ERE�ɂ��g���K���[�`���̏������́A����Scope V2�̃\�[�X�ɂȂ���Đi�߂�悢�B�i���C�����[�v�����j

�@�@�@����SW�����L�q�iCN�����݁j�̋L�q�́A������PIC24F�n�Ɠ����ƍl���ėǂ������B

�@�@�E���i�͑S�č����͂������A�v��ʂ�A�܂��́ARE�g���K�{SLOPE�ؑց{HOLD

SW�̂Ƃ���܂ł�

�@�@�@�v���O������p�ӁiTEST_2�j���Ă���A���̕����̉������s���A�`�F�b�N���s�����Ƃɂ���B

���@2015.12.26

�@�@�EStep1�܂ł̃\�[�X�����グ��B

�@�@�@�R���p�C��OK�AHEX�܂ŏ����ł���B

���@2015.12.27

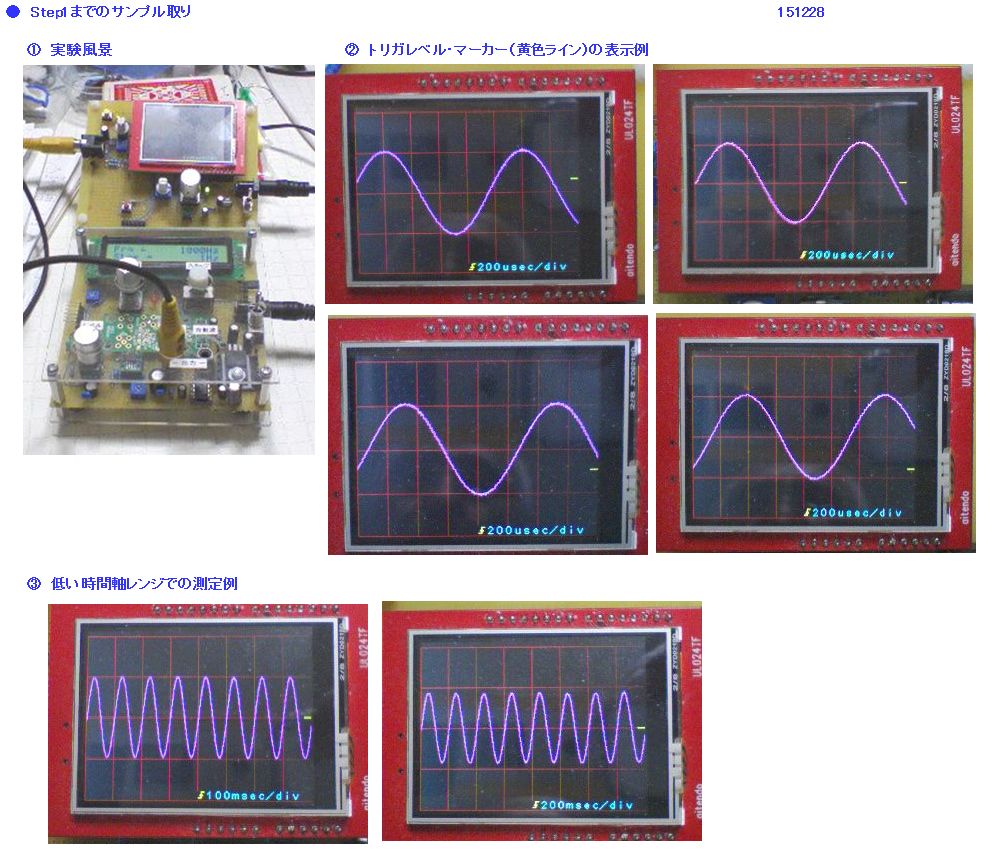

�@�@�EStep1�܂ł̊���������������B

�@�@�EHEX��������ŁA�`�F�b�N�ɓ���B

�@�@�@�܂��͑ʖځB�g���K���x���E�}�[�J�[�\���ƁA���ۂ̃g���K���x���̃v���X�����啝�ɍ���Ȃ��B

�@�@�@����̓C�[�W�[�~�X�ŁA�v���X���̃X�e�b�v���A4�łȂ�16�ɂȂ��Ă����B

�@�@�@��������A�������������B

�@�@�@�����̎v���Ⴂ�̂����ł������B

�@�@�@���̂��A�t����Y�����F240dot��S�č��W���Ɏg���Ă���Ɗ��Ⴂ���Ă��܂����B

�@�@�@233dot�������W���Ƃ��Ďg���Ă���̂ł������B�i�ŏ��̐����̒ʂ�ł���B�j

�@�@�@�Ȃ̂ł��͈̔͂ŁA���x���ƕ\�������킹��悤�C������OK�ɂȂ�B

�@�@�@SLOPE�ؑւƁAHOLD SW�̋@�\�͖��Ȃ������B

�@�@�@����ŁAStep1�܂ł̓����OK�ƂȂ�B

���@2015.12.28

�@�@�EStep1�܂ł̃T���v�������s�����B

���@2015.12.29�`�@2015.12/31

�@�@�EStep2�̏����ɓ������B

�@�@�@�ʓ|�ȁA�lj��������s���B

�@�@�@���߂��猜�O�͂��������A���Ȃ��X�y�[�X�̒��ɁA�lj����������������B

�@�@�@��G�b�W���ɂ��A���[�h�}�����������ƁA�ƂĂ������ł��Ȃ��̂ŁA�����͍w�����Ă�����

�@�@�@�s���o�C�X�ŁA0.8�ӂ̌����J�����B

�@�@�@�������Ⴍ���āA�M���M�����̂���Ƃ���ŃJ�b�g���Ȃ������̂������Ȃ������B

�@�@�@�Ȃ�Ƃ��A12/31 15:00���A���������ƂȂ����B

�@�@�EStep2�܂ł̃\�t�g�������グ���B

�@�@�@�R���p�C��OK�`�@HEX�܂ŏ����ł����B

�@�@�E�܂�HEX�������݁A�lj�IC���������āA�f�o�b�O�ɓ������B

�@�@�@���낢��s����o���B�@�@

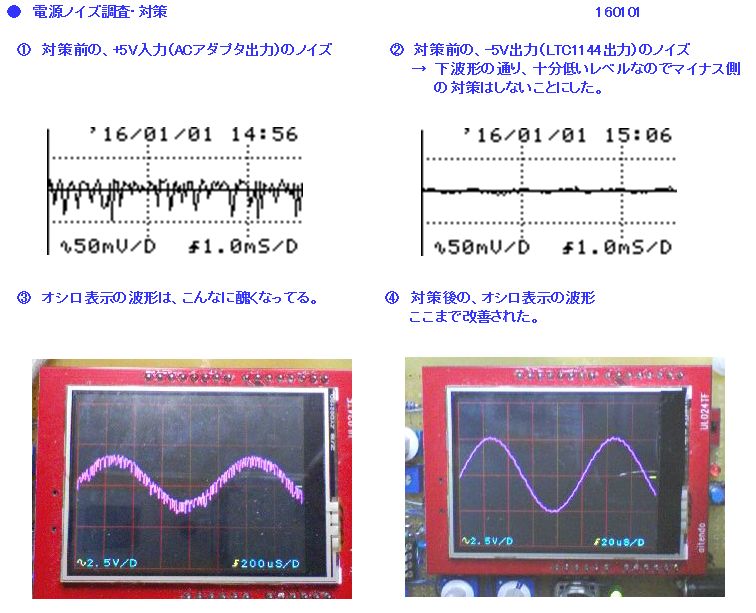

���@2016.1.1

�@�@�E�s���������܂܁A�V�N���}�����B�i���N�������������悤�ȁE�E�E�j

�@�@�E���ʓI�ɂ́A�m�C�Y���������ẮA���OK�ɂȂ����B

�@�@�@�ȉ��ɁA���������s��_�ƁA�Ώ������ɂ��Đ������A��L���Ă݂��B

�@�@�@�����������s��_�ƁA�Ώ�������

�@�@�@�@(1) �A�i���O��

�@�@�@�@�@�@�@�@����ZERO�ɂāAOFFSET VR�ŁA�Z���^�[���x���ɏo���Ȃ��H

�@�@�@�@�@�@���@�z���~�X�������B

�@�@�@�@�@�@�@�@ �������iOP�A���v�́A�|�s�����AAGND�ƃu���b�W���Ă����B����̉����̎��u���b�W

�@�@�@�@�@�@�@�@ ���Ă��܂����悤���B

�@�@�@�@�@�@�@�@ �������OK�ɂȂ�B

�@�@�@�@(2) �f�W�^����

�@�@�@�@�@�@�@�@�d�������W��ؑւ��Ă��A"50mV/D"�\���̂܂ܕω����Ȃ��B

�@�@�@�@�@�@�@�@ �܂��AAC/DC�ؑփX���C�hSW�̓Ǎ��݂�NG�ŁA�ؑւ��Ă��ADC�L�����N�^�\���̂܂܂ɂȂ�B

�@�@�@�@�@�@���@���Y�|�[�g�iRD�j���f�t�H���g�̃A�i���O�s���ݒ�ɂȂ��Ă����B

�@�@�@�@�@�@�@�@ ANSD= 0;�ݒ�lj��Ńf�W�^���s���ɂ�����OK�ɂȂ�B

�@�@�@�@�@�@�A�@AUTO/SINGLE�ؑփX���C�hSW�iRF3�j�͓Ǎ���ł���悤�ł��邪�ASINGLE�ɂ��āA

�@�@�@�@�@�@�@�@ READY SW�������Ă��AREADY LED���_�����Ȃ��B

�@�@�@�@�@�@���@READY SW�ƁAAUTO/SINGLE�ؑփX���C�hSW�͐��������삵�Ă��邱�Ƃ��m�F�����B

�@�@�@�@�@�@�@�@ �����LED�̓��삪���������B

�@�@�@�@�@�@�@�@ ���ǁA�g���Ă���LED�̃J�\�[�h�ʂ̃J�b�g���͂����肵�Ă��Ȃ��āA�������ԈႦ�Ď���

�@�@�@�@�@�@�@�@ ���Ă����B�C����OK�ɂȂ�B

���@2016.1.2

�@�@�E�c��̃m�C�Y���������ł����B

�@�@�@����A��J���Ă��邱�Ƃł��邪�A����͂������傤�Ԃ��낤�ƁA+5V���C����LC�t�B���^�͏Ȃ��Ă����B

�@�@�@�@�@�@���낢���������A���ǁA�m�C�Y���́A+5V�iAC�A�_�v�^�o�́j�̓d���m�C�Y�i�I�V���Ō����0.1Vmax�ʁj

�@�@�@�@�@�@ �ł������B

�@�@�@�@�@�@ �����ɂ����́ALC�Ό^�t�B���^��lj������B

�@�@�@�@�A�@�������ꂾ���ł͑ʖڂŁA���̃m�C�Y����ԉe�����Ă���A4051�̃A�i���OSW�ƁA��i��

�@�@�@�@�@�@

�d���o�b�t�@�A���v�̃p�X�R���̗e�ʕύX�ƒlj����s�����B

�@�@�@�@�@�@�@�E4051��+5V�p�X�R�����@0.1u��10u�ɕύX������Ƀp����10u��lj��B

�@�@�@�@�@�@�@�E�d���o�b�t�@�A���v��+5V�p�X�R�����@0.1u�ƃp���ɁA10u��lj��B

�@�@�@���A�`���[�W�|���v�o�́i-5V�j�̃m�C�Y�̉e���͖w�ǂȂ��悤�Ȃ̂ŁA�����ɂ�LC�t�B���^��lj����ĂȂ��B�@

�@�@�@�����A�ŏ�����傫�ڂ̃R���f���T100u���������Ă������B

�@�@�@���@�@�A�A�̉����ŗǂ��Ȃ����B

�@�@�@�ȉ��ɂ��̗l�q���A�b�v���܂����B

�@�@�@�i������������Ă��鎞�Ɍ���āA�t���̃K���X�ʁi�E���j�Ƀq�r�����Ă��܂������߁A���̕�C�̂��߂�

�@�@�@

���r�j�[���e�[�v�ŕ�C�����̂��ʐ^�ɂ��ʂ��Ă��܂����A�������̂قǂ��B���@����������܂����B�j

�@�@�@�����A������ƋC�ɂȂ�_����B

�@�@�@�n�C�����W�i20uS/D, 10uS/D�j�ŁA���Ԏ����A�����ς��g����1������\�������ꍇ�A���������A

�@�@�@�g�`���c��ŕ\������銴��������B�@

���@2016.1.3

�@�@�E����̃n�C�����W�̔g�`�\�����A��c�ތ��ۂ����A���ǂ́A���i�̃A�i���OSW�i4051�j

�@�@�@���A������]���ɍw�����Ă��������̂Ɍ���������A�R�̂悤�ɁH�@�Y��Ȕg�`�\���ɂȂ����B

�@�@�@���̘c�̌����́A�͂����肵�Ȃ����A���͂�AC�U�������̂悤�ȋC������B

�@�@�@�Ƃ���������ŗǂ��Ȃ����̂�OK�Ƃ����B

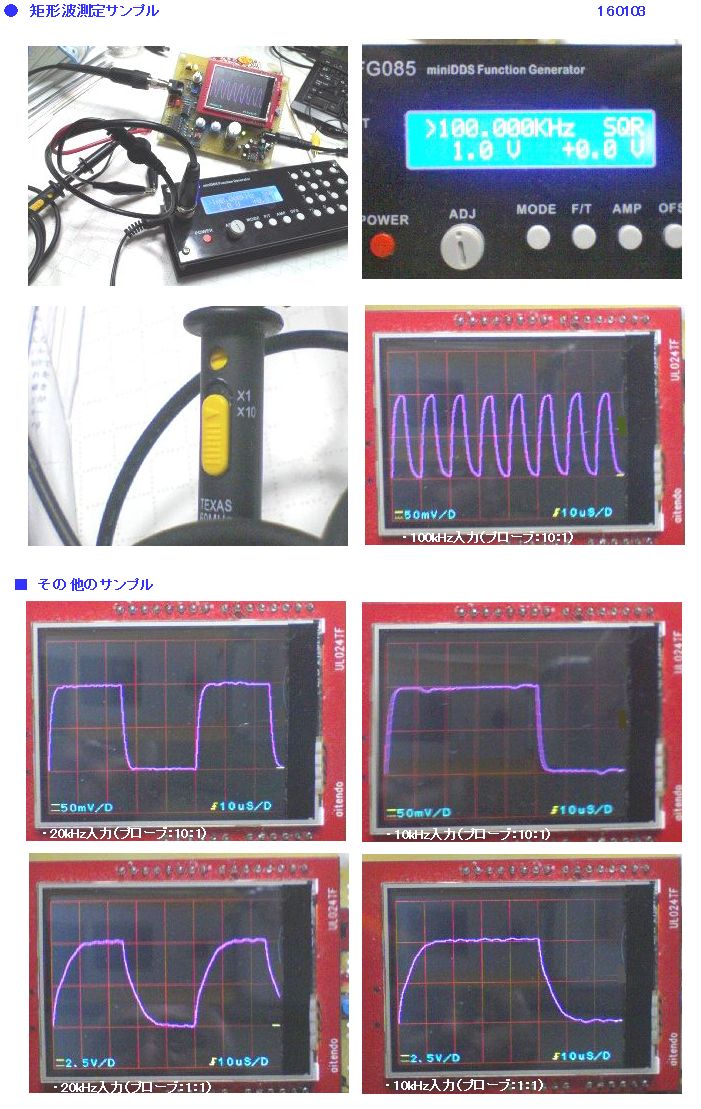

�@�@�E������`�g���͂̔g�`�m�F�����ĂȂ������̂ŁA����Ă݂܂����B

�@�@�@�ȉ��ɁA��`�g���͎��̃T���v�����A�b�v���܂��B

�@�@�EDC�����W�ɂāA�d�r���璼���d����^���A�e�d�������W�̊m�x���m�F�����B���@OK

�@ �EOFFSET��VR���A�N���e�B�J���߂��āAZERO�_�����킹���炢�B

�@�@�@����͍ŏ����番�����Ă������ƂȂ̂����A�������Ⴍ���ĉ������ڂɂ��ꂸ���̂܂܂ɂ��Ă����B

�@�@�@�����̂悤�ɁAVR�̗��[�ɁA20k��lj������B����łقǂ悢�����ɂȂ����B

���@2016.1.4

�@�@�E�x�ꂽ���A���̎��_�̓d���R���f�B�V�������m�F�����B

�@�@�@+5V�F5.18V

�@�@�@-5V�F-4.96V

�@�@�@VCC�F3.29V

�@�@�@AVCC�F3.26V

�@�@�@+5V���͓d���F0.14A

�@�@�E�Ō�ɁASINGLE�g���K�E���[�h���`�F�b�N�����B

�@�@�@AUTO/SINGLE�̐ؑւ��AREADY SW�̓����͂悳�����Ȃ̂����AREADY

LED�̓��������������B

�@�@�@SINGLE���[�h�ɂ��āAREADY SW�������A�g���K�҂��iREADY

LED ON�j�ɂ�����ԂŁA�M������

�@�@�@�����AAUTO�ɐؑւ������AREADY LED���������Ȃ��H

�@�@�@����̓C�[�W�[�~�X�ł������B

�@�@�@AUTO���[�h�����̍ŏ��ɁALED OFF�ƁAREADY�t���O�ނ̃��Z�b�g�������Ă����B

�@�@�@�����lj����āASINGLE���[�h���AOK�ɂȂ�B

�@�@���@����őS�Ă̋@�\��OK�ɂȂ����B

�@�@�@�@

����P�[�V���O�͓��ɂ��ĂȂ����A������͕t���āA�n���_�ʂ�ی삷��Ɠ����ɁA������

�@�@�@�@ �^�J�`�d�@�H�Ƃ́A�u�s�h�^�`���g�X�^���h

�s�h-70S�v����t���āA�ߒu���\�ɂ��A���쐫��

�@�@�@�@ �悭���܂����B

���@2016.1.6

�@�@�E�ŏI�I�ȁA�O�ςƔg�`�T���v�������܂����B

�@�@�@���̃y�[�W�g�b�v�̎ʐ^���Q�Ƃ��Ă��������B

���ŏI��H�}��

�@�E�����炩��A�ǂ������@�uPIC24F_GC_�����I�V��������H_2�i1/2�j�v�@�F�@�f�W�^�����{�A�i���O��2

�@�@�@�@�@�@�@�@�@�@�@�@�@�@�@�@�@�@�@�uPIC24F_GC

�����I�V��������H_2�i2/2�j�v�@�F�@�A�i���O��1

���ŏI�\�[�X��

�@�E�����炩��A�ǂ������@High_Speed_Oscillo_Test_2.c

���@���̑��ɁAQVGA�t�����C�u�����ƁA�t�H���g�f�[�^�i�w�b�_�t�@�C���j���K�v�ł����A

�@�@�@�@����́A�O�e�[�}72�̂Ɠ��l�Ȃ̂ŁA��������Q�Ƃ��Ă��������B

���@�����e�[�}1�ɖ߂��@�@�@TOP PAGE�ɖ߂��@�@�@�����e�[�}74�ց@��

�@

�@

�@

�@