● 実験テーマ61

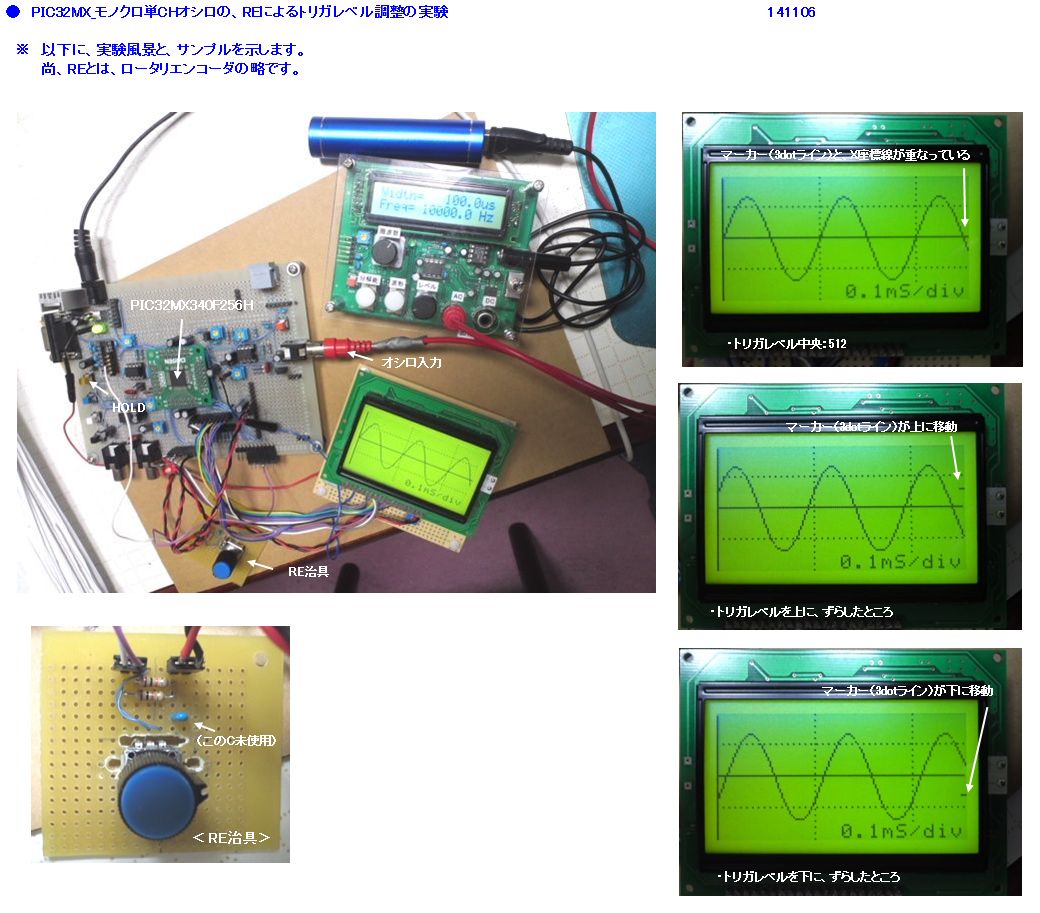

「PIC32MX_モノクロ単CHオシロの、REによるトリガレベル調整の実験」

(RE:ロータリエンコーダによりトリガ調整する実験です。今回、良い結果が得られたので報告します)

・以下、この実験の顛末記です。

■ 2014.11.1

・以前、実験テーマ30で、タクトSWを使っての、トリガレベル直接入力の実験はしているのだが、

SWなので、なにせ操作性が悪い。

この操作性がよくならないものかと考え、RE(ロータリエンコーダ)に置換えたらどうかと、

思いついた。

しかし、応答性とかが心配なので、実験にて試してみることにした。

<最初に考えた実験仕様>

① トレーニング基板使用

② REには、安価なメカ接点式のものを使う。(秋月で、80円で販売している、「EC12E2420801」)

② RE治具を、ポートに接続( RE-A出力を、RF5、RE-B出力を、INT0(RF6)に接続)

③ RE-Bの立下りで、外部割込み(INT0)を起動し、そこで読込み処理を行う。

④ 時間軸は、0.1mS/div固定にする。

⑤ 肝心な、トリガ仕様は以下の通り。

⑤-1: 可能な限り、0~1023(0~3V)fullレンジを可変できるようにする。

⑤-2: 初期値=512(センター:1.5V相当)、1STEP

±5(約15mV相当)として、10bitfullレンジを

出来るだけカバーすると、センター:512を中心に、±102ステップになる。

103ステップ目は、±共に、フルスケール値をオーバーするので+103側は、強制的に1022にし、

-103側は、2にする。

⑤-3: トリガ設定値が判るように、液晶画面、右隅に、その値を表示する。(例:Trg:0512)

■ 2014.11.3

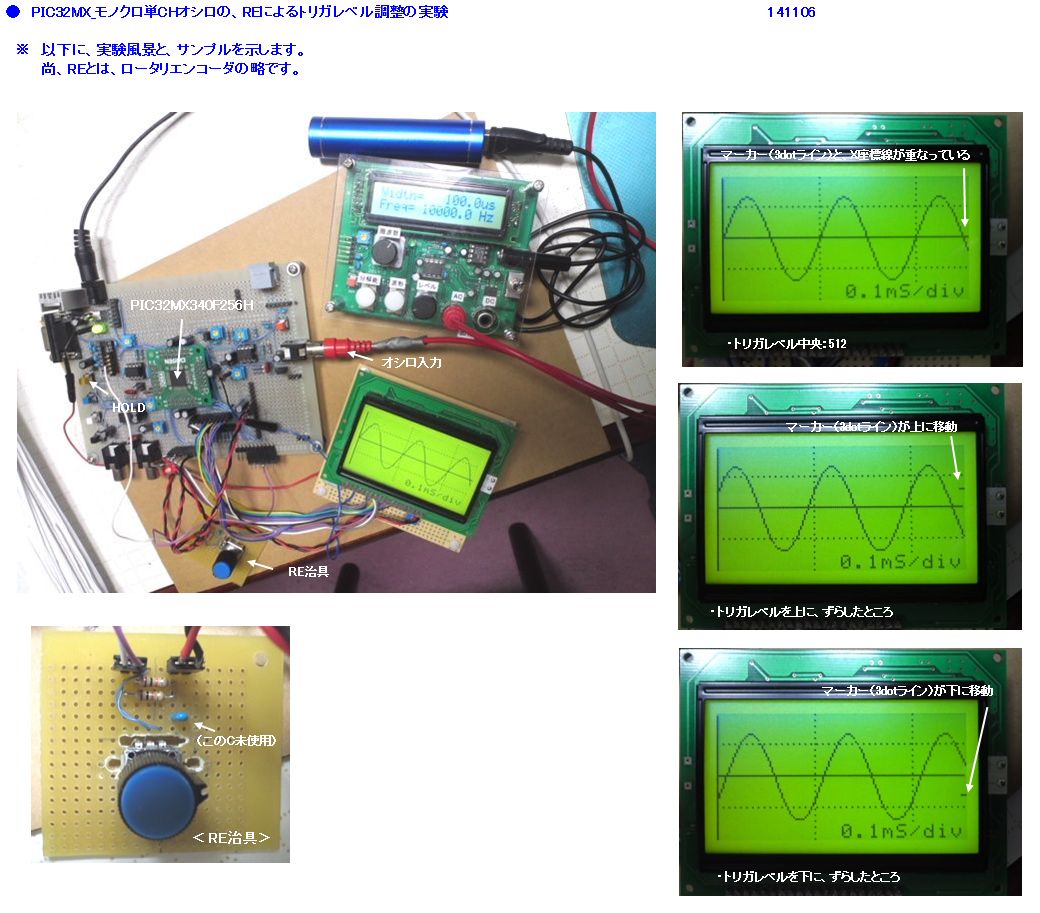

・REを外部割込みで読込む方式で、ソフトを書き上げた。

HEXを書込んで、動作チェックするも、オシロ動作がおかしい。何か、波形表示が違う。

これは、イージーミスだった。

0.1mS/div固定としたため、イニシャライズの、プリスケーラの値を、PR3=

399;から、PR= 79;に変更

したが、ここを書く時に、PR3= PR3= 79;と、元々書いてあった、PR3=を残したまま書いてしまったこと

に気が付かずコンパイル。

これでも、コンパイルエラーは出ない。

もちろん普通こんな書き方はしない。

PR3= 79;と修正し、オシロ表示はOKとなる。

■ 2014.11.4

・昨日いろいろやって、基本的に動かすことは出来た。

昨日のソースは、このようになっています→ Scope_PIC32MX_RE_TRG_TEST_141103_2.c

しかし、メカ式の弱点なのか、チャッター対策をソフトでしても、完全には上手く行かず時々数値飛びを起こす。

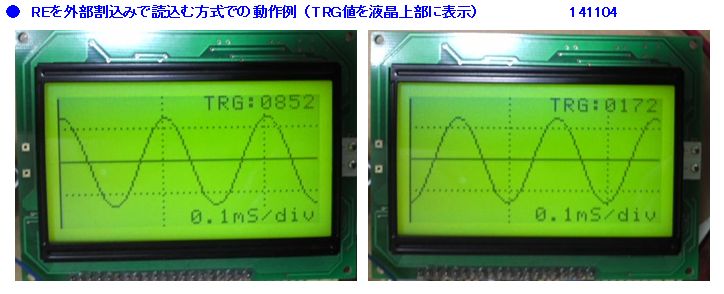

今日、REの各相のタイミング波形を取ってみたが、なんだが、相の出方が違う??

これでも、回転方向と、数値増減の関係は合っていたので、波形を見るまでは、疑わなかった。

ただ、右回転の場合、これじゃB相の立下りエッに対して、A相の立下りが殆ど同じになっているので、

誤動作の可能性が大!!

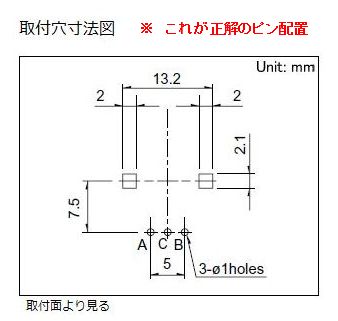

※ この原因は、治具の配線ミス

BとC((コモン)がテレコになっていた。

違う型番の、REのピン配置を見ていたようだ。

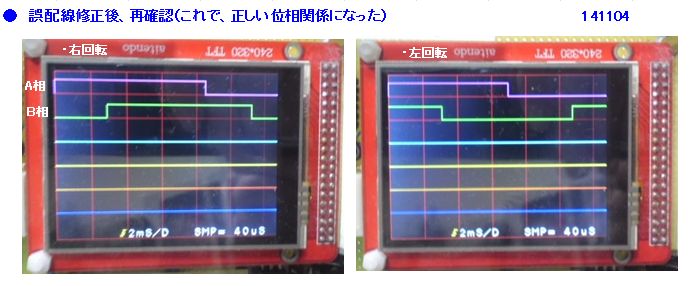

・早速誤配線を修正し、位相関係を再確認した。

・チャタリングは実測したところでは、目立っては発生してない感じ。

時々立下りの方に多く発生している模様(1mS以下)

REの規格では、チャタリング:3mSmax, バウンズ:2mSmaxとなっていたが、チャタリングが立上りで、

バウンズが立下がりと考えて良いのだろうか、今のところ不明である。

トータルで考えて、5mSmaxとすれば、今、B相の立上りに入れているウエイト値は、100mSであるが、

50mSに変更しても大丈夫と思い変えてみた。

結果、そんなに変わらない感じだったので、これにFIXした。

また、昨日の配線ミスの状態でも動いていたのだが、数値飛びが目立っていた。

配線ミス修正で、良くなるのかなと思いきや、期待するほどではなかった。

時々発生する数値飛びの幅が少なくなってはいる。

REのリードは、ほぼ、波形更新間隔(0.3秒)の間で行われるので早く回した場合の応答性はあまり良くない。

まあ、アナログVRにはかなわない。

操作的には、トリガポイントをうんと端に寄せた場合、これをセンターに戻す時、何回も回さなければならない

ので操作が煩わしい感はある。

これを改善するには、プッシュSW付きの、REを使い、プッシュしたら強制的にセンター値の戻す機能を付けれ

ばよいかもしれない。

メカ接点式のREを使う限り、ある程度の、数値飛びは、しょうがないかもしれない。

光学式のを使えば、かなりよくなるはず。

但し高価:80円に対し、1800円

■ 2014.11.5

・何も割込みで、REを読込まなくても、メインループで、読込んでもよいはずである。

割込みで読込む場合、波形描画更新中のところで、RE割込みが入ると、表示が、おかしく(はっきりとチラツク)

なるので、その間は、外部割込みを禁止して、更新が終ったら、再許可するような記述が必要であるが、

メインループで読込めば、その必要はなくなる。

メインループで、波形描画更新間隔の、0.3秒ウエイトのところで、エッジセンスを、1mS間隔で、300回実施

させるように、forループを追加してみた。

こうすれば、波形描画更新間隔の、0.3秒ウエイトも兼ねることになる。

つまり、300回サンプル(RE-B相の立下りのエッジセンス)のまとめ読みを行う訳だ。

あと、まだ気になっているところもある。

トリガ値を表示する方法は、上手く行ったが、

直感的ではないし、波形表示の邪魔にもなる。

前考えた、5ステップのトリガレベルでは、細かい(約14mV)ステップの

トリガ電圧を与えることが出来るが、

液晶右端にバー表示した場合、液晶Y方向のドット数(64ドット)と合わず、目安程度の表示となってしまう。

なので、ステップ分解能は下がってもよいので、Y方向のドット数=64

に合わせて、ステップ数を決めることにした。

1ドット当たりは、1024/64= 16(3/64= 0.047V相当)のステップ値になる。

<今回のトリガ値の直接入力仕様>

① 初期値=512(センター:1.5V相当)、1STEP ±16(約47mV相当)

センター:512を中心に、±側は、31テップ、-側は32ステップになる。(計64ステップ)

32ステップ目は、+側は、フルスケール値:1023をオーバー(1024)するので、1008(2.95V相当)とし

-側は、0なので、そのまま0とする。

-側は、33ステップ目に、フルスケール値:0をオーバー(-16)するので、0とする。

② トリガ設定レベルが視覚的に判るように、液晶画面、右端に、バー(マーカー)表示する。

③ 最初やったトリガ値表示記述は、デバッグ用として残す。(コメントアウトしておく)

・この修正で上手く行く!!

結果は良好である。

① 64テップ(0~ 1008)を可変するのに、そんなに時間が掛らない。(300回まとめ読みの効果)

② 数値飛び(マーカーの移動)も殆ど問題ない範囲に落ち着いた。

300回まとめ読みと言っても、波形描画更新間隔の、0.3秒の間でしか読んでないので、

REを回した時の、バー(マーカー)表示の反応が心配だったが、それほどでもなかった。

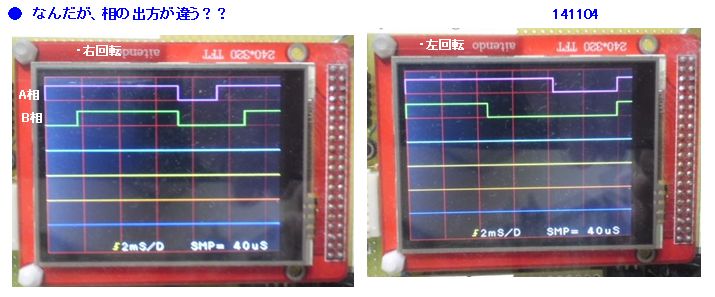

■ 2014.11.6

・これで、ロータリエンコーダーで、トリガ調整を行っても、ほぼアナログVRと同じ感覚で調整を

行うことが出来ることを確認できた。

今日はいくつかの画面サンプル取りを行った。

実験風景と、画面サンプルのついては、このページトップの写真を参照してください。

<最終回路図>

・こちらから、どうぞ→ 「PIC32MX_モノクロ単CHオシロ_REトリガ実験」

<最終ソース>

・こちらから、どうぞ→ Scope_PIC32MX_RE_TRG_TEST.c

← 実験テーマ1に戻る TOP PAGEに戻る 実験テーマ62へ →