● 実験テーマ3

「dsPIC30F_SDカード_リード・ライトTEST」の顛末記

■ 2010.08.01

<このTESTの目的>

・実験テーマ2の、ロガーは保存ターゲットがEEPROMであったが、これを最終的にはSDカードにしたい。

SDカードのアクセスには、マイクロ・チップ社から無償で提供されている、「FAT16ファイルシステム」を

移植して使う予定である。

そこで、現在のCPU:dsPIC2012でメモリ容量的に足りているのか?

足りていないのなら、どんなCPUを選択すればよいのかを含めて、検討し実際そのCPUで基板を製作

し、まずは基本的動作チェックとして「SDカードのリード・ライトTEST」を行うのが目的である。

尚、チェックプログラムは、PICの大御所「後閑哲也氏」と親交のある、齋藤洋一氏の「YS電子工作ラボ」

にちょうど良いのが掲載されていたので、自分のハードに合わせカスタマイズして使わせていただきました。

<SD(FAT16)を実装できるか?>

・現状のdsPIC2012(プログラムメモリ:12kB)では、ざっくり考えてもメモリ不足で、FAT16を実装できない。

しかも、このCPUを搭載しているトレーニングボードには、ブートローダーが出荷時に組み込まれており、

上メモリの内、1.5KBをブートローダが占有している。

・新たにCPUボード(CPUは、PIC24FJ32GA002(32kB)かdsPIC30F4013(48kB))を製作するか?

■ 2010.08.05

・dsPIC30F2012のまま、ソースをコンパイルしてみたところ、"FSIO.C"+"sd_r_w_cheak.c"+"SD-SPI.C"

をコンパイルしたところでリンク中、プログラム領域フルエラー発生を確認した。

→ やはりCPUは、PIC24FJ32GA002(32kB)かdsPIC30F4013(48kB)にするしかないか?

■ 2010.08.06

・dsPIC30F4013にしても、2012時のソースそのままで、デバイスヘッダーファイルをp30F4013.hに変更して

使用デバイスを4013指定でコンパイルすればメモリ不足なくリンクできつかと思いやってみたら上手くいった。

→ ちなみに、この時のプログラムメモリサイズは、約30kB(60%使用)だった。

よって、48kBの、4013を使用することに決める。

■ 2010.08.07

・現在使用している、dsPICトレーニングボードのハードを、そのまま活かし何とか4013を実装できないかと考えて

検討してみた。

dsPICトレーニングボードは、2012(チップ自体は、28pinSOIC)搭載の基板(40pinDIPサイズ)を本体基板に

40pinICソケットを介して実装されている。

それとピンコンパチでない、40pinDIPの4013を、そのソケットに実装するためには、ピン変換用のインターポーザ

基板を製作すれば何とかなるんではと思いついた。

・そこで下図に示すインタポーザ基板を製作してみた。

■ 2010.08.13

・インタポーザ基板と、SDカード追加基板が出来たので、それをトレーニングボードに実装し

デバッグを開始した。

・チェックプログラムの内容は、次のような単純なもの

→ SDカードに、整数12345を書込み、読み出した結果を、LCDに表示して両者等しいか確認する。

・dsPIC30F2012の時の実績ある、LCDアクセスプログラムで、4013動かず。

・DISP_CLEAR命令でLCDクリアせず?

・RD0でのLEDアクセスは正常

・LCDポート変更はハード、ソフト共OK(目視レベル)

・dsPIC30F4013の内蔵RC発振器の周波数が、2012と異なるのでは?と調べたが、

→ 7.37MHzで同じなので、LCDタイミングを制御している遅延関数に影響は無し。

(LEDを1秒間隔でフリッカーさせてみたが、ほぼ1秒間隔になっていたので時間の問題はなさそう。)

・WindowsMeでプログラムの書込みをしているのが問題なのかと思い、XPで書込みをしたが同じ。

・LCD制御ポート(D4~D7,

E, RS)を単純にソフトでON-OFFさせ、LCDモジュール側の端子にてオシロでチェック

→ ハード的には問題なし、ソフトの問題と思われる。

■ 2010.08.14

・4013を使用したLCDアクセスのWEB例と同じ、遅延タイミングにしても同じ。

→ DataセットからE立上がりまでのウエイト:0→ 1uS

Eパルス幅:610nS→ 1uS

・また、LCD初期化各ステージ間のウエイト値を、WEB例と同じにしても同じ。

(最初の、2ライン設定で、1ラインのままになる。)

■ 2010.08.15

・LCD制御ポートのみの、チェックプロを作成しテストを実施

<結果>

・ポートのビット単位アクセスを並べると、最後にアクセスしたD4のみパタパタ変化し、その前にアクセスした、

D5~D7は、Lowレベル固定で変化しなくなる。

(単独でポートをアクセスした場合は正常で、この現象は、2012では起こらない。何故かは不明?)

・後閑氏の著書を参考に、4bitパラレルデータを一斉にセットする記述に変更したら一応問題は解決した。

また、遅延の値も後閑氏のに合わせ変更した。

それと、RSはレベル制御でよさそうなので変更した。

■ 2010.08.16

・LCDポートのみのアクセスならば、4bitパラレルデータを一斉にセットする記述で問題ないが、同じRBポート

グループの他の入出力ビットをアクセスすると、LCDデータビットにも影響するようで、液晶表示がおかしく

なったり、SDの、CS制御がおかしくなったりする。

・WEBの4013使用の齋藤氏の例のように、後閑氏のアクセス方法を個別アクセスで動作させる方法に変えよう

と思う。

・RBポートの内、LCD_DATAの4bitのみLAT指定で個別アクセスでLCD表示はするが、RB2に割付けたSD_CS

出力と、RB4に割付けたSD_CD入力のPORT指定の動作がおかしくなる。

→ 同グループ内の、LAT/PORT指定混在は不可なのか?

・dsPICの場合、LAT指定出力もPORT指定出力も、そのポートの読出しの場合は、出力ラッチへセットした値

の読出しになるので、もう1度、RBポート各ビット全てをPORT指定にし、LCDパラレルデータ4ビットのみ一斉

にセットする記述に変更してみる。

■ 2010.08.18

・RBポートに割付けた、SD_CD入力と、WE入力が読めなかったのは、4013のRBポート13bit全てがReset時

AD入力(アナログ入力)に割付けられていた為と判明した。

→ Mainの頭に、RBポートをデジタル入力に設定するマクロを追加した。

ADPCFG= 0xFFFF;

・LCDアクセスに関しては、ビット単位アクセスの場合は、DATAポートのみLAT指定にしないと正しく表示

しないことが判明した。

または、全てPORT指定で、DATAのみ、4bitパラレルアクセスでもOKだが、今回はソースの解り易さから、

前者を採用した。(何故、DATAポートのみLAT指定にしないとNGかは不明?)

・またSDアクセス関数を実行すると表示がおかしくなっていたのは、SD-SPI.hのポート割付修正時、誤って

SD_CD入力を、RB10(LCD-D5)に割付ていたことが原因と判明した。

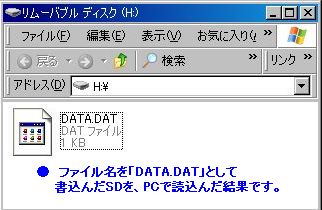

・以上3点を修正したら、SDカード_リード・ライトTESTプログラム(sd_r_w_check.c)が、上手く動いた。

(SDカードに、整数12345を書込み、読み出した結果を、LCDに正しく表示できた。)

■ 2010.08.19

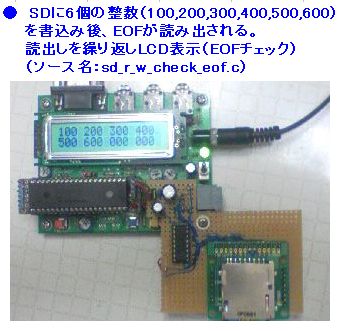

・SDカードTESTプログラムに以下の2つを追加(齋藤洋一氏のプログラムを参考にさせていただきました。)

① SDに順番に100,200,300,400を書込み、それを読出し後、LCD表示(FIFOチェック)

→ ソース名:sd_r_w_fifo.c

② SDに6個の整数(100,200,300,400,500,600)を書込み後、EOF(N_Read=

0)が読み出される。

読出しを繰返し、LCDに表示(EOFチェック)

→ ソース名:sd_r_w_eof.c

・上記の2つのTESTプログラムも上手く動いた。

■ 2010.08.20

・以下に、今までのTEST結果を示しました。

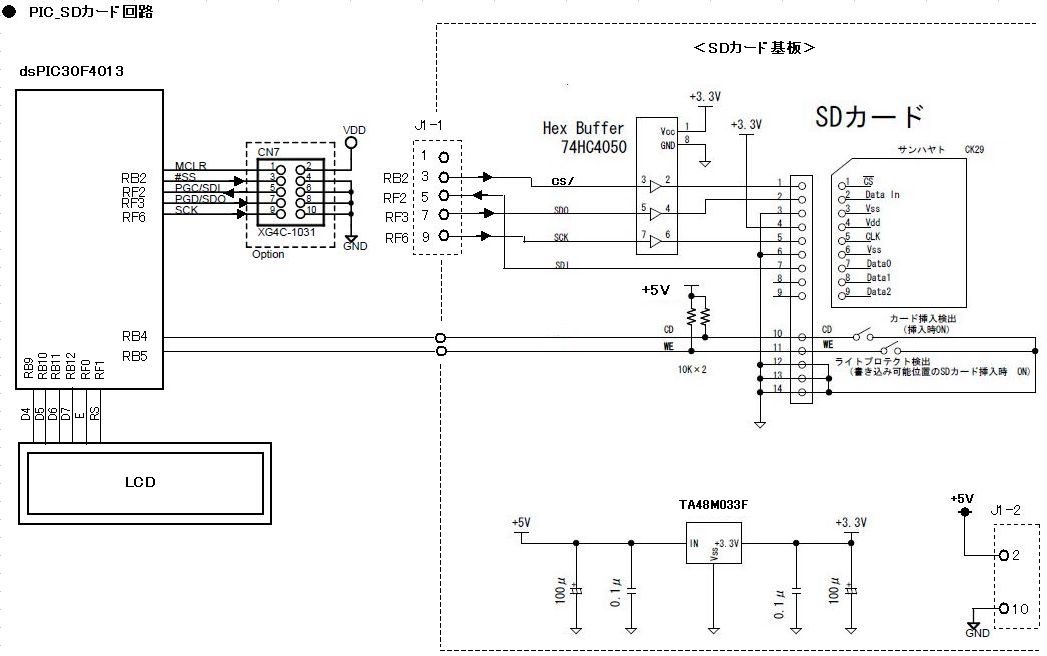

<最終回路図>

・ この時点では、回路図CADを持ち合わせてなかったので、画像の貼り合わせと、オートシェープで作成してました。

尚、dsPIC(トレーニングボード)側の回路は、主要な部品のみの接続を示しています。

<最終ソース・ファイル>

・こちらから、どうぞ→ sd_r_w_check.c

sd_r_w_check_fifo.c

sd_r_w_check_eof.c

← 実験テーマ1に戻る TOP PAGEに戻る 実験テーマ4へ →