● 実験テーマ29

● 実験テーマ29 ● 実験テーマ29

● 実験テーマ29

「PIC32MXによる、オシロ実験_1」(トリガ方式:ポテンショレベルをAD変換)

■ 2013.4.8

(1) 実験目的

① PIC24Hと、PIC32MXのシステムクロック速度の違い(40MIPSに対し80MIPS)

で測定帯域がどこまで伸びるか実験してみる。

PIC24Hの時と同じサンプリング+バッファ処理方式(2分割のダブルバッファ)

でやってみる。

目標としては、SPIラインの観測が出来るように、100kHzのクロックが

0.2ms/div(2uSサンプル)で、レベル低下なしに周期が確認できる程度に

表示できればと思っているのだが・・・・

まあ、100kHzの1サイクルは、10uSなので、2uSだと、1サイクル5データしか

サンプルできないのでサイン波は厳しいと思われるが。

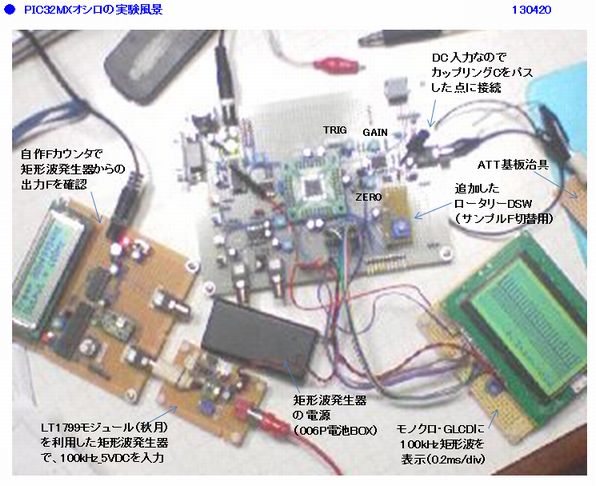

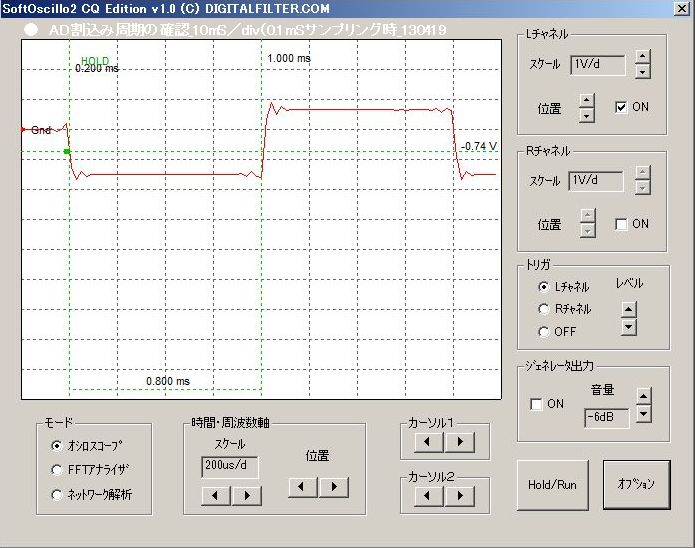

(2) 実験環境整備

① PIC32MXトレーニング基板使用。

ただ以下の改造が必要。

a. 入力アンプ回路に、2ndOPアンプのZERO(オフセット)ポテンショを追加

(センターレベル固定とポテンショ設定を選べるように、DICピンを立てる。)

b. AN1ピンに、トリガポテンショを追加

(これを切り離せる、DICピンも用意)

c.

時間軸レンジ(サンプル周期)切替ロータリーDSW治具を追加

(プルアップは、MPU内蔵プルアップを使用)

■ 2013.4.10

・とりあえず、PIC24Hの、AD設定条件そのままで、PIC32MXへ移植してみることにする。

・PIC24HJ12GP202と、PIC32MXの、ADCブロックは、ほぼ同じようである。

またDMAを使わないで済みそうである。

BUFとして最初から、ADBUF0~Fの16個のバッファが用意されている。

■ 2013.4.11~ 2013.4.12

・ここまで、PIC24Hと、PIC32MXのAD設定関係のレジスタ類を比較検討[済]

・この他、PIC24Hと異なるのは、たぶんADC割込み関数の記述だと思う。

■ 2013.4.15

・一応ソース書き上げる。

・コンパイルエラー処理を行う。

→ CNENレジスタの構成が、PIC24Hと異なっていた。

32bitあって、またマクロ名が異なる。

→ CNPU1は、NGで、CNPUEレジスタの、32bitしかない。

記述については、下位16bitしか使わないので、16bit表記でOK

→ これでコンパイルは通った。

■ 2013.4.17

・PIC32MXトレーニング基板の改造が済んだので、今日は、100kHzサイン入力で前作の

PIC24Hオシロの表示がどうなるか、まずリファレンス作りのため測定しようと思う。

→ 自作FGの出力範囲= 10Hz~約10kHzまでが実用域(歪と、レベル低下を無視すれば、

~50kHz位まで)なので、100kHzサイン波は入力できない。(他にFGの持ち合わせ無)

→ そこで、秋月のLTC1799モジュールを利用して自作した、矩形波発生器(10k~30M)

を使うことにした。

→ これを使っての、PIC24Hオシロでの結果は以下の通り。

① 100kHzでは、波形にならずレベルも極端に低下。

② 30kHz位が実用限界

■ 2013.4.18

・PIC32MXでのデバッグ開始

・とりあえず、PIC32MXで基本のオシロ動作をするか、おおざっぱに確認することにした。

→ まず、イニシャルメッセージの、"Start

Oscillo"は表示OK

その後、XY軸が表示されない。

たぶん、AD割込みに入ってこないと思われる。

① まず、EOC待ちの手前までは、RUNしていることを、デバッグ用LEDにて確認

② AD割込みルーチンの頭で、デバッグ用LEDを点灯させ、プログラムを停止してみたが

点灯しない。やはり、AD割込みにジャンプしてこないようだ。

・この想定原因としては、INT許可までの手順の誤りが考えられる。

後閑氏の「PIC32MX活用ガイドブック」の手順(⑧~⑨)を、AD_ONの前に入れてみる。

⑧ AD1IFビットを一旦クリアして割込み要因をリセット

→ mAD1ClearIntFlag();

⑨ AD1IP<2:0>と、AD1IS<1:0>でプライオリティレベルを設定

→ mAD1SetIntPriority(7);

mAD1SetIntSubPriority(3);

→ これらを追記してみたが、未だダメ

→ こうなったら後は、ベクター割込み許可の記述が適当でないのかもしれない・・・・

ベクターは、AD割込みしか使ってないと理解しているので、シングルベクター割込み許可の

記述にしてあるのだが、マルチベクター割込み許可に記述を変更してみたら、AD割込みが

入るようになった。(AD以外はタイマーも使っているが、PSとPRの設定だけで、割込みは

使ってないので、シングルベクターでもよいはずと思っていたんだが・・・ まあ結果良しとしよう。)

・次に、1kHzサイン波を入力してみた。(1ms/divレンジ、0.3Vp-p入力)

→ ZERO及び、TRIGポテンショは効いているが、周期が正しく出ていない?

(若干速めに表示されてしまう)

→ たぶんT3のPR設定ミスだろうと思い、調査を始めた。

■ 2013.4.19

・T3周期(サンプル周期)が合わない件の調査

<調査事項>

① そもそも自作FGの出力周波数は正しいか?

→ Fカウンタにて正しいことを確認した。

② それでは、PIC32MXトレーニング基板上の、入力アンプの出力Fはどうか?

→ これも、Fカウンタにて正しいことを確認した。

③ AD割込み周期を測定すれば、T3周期が合っているか確認できるので、

AD割込み関数の頭に、ポートをトグルする記述を追加してチェックしてみた。

→ 最初、Fカウンタで測定したのだが、割込み処理が終わった後、メインの描画処理があるので、

ON/OFFサイクルの規則正しい繰返しにならず、正しく測定できなかったので、

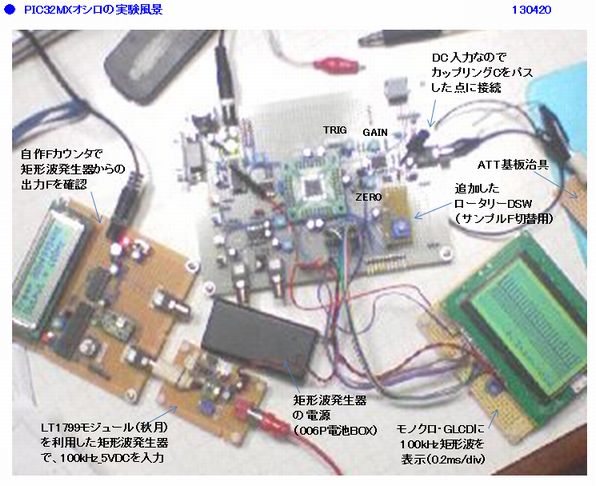

(まあ、よく考えれば最初から解ってることなのだが・・・)ソフトオシロ2にて確認することにした。

→ 1ms/div(10uSサンプル)時、AD割込み周期は、80uSになっていることが確認できた。

ソフトオシロ2の、オーバーサンプル機能を使って、50uSレンジで見ているので、確かさは保障できない

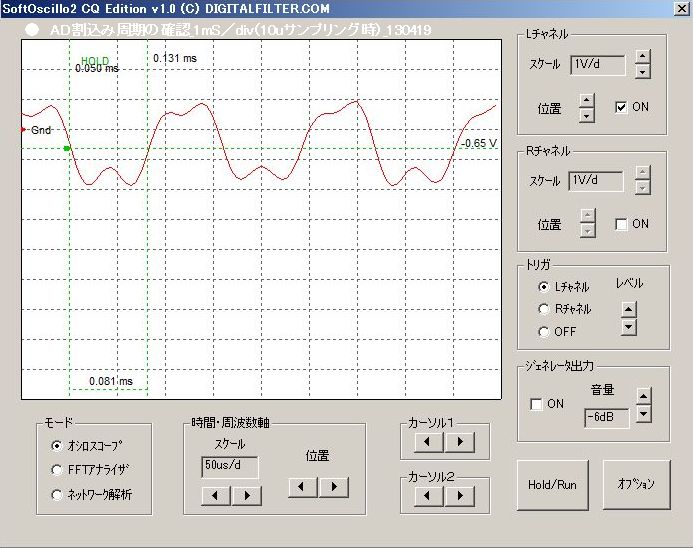

ので、念のため、10ms/div(0.1msサンプル)でも測定してみたら、0.8mSになっていることが確認

できた。(2CH分(信号入力と、トリガ入力)を、各4回ずつサンプルするので、10uSサンプル時の

AD割込み周期は、10uS*4*2=80uSで正しい。)

以下に、その時の測定波形を示す。

・T3割込みルーチンだけ、デバッグ用に作り、そこでトグル・フリーランさせて、Fカウンタで見れば確実なので

別プロジェクトで、T3の設定周期(サンプル周期)精度を、Fカウンタにて確認してみる。

(まあ、ソフトオシロ2の結果で殆ど問題ないのだが、精度までは判らないので・・やってみることに)

→ 10uSサンプルで、ポートをトグルさせると、周期は2倍の20uSになるので、周波数は50kHzになる

はずである。

その測定結果は、自作の周波数カウンタで、49.961Hz(20.0156uS)であった。

つまり、サンプル周期は、20.0156/2=

10.0078uSで、0.0078uS(7.8nS)の誤差しか出てないことが判った。

・どうも検証の結果

T3サンプル周期の設定に間違いはなく正確に出ているようなので

AD割込み周期も正しいようである。

ならば、時間軸の描画位置(固定)と、取得プロットデータ数による波形描画との関係に誤りがあるのか??

・疑いたくないが、(意図的かもしれないので)後閑氏のPIC24Hのクロック設定の疑問が今でもある。

PIC24Hのデータシートの説明通りに、後閑氏の設定はなっていないことが、前回の実験でも分かって

いることから、このことで、描画との辻褄が合っているのかもしれない・・・・

→ ここで、PIC24Hオシロでも、T3周期の確認を行ってみることにした。

・ここで仮説を立てる。

後閑氏の画面座標(時間軸)の、Xポジションの値:53及び、106は意図的かもしれないが、誤りと思われる。

X= 50及び、X= 100が正しいと考える。

(PIC24Hオシロで、うまく行っているのは、クロック設定が誤っていて、T3周期がズレそれで波形描画との

辻褄が合っているのだと思われる。

(または、オーバークロックにして意図的に、Xポジションを、ずらしているのかもしれないが・・・)

<その理由>

※ 条件として、1ms/div(10uSサンプル)で考えると

① 1mS= 1000uS/1サイクル

AD割込み周期= 80uS

なので、1000u/80u= 12.5回、AD割込みが入って、波形1サイクル分のデータが揃うことになる。

② 8回のサンプル+AD変換が完了すると、1回のAD割込みが入るように設定されているが

その内の4回が、入力信号(AN0)についてのサンプル+変換(残り4回はトリガ入力いついての

サンプル+変換)であるので、1回のAD割込みで得られる、AN0についてのデータは、

4データである。

③ よって、1サイクルを描画するのに必要なデータ数は、

4データ × 12.5回= 50データ

になる。

このことから、必然的に、最初の1サイクルのX座標位置は、X=

50になると考える。

(実際に、50データ分が、AD割込みで取得されるのは、13回目のAD割込みが入った時になる)

■ 2013.4.20

・昨日の理由で、PIC32MXオシロの、時間軸の、X座標を、

X= 53→ X= 50

Y= 106→ Y= 100

に変更したら、波形周期と、時間軸がぴったり合うようになった。

・昨日やろうと思っていた、前作の、PIC24Hオシロについても、T3割込みだけのプロジェクトを、

PIC32MX同様に作成し、サンプル周期が、どの程度ズレているか確認してみることにした。

→ 結果は、Fカウンタによる実測で、52.5kHzであった。

つまり周期にすると、1/52.5kHz= 19.048uS

よって、T3周期(サンプル周期)としては、19.048uS/2=

9.524uS

だから、PIC32MXオシロでは、スケール上の波形周期が速く見えていたことになる。

→ さらにこの結果から、Fcyを逆算すると、(PIC24Hの場合本来は、40MHzになるはずだが・・・)

T3分周器の設定値:n=400なので、システムクロックサイクル:Tcyは以下で求まる。

Tcy × 400= 9.524u

∴ Tcy= 9.524uS/400=

0.02381uS= 23.81nS(本来は、25nS)

よって Fcy= 1/23.81nS= 41.999MHz

→ この結果から、後閑氏のクロック設定値は、意図的にオーバークロック(40M→42M)にして、サンプル周期を

設定より若干速めにし、その分時間軸のX座標をズラして動かしていると考えられる。

<補足>

※ PIC24Hのクロック設定(PLLDIVの設定)について

・PLLDIV<8:0>に設定した値そのものが、逓倍値ではなく、設定値+2が設定値になるので、

現在40としているのを、38(PLLFBbits.PLLDIV= 38;)にすれば、Fcy

40MHzになる。

ちなみにこれでやると、T3割込みを使った、ポートトグル実験での、実測値は、50.002kHzになるので

間違いない。

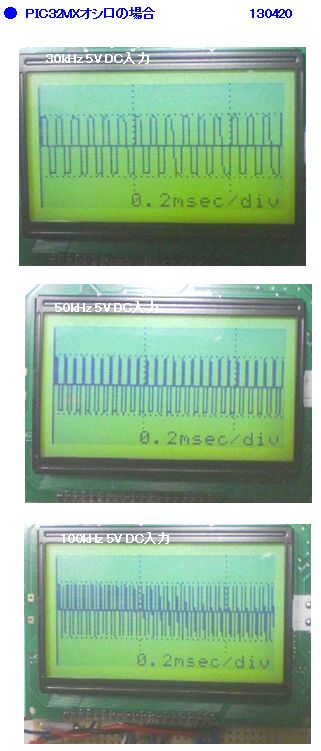

・ここで、PIC32MXオシロでの波形取りをして、PIC24Hオシロと比較してみた。

以下の通りで、実用的には変わらず、30kHz位だが、PIC32MXの方が、50KHzも含めてレベルは落ちてないし

波形としてもややはっきり表示できている。

また、100kHzもレベル落ちしていない。(ただこれじゃ100kHzはとても実用にならない。)

この差は、Fcyの差というより、ADCの若干のスピードアップによるものが大きいと思われる。

■ 2013.4.21

・これで、殆どPIC32MXへの移植実験は清んだが、思ったような高速化の成果は得られなかった。

・やはり少なくとも、0.2mS/div(2uSサンプル)レンジで、100kHzを矩形波入力でよいから、見れる

形の波形表示にしたい。

※ 一つの案が前からあって、

トリガを、現在のポテンショレベルをサンプル+AD変換する方式から、2つの、TRG_UP、TRG_DWN

SWで、直接デジタル値を設定する方式に変更すれば、AN0のみの連続サンプル+AD変換が可能

なので比較的きれいな波形になると考えている。

→ このテーマは、次回の「実験テーマ30」として、展開したいと思います。

<最終回路図及び、ソース>

・回路図は、こちらからどうぞ→ PIC32MX_オシロ実験回路図

・Cソースは、こちらからどうぞ→

Scope_PIC32MX.c

← 実験テーマ1に戻る TOP

PAGEに戻る 実験テーマ30へ →