�@�@�@�V���v����CPU������Ă݂悤�@�i���̂Q�j

�@�@�@�@�@�@�@�@

�|�u�g�c�k��p�����S�̐v�|

�M�B��w�H�w���@�@���V�T�i

�P�D�͂��߂�

��1�́i���̂P�j �ł́C�I���W�i���� 15bit RISC�^�v���Z�b�T�̖��߃Z�b�g�����肵�C

C���� ��p���� ���� �uCPU�V�~�����[�^�v �𐧍삵�܂����D

�{�͂���C �n�[�h�E�F�A�L�q����iHardware Description Language) ��p���āC���ۂ�

�v���Z�b�T��v���܂��D

�v������H�̃f�[�^�́C FPGA(Field Programmable Gate Array) �Ƃ��������̃f�o�C�X��

�_�E�����[�h���āC���삳���܂��D

�n�[�h�E�F�A�L�q���� �ɂ́C���ۓI�ɍL�����y���Ă��� VHDL ���g�p���܂��D

���̃R���e���c�̒��ŁC VHDL�̋L�q�@ ���ڍׂɐ������邱�Ƃ͂ł��܂���̂ŁC�Q�l����

�C���^�[�l�b�g���ŕ����C�g�����Ȃ���悤�K�n���ĉ������D

�Ȃ��C�{�͂ł͖��߃Z�b�g�̐v�Ɠ��l�C�\�L�̕�����₷����D�悳���Ă��邽�߁C

�������֘A �� �n�[�h�E�F�A�͑啝�� �ȗ��� ���Ă��܂��D

�Ⴆ�C �v���O����ROM�iPROM) �̓��e���C VHDL �̒��ŋL�q���Ă��܂��D

�܂��C���� RAM�̗e�� ���������ݒ肵�Ă���̂ŁC D-FF ��p���ċL�q���Ă��܂��D

���̂悤�ȕ��@�͕K�����������I�Ȏ�@�ł͂���܂��C VHDL�̃}�N���t�@���N�V���� ��p���āC

�O���t�@�C�� ����PROM�̃f�[�^��ǂݍ��ގ�@��C �z�� ��p����RAM���L�q������@�ɂ��ẮC

��4�� �Ő������܂��D

�{�͂ł́C CPU�̊�{�I�ȓ��� �ɂ��Đ���������C �S�̂̐v ���s���܂��D

���̊K�w�Ɉʒu���� �ʂ̉�H�i�R���|�[�l���g�j �ɂ��ẮC���� ��3�� �ʼn�����܂��̂ŁC

�@�\��傫�������M���̎n���𒆐S�ɗ�������悤�ɂ��ĉ������D

����ł́C CPU�̍\�� ����������܂��傤�D

�Q.�@CPU�̍\��

�Q�D�P�@��{�I��CPU�̓���i�X�e�[�W�j

�͂��߂ɁC��{�I��CPU�̓���ɂ��ĕ��K���܂��D

���̐}�́CCPU�̓����͎��I�ɕ\�������̂ł��D

1���߂̓����4�̃X�e�[�W�C���Ȃ킿

(1) �t�F�b�` �F ���߃R�[�h��PROM����ǂݍ��� (2) �f�R�[�h �F �ǂݍ����߃R�[�h����͂��A���s�̏������s�� (3) ���s �F CPU�����̉��Z���j�b�g�iALU�j�Ŗ��߂����s���� (4) ���C�g�o�b�N �F ���s���ʂ����W�X�^�� RAM�ɏ������� ����\������Ă��܂��B

�e�X�e�[�W��1�N���b�N�Ŏ��s�����Ƃ��C1�̖��߂����s�����̂� 4�N���b�N ��v���܂��D

�Q�D�Q�@CPU�̊�{�\��

����v����CPU���C

�@�@ �t�F�b�`

�@�A �f�R�[�h

�@�B ���s

�@�C ���C�g�o�b�N

�� �S�X�e�[�W �ō\������܂��D

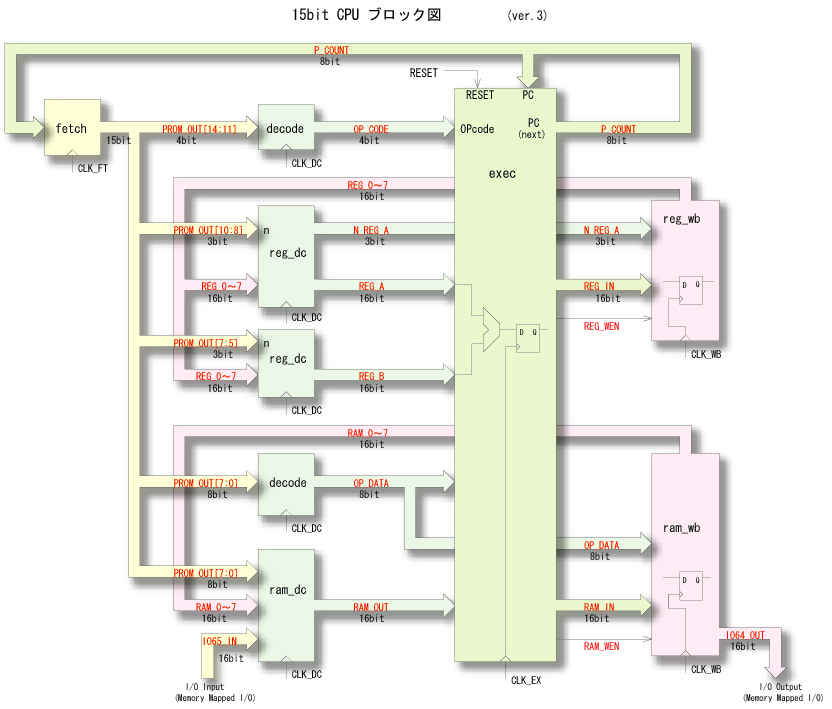

��P�� �Ŏ����� �u���b�N�\���} ���C������x�����܂��D

�}�̍��� �@�t�F�b�` �C�E�� �C���C�g�o�b�N �̃X�e�[�W�ɑΉ����܂��D

�X�e�[�W�̐��ڂɔ����C������E�Ɍ������āC�K�v�ȃf�[�^�ɕϊ�����n����Ă䂭�\���ƂȂ��Ă���

���Ƃ𗝉����ĉ������D

�Q�D�R�@��{�I��CPU�̃X�e�[�W

CPU�̏ڍׂȃu���b�N�\���ƁC�e���̋�̓I�ȐM�������ȉ��Ɏ����܂��D

�Q�D�S�@CPU�̃^�C���`���[�g

��Ŏ������M���̃^�C���`���[�g���C�ȉ��̐}�Ɏ����܂��D

�S�̃X�e�[�W�i �@�t�F�b�` �C �A�f�R�[�h �C �B���s �C �C���C�g�o�b�N �j�ŁC�K�v�ȐM������������C���̃X�e�[�W��

�n�����\���ƂȂ��Ă��܂��D

�Ⴆ�C�f�R�[�h�̃X�e�[�W�ł́C�O�i�̃t�F�b�`�̏o�͂ɑ��Ę_�����Z�i�g������H�j���s���C

���̌��ʂ����b�`�����M�����o�͂���܂��D

���̐M���́C���̎��s�X�e�[�W�̓��͂ƂȂ�܂��D

�R�D�@CPU�̑S�̐v

�R�D�P�@�u���b�N�����Ɗe�R���|�[�l���g�̐v

�{�߂���CVHDL��p����CPU�̋L�q��ɂ��ĉ�����܂��D

����CPU�́C�ȉ��Ɏ���5�̃u���b�N�ƁC9�̃R���|�[�l���g��H�ɂ��\������Ă��܂��D

�ȉ��C�ȒP�ɂ��̓��e��������܂��D

(1) �N���b�N�����p�u���b�N

���̃u���b�N�ł́C��{�N���b�N����ɁCCPU�̊e�u���b�N�ɋ�������S���̃N���b�N�����܂��D

���@�� ��{�N���b�N�@ CLK �o�@�� �@�t�F�b�`�C�A�f�R�[�h�C�B���s�C�C���C�g�o�b�N�̊e�u���b�N�ɋ�������4�̃N���b�N�M��

CLK_FT �CCLK_DC�C CLK_EX �CCLK_WB

�N���b�N ��{�N���b�N�@ CLK �����̃N���b�N�̓^�C���`���[�g�̐}�Ɏ����悤�ɁC�݂��ɏd�Ȃ邱�Ƃ��Ȃ�

4���\���ɂȂ��Ă��܂��D

�Ȃ��CVHDL�̃R���|�[�l���g���́@ clk_gen.vhd �@�ł��D

(2) �t�F�b�`�iFetch�j�u���b�N

�t�F�b�`�u���b�N�̓��o�͂́C�ȉ��̂悤�ɂȂ��Ă��܂��D

���@�� �v���O�����J�E���^�iPC�j�̏o�� P_COUNT (8bit) �o�@�� �J�E���^���A�h���X�Ƃ���Program ROM�̃f�[�^ PROM_OUT (15bit) �N���b�N ��P���̃t�F�b�`�N���b�N�@ CLK_FT ���Ȃ킿�C�v���O�����J�E���^�iPC�j����͂Ƃ���PROM�iProgram ROM�j�̃f�[�^�i15bit�j��

�t�F�b�`�̃^�C�~���O�iCLK_FT�j�Ń��b�`���C�o�͂��܂��D

VHDL�̃R���|�[�l���g���́@ fetch.vhd �@�ł��D

��ʂɁC�v���O�����iPROM�j�̃f�[�^�́CCPU�̉�H����Ɨ������C�ʃt�@�C���ŋL�q���܂��D

�������Ȃ���C���̗�͕�����Ղ���D�悳���邽�߁CVHDL�̒��ł����̃f�[�^���L�q���Ă��܂��D

��4�͂ł́C�O���t�@�C���̌`���Ńf�[�^��ǂݍ��ޕ��@�ɂ��ďЉ�܂��D

(3) �f�R�[�h(Decode)�u���b�N

�f�R�[�h�u���b�N�́C �@ decode.vhd�C�A reg_dc.vhd�C�B ram_dc.vhd ��3�̃R���|�[�l���g�ɕ�����

�L�q���Ă��܂��D

�@ decode.vhd �̓��o�͂́C�ȉ��̂悤�ɂȂ��Ă��܂��D

���@�� ���b�`���ꂽProgram ROM�̃f�[�^�o�� PROM_OUT �i15bit) �o�@�� �I�y�R�[�h OP_CODE (4bit)����уf�[�^�i�A�h���X�j�̃I�y�����h OP_DATA (8bit)

�N���b�N ��Q���̃f�R�[�h�N���b�N CLK_DC �A reg_dc.vhd �̓��o�͂́C�ȉ��̒ʂ�ł��D

���@�� Program ROM���������W�X�^A�CB�̔ԍ� N_REG_IN (3bit)

8�̃��W�X�^�̏o�� REG_0�`7 (16bit)�o�@�� ���W�X�^A�CB�̔ԍ� N_REG_OUT (3bit)

���W�X�^A�CB�̔ԍ��ɑΉ����郌�W�X�^�̃f�[�^ REG_OUT (16bit)�N���b�N ��Q���̃f�R�[�h�N���b�N CLK_DC �B ram_dc.vhd �̓��o�͂��C�ȉ��Ɏ����܂��D

���@�� Program ROM������RAM�̃A�h���X RAM_ADDR (8bit)

8��RAM�o�� RAM_0�`7 (16bit)

�������}�b�v�hI/O�̓��̓f�[�^ IO65_IN (16bit)�o�@�� �A�h���X�Ŏw�肳�ꂽ RAM�̃f�[�^ RAM_OUT (16bit) �N���b�N ��Q���̃f�R�[�h�N���b�N CLK_DC

(4) ���s(Execute)�u���b�N

���s�u���b�N�� VHDL�R���|�[�l���g�́@ exec.vhd �@�ł���C

���̓��o�͈͂ȉ��̂悤�ɂȂ��Ă��܂��D

���@�� �V�X�e�����Z�b�g���� RESET

�v���O�����J�E���^(PC) PC_IN (8bit)

�I�y�R�[�h OP_CODE (4bit)����уf�[�^�i�A�h���X�j�̃I�y�����h OP_DATA (8bit)

���W�X�^�w��I�y�����h(3bit)�ɑΉ����郌�W�X�^�̃f�[�^ REG_A (16bit)�C REG_B (16bit)

�A�h���X �I�y�����h(8bit)�ɑΉ�����RAM�̃f�[�^ RAM_OUT (16bit)

�o�@�� �v���O�����J�E���^�iPC) PC_OUT (8bit)

���W�X�^�̉��Z���� REG_IN (16bit)

���W�X�^�ւ̏��������M�� REG_WEN

�A�h���X �I�y�����h(8bit)�ɑΉ�����RAM�̃f�[�^ RAM_IN (16bit)

RAM�ւ̏��������M�� RAM_WEN�N���b�N ��R���̎��s�N���b�N CLK_EX

(5) ���C�g�o�b�N(WriteBack)�u���b�N

���C�g�o�b�N�u���b�N�́C�Q��VHDL�R���|�[�l���g�i �@ reg_wb.vhd �C �A ram_wb.vhd �j�ɕ����ċL�q����Ă��܂��D

�@ reg_wb.vhd �̓��o�͂��C�ȉ��Ɏ����܂��D

���@�� ���W�X�^�I�y�����h(3bit)�Ŏw�肵�����W�X�^�̔ԍ� N_REG (3bit)

���W�X�^�̉��Z���� REG_IN (16bit)

���W�X�^�ւ̏��������M�� REG_WEN

�o�@�� 8�̃��W�X�^�̃f�[�^ REG_0�`7 (16bit)

�N���b�N ��S���̃��C�g�o�b�N�N���b�N CLK_WB �A ram_wb.vhd �̓��o�͂́C�ȉ��̂悤�ɂȂ��Ă��܂��D

�Ȃ��C���̗�ł�RAM�̃f�[�^ RAM_0�`7 ���ʂɋL�q���Ă��܂��D

RAM��z��ŕ\���C���̃A�h���X��z��̃C���f�b�N�X�ɑΉ���������@�ɂ��ẮC��4�͂ŏЉ�܂��D

���@�� �A�h���X�I�y�����h(8bit)�Ŏw�肵��RAM�A�h���X RAM_ADDR (8bit)

�I�����ꂽ���W�X�^�̃f�[�^ RAM_IN (16bit)

RAM�ւ̏��������M�� RAM_WEN

�o�@�� RAM�̃f�[�^ RAM_0�`7 (16bit)�@�i8��ށj

�������}�b�v�hI/O�̏o�̓f�[�^ IO64_OUT (16bit)

�N���b�N ��S���̃��C�g�o�b�N�N���b�N CLK_WB

�R�D�Q�@�e�R���|�[�l���g�̃^�C�~���O�v

�\�t�g�E�F�A�Z�p�҂ɂƂ��āC�n�[�h�E�F�A�̐v�ōł�����Ɗ�����̂��C�^�C�~���O�̖��ł��D

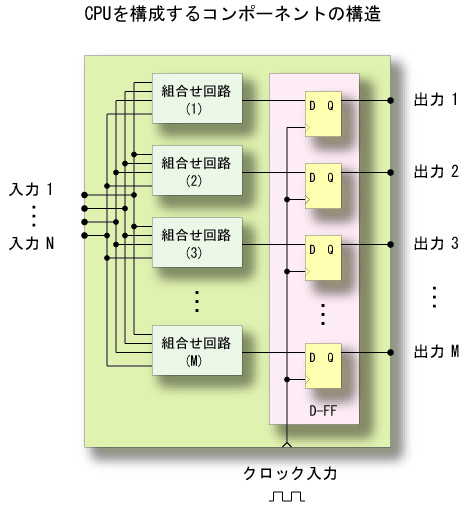

�����Őv���邷�ׂẴR���|�[�l���g�͂��ׂāC���̐}�悤�ȒP���ȍ\���ɂȂ��Ă��܂��D

���Ȃ킿�C���͐M����g������H�̓��͂Ƃ��C���̏o�͂��N���b�N�Ń��b�`���ďo�͂��܂��D

���b�`�ɂ��x���́C���1�N���b�N�ƂȂ�_�ɒ��ӂ��ĉ������D

�^�C���`���[�g�Ŏ������悤�ɁC�e�X�e�[�W�́C���̍Ō�ɗ����オ��N���b�N

�Ń��b�`����o�͂���܂��D

�����łP���₪����܂��D

�{���CEXEC�u���b�N�̃v���O�����J�E���^�iPC�j�o�͂́C���C�g�o�b�N�̃^�C�~���O�ŁC���b�`�����

���ƂɂȂ��Ă��܂����C�M�����̃u���b�N�}�ł́C���̉�H���ȗ�����Ă��܂��D

���̂悤�ȏȗ��ɂ��C��肪�������邱�Ƃ͂Ȃ��̂ł��傤���H�@�l���ĉ������D

�i�q���g�F�@�S���̃N���b�N��p���Ă���_�ɒ��Ӂj

�S.�@CPU��VHDL�ɂ��L�q��

�{�߂ł́C����CPU��VHDL�ɂ��L�q������icpu15e.vhd�j�������܂��D

�e�R���|�[�l���g�̏ڍׂɂ��ẮC���́i���̂R�j�Ő������܂��̂ŁC

�����ł͂����̋@�\�𒆐S�ɔc�����ĉ������D

�S�D�P�@VHDL��p����CPU�̃\�[�X�R�[�h�icpu15e.vhd�j

-- exec.vhd

-- Y.Izawa

-- H18.3.27

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.std_logic_unsigned.all;

entity cpu15e is

port

(CLK : in std_logic; RESET : in std_logic; IO65_IN : in std_logic_vector (15 downto 0); IO64_OUT : out std_logic_vector (15 downto 0) ); end cpu15e;

architecture RTL of cpu15e is

component �@ clk_gen port

(CLK : in std_logic; CLK_FT : out std_logic; CLK_DC : out std_logic ; CLK_EX : out std_logic; CLK_WB : out std_logic ); end component;

component �@ fetch port

(CLK_FT : in std_logic; P_COUNT : in std_logic_vector (7 downto 0); PROM_OUT : out std_logic_vector (14 downto 0) ); end component;

component �@ decode port

(CLK_DC : in std_logic; PROM_OUT : in std_logic_vector (14 downto 0); OP_CODE : out std_logic_vector (3 downto 0); OP_DATA : out std_logic_vector (7 downto 0) ); end component;

component �@ reg_dc port

(CLK_DC : in std_logic; REG_0 : in std_logic_vector (15 downto 0); REG_1 : in std_logic_vector (15 downto 0); REG_2 : in std_logic_vector (15 downto 0); REG_3 : in std_logic_vector (15 downto 0); REG_4 : in std_logic_vector (15 downto 0); REG_5 : in std_logic_vector (15 downto 0); REG_6 : in std_logic_vector (15 downto 0); REG_7 : in std_logic_vector (15 downto 0); N_REG_IN : in std_logic_vector (2 downto 0); N_REG_OUT : out std_logic_vector (2 downto 0); REG_OUT : out std_logic_vector (15 downto 0) ); end component;

component �@ ram_dc port

(CLK_DC : in std_logic; RAM_0 : in std_logic_vector (15 downto 0); RAM_1 : in std_logic_vector (15 downto 0); RAM_2 : in std_logic_vector (15 downto 0); RAM_3 : in std_logic_vector (15 downto 0); RAM_4 : in std_logic_vector (15 downto 0); RAM_5 : in std_logic_vector (15 downto 0); RAM_6 : in std_logic_vector (15 downto 0); RAM_7 : in std_logic_vector (15 downto 0); IO65_IN : in std_logic_vector (15 downto 0); RAM_ADDR : in std_logic_vector (7 downto 0); RAM_OUT : out std_logic_vector (15 downto 0) ); end component;

component �@ exec port

(CLK_EX : in std_logic; RESET : in std_logic ; OP_CODE : in std_logic_vector (3 downto 0); PC_IN : in std_logic_vector (7 downto 0); REG_A : in std_logic_vector (15 downto 0); REG_B : in std_logic_vector (15 downto 0); OP_DATA : in std_logic_vector (7 downto 0); RAM_OUT : in std_logic_vector (15 downto 0); PC_OUT : out std_logic_vector (7 downto 0); REG_IN : out std_logic_vector (15 downto 0); RAM_IN : out std_logic_vector (15 downto 0); REG_WEN : out std_logic ; RAM_WEN : out std_logic ); end component;

component �@ reg_wb port

(CLK_WB : in std_logic ; N_REG : in std_logic_vector (2 downto 0); REG_IN : in std_logic_vector (15 downto 0); REG_WEN : in std_logic ; REG_0WB : out std_logic_vector (15 downto 0); REG_1WB : out std_logic_vector (15 downto 0); REG_2WB : out std_logic_vector (15 downto 0); REG_3WB : out std_logic_vector (15 downto 0); REG_4WB : out std_logic_vector (15 downto 0); REG_5WB : out std_logic_vector (15 downto 0); REG_6WB : out std_logic_vector (15 downto 0); REG_7WB : out std_logic_vector (15 downto 0) ); end component

component �@ ram_wb port

(CLK_WB : in std_logic; RAM_ADDR : in std_logic_vector (7 downto 0); RAM_IN : in std_logic_vector (15 downto 0); RAM_WEN : in std_logic; RAM_0 : out std_logic_vector (15 downto 0); RAM_1 : out std_logic_vector (15 downto 0); RAM_2 : out std_logic_vector (15 downto 0); RAM_3 : out std_logic_vector (15 downto 0); RAM_4 : out std_logic_vector (15 downto 0); RAM_5 : out std_logic_vector (15 downto 0); RAM_6 : out std_logic_vector (15 downto 0); RAM_7 : out std_logic_vector (15 downto 0); IO64_OUT : out std_logic_vector (15 downto 0) ); end component;

signal CLK_FT : std_logic; signal CLK_DC : std_logic; signal CLK_EX : std_logic; signal CLK_WB : std_logic; signal P_COUNT : std_logic_vector (7 downto 0); signal PROM_OUT : std_logic_vector (14 downto 0); signal OP_CODE : std_logic_vector (3 downto 0); signal OP_DATA : std_logic_vector (7 downto 0); signal N_REG_A : std_logic_vector (2 downto 0); signal N_REG_B : std_logic_vector (2 downto 0); signal REG_IN : std_logic_vector (15 downto 0); signal REG_A : std_logic_vector (15 downto 0); signal REG_B : std_logic_vector (15 downto 0); signal REG_WEN : std_logic; signal REG_0 : std_logic_vector (15 downto 0); signal REG_1 : std_logic_vector (15 downto 0); signal REG_2 : std_logic_vector (15 downto 0); signal REG_3 : std_logic_vector (15 downto 0); signal REG_4 : std_logic_vector (15 downto 0); signal REG_5 : std_logic_vector (15 downto 0); signal REG_6 : std_logic_vector (15 downto 0); signal REG_7 : std_logic_vector (15 downto 0); signal RAM_IN : std_logic_vector (15 downto 0); signal RAM_OUT : std_logic_vector (15 downto 0); signal RAM_WEN : std_logic ; signal RAM_0 : std_logic_vector (15 downto 0); signal RAM_1 : std_logic_vector (15 downto 0); signal RAM_2 : std_logic_vector (15 downto 0); signal RAM_3 : std_logic_vector (15 downto 0); signal RAM_4 : std_logic_vector (15 downto 0); signal RAM_5 : std_logic_vector (15 downto 0); signal RAM_6 : std_logic_vector (15 downto 0); signal RAM_7 : std_logic_vector (15 downto 0);

begin C1 : clk_gen port map (CLK, CLK_FT, CLK_DC, CLK_EX, CLK_WB); C2 : fetch port map (CLK_FT, P_COUNT, PROM_OUT); C3 : decode port map (CLK_DC, PROM_OUT, OP_CODE, OP_DATA ); C4 : reg_dc port map (CLK_DC, REG_0, REG_1, REG_2, REG_3, �@�@�@�@�@REG_4, REG_5, REG_6, REG_7, �@�@�@�@�@ PROM_OUT(10 downto 8), N_REG_A, REG_A); C5 : reg_dc port map (CLK_DC, REG_0, REG_1, REG_2, REG_3, �@�@�@�@�@REG_4, REG_5, REG_6, REG_7, �@�@�@�@�@ PROM_OUT(7 downto 5), N_REG_B, REG_B); C6 : ram_dc port map (CLK_DC, RAM_0, RAM_1, RAM_2, RAM_3, �@�@�@�@�@RAM_4, RAM_5, RAM_6, RAM_7, �@�@�@�@�@IO65_IN, PROM_OUT(7 downto 0), RAM_OUT); C7 : exec port map (CLK_EX,�@RESET, OP_CODE, P_COUNT, �@�@�@�@�@REG_A, REG_B, OP_DATA, RAM_OUT, P_COUNT, �@�@�@�@�@REG_IN, RAM_IN, REG_WEN, RAM_WEN); C8 : reg_wb port map (CLK_WB, N_REG_A, REG_IN, REG_WEN, �@�@�@�@�@REG_0, REG_1, REG_2, REG_3, �@�@�@�@�@REG_4, REG_5, REG_6, REG_7); C9 : ram_wb port map (CLK_WB, OP_DATA, RAM_IN, RAM_WEN, �@�@�@�@�@RAM_0, RAM_1, RAM_2, RAM_3, �@�@�@�@�@RAM_4, RAM_5, RAM_6, RAM_7, IO64_OUT); end RTL;

�ȉ��C �\�[�X�R�[�h �̓��e�ɂ��ĊȒP�ɕ⑫���܂��D

�ŏ��� entity �́C����CPU�� ���o�͐M�� ��\���Ă��܂��D

��{�ƂȂ�N���b�N( CLK )�ƁC���Z�b�g�M��( RESET )�CI/O�̓��͂Əo�͂̐M��(16bit)�ł��D

���̃v���O�����ł́CI/O��64�Ԓn�ɁC���Z���ʂ��o�͂���܂��D

����̐v�ł́C �������}�b�v�hI/O �������̗p���Ă��܂��D

���̕����́C �������A�h���X�iRAM�j �̈ꕔ���g���āC�O������� ���̓|�[�g �C��������

�O���ւ� �o�̓|�[�g �Ƃ��Ďg�p������̂ł��D

��������I/O������������悭�g���Ă��܂����C����͉�H�n�̊ȗ����̂��߁C

���̕������̗p���܂����D

architecture �� RTL ���̏��߂ɁC���p����R���|�[�l���g�i8��ށj���`���Ă��܂��D

�����̃t�@�C���i�Ⴆ�C clk_gen.vhd ���j�́C�{�́i cpu15e.vhd �j�Ɠ����f�B���N�g���ɒu��

�K�v������܂��D

�R���|�[�l���g�̋@�\���ɂ��ẮC 3.1 ���Q�Ƃ��Ă��������D

���ɁC�R���|�[�l���g�Ԃ̐M����ڑ����邽�߂̐M�����C signal ���Œ�`���܂��D

�Ō�ɁC����CPU�Ŏg�p����9�̃R���|�[�l���g �iC1�`C9�j ���L�q���C signal ���Œ�`����

�M����p���āC�R���|�[�l���g�Ԃ̐M����ڑ����܂��D

�Ȃ��C2�̃I�y�����h�ɑΉ����郌�W�X�^�i REG_A �C REG_B �j�̐M���������H�́C

�����R���|�[�l���g �i reg_dc �j���g�p���܂��D

�ȏ�̐����ŁC�������Ă��������܂����ł��傤���H

�s���ȓ_���c���Ă���ꍇ�́C�\�[�X�R�[�h��������x���Ӑ[���ǂݕԂ��ĉ������D

�T�D�@���s��

VHDL�̊J���c�[���ɂ́C �g�`�\�� ����� �V�~�����[�^ �̋@�\������܂��D

���̃V�~�����[�^��p���āC�����Őv���� CPU�̓��� ���m�F���Ă݂܂��傤�D

(1) �N������

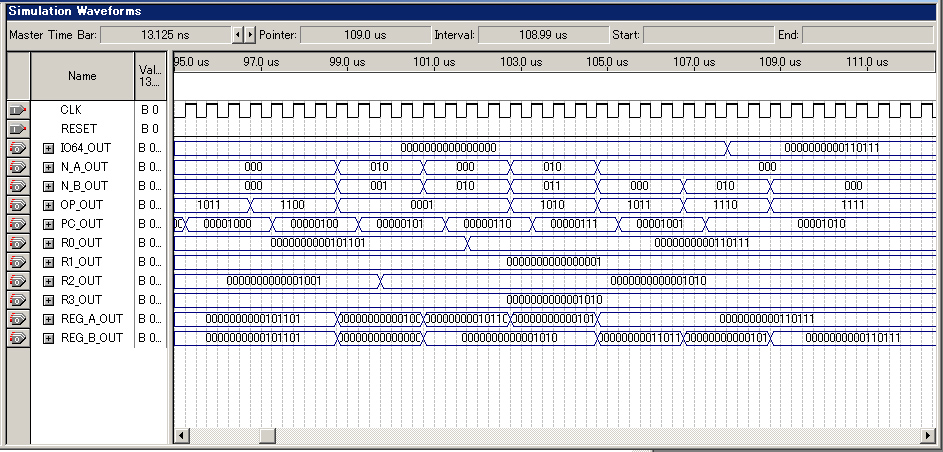

�V�~�����[�^ ���N������ƁC�e���̐M���͉��̐}�̂悤�ɕ\������܂��D

RESET ��C�v���O�����J�E���^ PC �̍X�V�ɂ��COP�R�[�h�i�}�� OP_OUT �j���ǂݏo����C4�̃��W�X�^

�i R0_OUT �C R1_OUT �C R2_OUT �C R3_OUT �j������̓�������Ă��邱�Ƃ�������܂��D

(2) �v�Z�I�����v�Z�I�����O�� �e���̐M�� �͉��̐}�̂悤�ɂȂ�܂��D

I/O�� 64�Ԓn �ɁC�ŏI�I�ȉ��Z���ʂ� 55 �ɑΉ�����2�i���i 0000000000110111 �j��

�o�͂���Ă��邱�Ƃ�������܂��D

�U�D�@�܂Ƃ�

�{�͂ł́CCPU�� �ŏ�ʊK�w �̉�H���C VHDL ��p���ċL�q���܂����D

���̊K�w�ɑ������H�́C �R���|�[�l���g �ɂ��L�q���Ă��܂����C���̏ڍׂɂ��ẮC

���� ��R�� �̒��ʼn�����܂��D