これらは同期型 V/F 変換器である点が前記の AD654 等と異なります。

AD7741/7742 データシート (131KB pdf)

クロック周波数の下限について、はっきりした記述は見当たらないのですが、規格は 200kHz 〜 6.144MHz クロックの場合について規定されています。 応用例に 5MHz クロックを使用しているものがあります。 スイッチトキャパシタンス積分器を使っていることからクロック周波数の下限はあるものと考えたほうがよいでしょう。 最大出力周波数はクロック周波数の 0.45 倍ですから、クロックを 5.4MHz に選んで 128 分周すると約 19kHz の出力が得られます。 2.7MHz で 64 分周という組み合わせもよいでしょう。

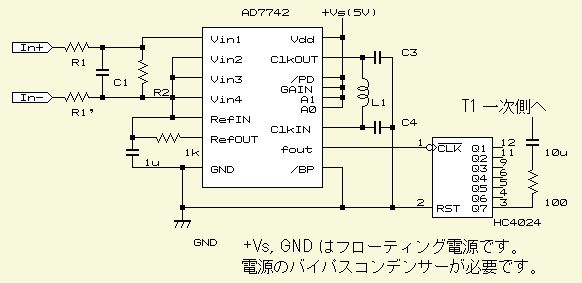

このクロックをどうやって発生させるか、けっこう問題ですが、とりあえず CR あるいは LC 発振器で済ませます。 クロック周波数のみを安定化させたところで利得・オフセット誤差が 0 になるわけではありませんので、これらのは誤差は自動調整する方向で考えます。

電源の GND と入力端子 In- の間には約 2.5V の電位差があることに注意して下さい。 入力電圧レンジは約±1.25V です。 R1, R1', C1, R2 の部分、T1 以降の部分は AD654 の場合と同じです。

L1, C3, C4 の回路でうまく発振できるかどうか、試していません。 ClkIN, ClkOUT ピンに直列抵抗が必要かもしれません。 うまくいかない場合は 74HCU04 などを使った外部発振回路にします。

RefOUT と RefIN の間に抵抗分圧回路を入れることも考えましたが、RefOUT の出力抵抗が大きく、RefIN の入力抵抗が意外と小さく、さらにコモンモード入力電圧が GND ピンに対して +0.5V 〜 Vdd - 1.75V という制限があるため、あまり自由にはなりません。

より高精度な製品も見つけました。

Generic Architecture No. of Channels Fout Max INL @ Fout Max Input Impedance Power Supply (V) IDD Max (mA) Price 100-499 pcs ($) Packages

AD652 Synchronous 1 Single-ended 2 MHz 0.01% FS Low/Medium Single +12/+36 ±15 10.46 16-Pin Cerdip

or Dual 6/18 & 20-Pin PLCC

AD652 データシート

(950KB pdf)