| 各種デバイスのモデリングについて、実例を紹介します。 セラミック・水晶振動子とラダー型フィルター 小信号ショットキーバリアーダイオード VDMOS FET OP アンプ パリスター 白金測温抵抗体 Pt100 白熱電球やネオンランプのモデルは、ここなどにあります。 files/Lib/Electrical Lamp/ files/adventures with analog/my model files/ |

|

| ● |

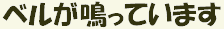

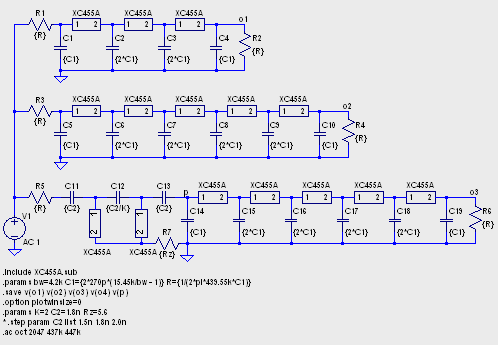

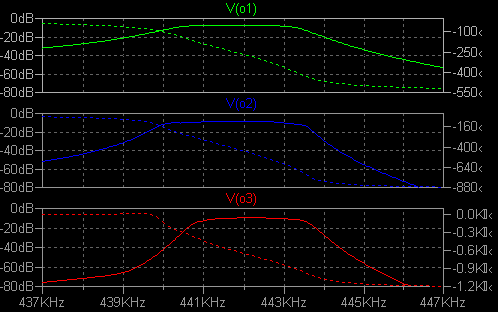

セラミック・水晶振動子とラダー型フィルター 最も簡単な2端子の等価回路を使います。  ものの本によりますと、 直列共振周波数 fs = 1/(2*pi*sqrt(Lm*Cm)) 並列共振周波数 fp = 1/(2*pi*sqrt(Lm*Cm * Cs/(Cm + Cs))) となります。 実際には fs, fp, Cs を測定して Lm, Cm を求め、これを .subckt 化するのが 普通です。 Lm, Cm は連立方程式を解けば求まりますが、私はこの手の計算が苦手で、すぐに間違え ます。 ですから数式処理プログラムのお世話になることに決めて います。 数式処理プログラム MAXIMA で解く方法 Cm = Cs*(fp**2 - fs**2)/fs**2 Lm = 1/(pi**2 * fs**2 * Cm)/4 具体例として、fs = 439.55kHz, fp = 455.0kHz, Cs = 270.0pF のセラミック振動子を .subckt 化します。 * fs = 1/(2*pi*sqrt(Lm*Cm)) = 439550. * fp = 1/(2*pi*sqrt(Lm*Cm*Cs/(Cm+Cs))) = 455000. * fp-fs = 15450. .subckt XC455A 1 2 L1 1 P001 6.78802m C1 P002 P001 19.3144p R1 2 P002 10 C2 1 2 270p .ends これの特性をシミュレーションで確認します。 拡大して見ても正確で した。(直列抵抗 Rs が 10Ωというのは小さすぎる値かもしれません。)  この振動子を利用して、簡単なラダー型のフィルターを作ってみました。 Cohn minimum loss タイプ です。 o1 は3段、o2 は5段、o3 は5段に加えて、低域特性を改善するためのT型 HPF を入れて あります。   resonator.zip |

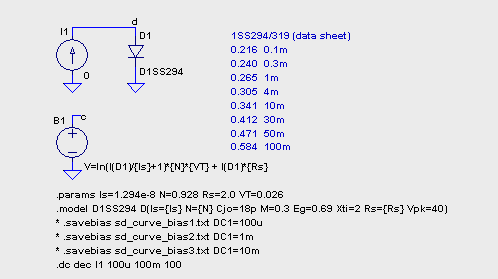

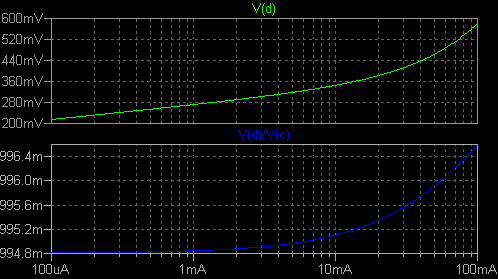

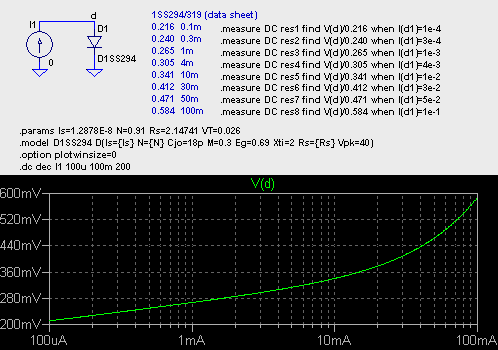

| ● | 小信号ショットキーバリアーダイオード 接合ダイオードに流れる電流の基本式は、 Id = Is*(exp(Vd/(N*VT)) - 1) ここで VT = K*T/q = 0.026V @ 27℃ です。これを Vd について解くと: Vd = ln(Id/Is + 1)*N*VT 少なくとも2つの Vd に於ける Id の値がわかれば、N と Is を決定できます。 1SS294, 1SS319 の データシートから次の値を読み取りました。 これは 25℃ での値ですが、まずはそのまま使います。 1SS294/319 0.216V 0.1mA 0.240 0.3m 0.265 1m 0.305 4m 0.341 10m 0.412 30m 0.471 50m 0.584 100m 大電流領域の値は直列抵抗 Rs のせいで基本式から外れますから、10mA 未満の値の組を使い ます。 理論式に基づいて Is と N を計算する MAXIMA のプログラムを作りました。 sac1.txt Id 0.1m 〜 0.3m Is = 5.082E-9, N = 0.8402 Id 0.3m 〜 1m Is = 2.867E-9, N = 0.7986 Id 1m 〜 4m Is = 1.027E-7, N = 1.109 Id 0.1m 〜 4m Is = 1.294E-8, N = 0.9279 このように大変大きく変動します。 グラフの読み取り精度と、そもそもフリーハンドで書いた グラフそのものに問題があるのでしょう。 結局 0.1m 〜 4mA の範囲から割り出したパラメーター値を 使ってシミュレートしてみました。 Cjo の値はデータシートから、その他はショットキーダイオードの 標準値を使います。 (Rs については後述)   100mA 時の V(d) がデータシートから読み取った値に近くなるように Rs を設定し ます。 カーソルを使ってグラフから V(d) を読み取りました。 まあ、大まかには合いま した。 0.1mA 215.1mV 1m 272.2m 4m 311.4m 10m 345.4m 100m 580.7m V(d)/V(c) のグラフは Vd = ln(Id/{Is}+1)*{N}*{VT} + Id*{Rs} という理論式で求めた値との 比較をしています。 これが 1.0 にならないところを見ると、LTSpice は異なったモデルを 使っていることがわかります。 しいて言えば 1mA 〜 10mA あたりの電圧を少し減らして Rs を大きくしたほうがよさそう です。 しかしそれをやるなら、savebias でエクスポートしたデータ、あるいは raw ファイル から ltsputil で切り出したデータと自作のプログラムを連動させてパラメーターの最適化を 行うのが現実的でしょう。 あるいは Rs を含み LTspice シミュレーション結果との微妙な差を 取り入れた理論式を作って、それに基づいてパラメーターを計算する MAXIMA プログラムを 作成する方法もあります。 後者の方法をもっと簡略化して、MAXIMA プログラムの Vd に補正を施して Is, N を算出し、再びシミュレートしました。 sac2.txt LTspice のグラフから V(d) を読み取りました。ずっとよくフィットしています。 0.1mA 216.1mV 0.3m 241.2m 1m 269.7m 4m 307.2m 10m 340.3m 30m 407.1m 100m 581.1m schottky.zip こちらの sbd_curve をご覧下さい。 |

| ○ |

もう少し楽にパラメーターを決める方法として、ガウスの最小自乗法

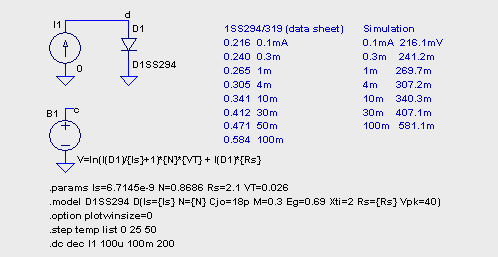

を用いて Is, N, Rs を一挙に多点のデータにフィットさせてしまう方法を試しました。 sac3.txt これで求めたデバイスパラメーターでシミュレーションを行い、結果を .measure で Error Log file に書き出しました。  res1: v(d)/0.216=0.977084 at 0.0001 res2: v(d)/0.240=0.988893 at 0.0003 res3: v(d)/0.265=1.00821 at 0.001 res4: v(d)/0.305=1.00409 at 0.004 res5: v(d)/0.341=0.999114 at 0.01 res6: v(d)/0.412=0.993941 at 0.03 res7: v(d)/0.471=0.986148 at 0.05 res8: v(d)/0.584=1.00712 at 0.1 Id = 300μA 〜 30mA の範囲なら 1% 程度にまで合致しています。 (50mA 時を無視すれば、Id = 100mA まで) schottky.zip こちらの sbd_curve2 をご覧下さい。 |

| ○ |

IF の温度依存性を計算する

とき、Is*(exp(Vd/(N*(k*T/q)))-1) 式は使えません。 デバイスの温度依存性を調べるには

.step temp list ...

を使います。  データシートのグラフを見たところ、50℃ の温度変化で電流が約 20 〜 30 倍変わるように 見えます。 このグラフも同程度の温度依存性を示していますから、パラメーター Xti は そのままにしておきます。(電流が大きな領域では温度依存性が小さくなります。) 東芝のデータシートは周囲温度 25℃ ですが、SPICE 関連分野では 27℃ を標準としています。この 違いを気にするのなら、上記のような温度依存性グラフから電流の温度係数を読み取って、デバイス パラメーターの Is を微調整すればいいでしょう。 schottky.zip こちらの sbd_tempco をご覧下さい。 |

| ○ |

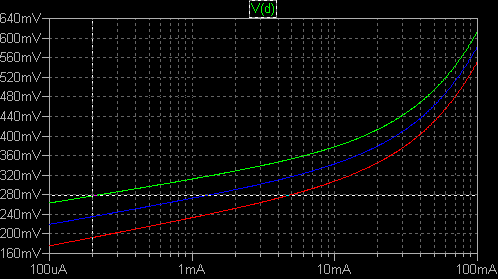

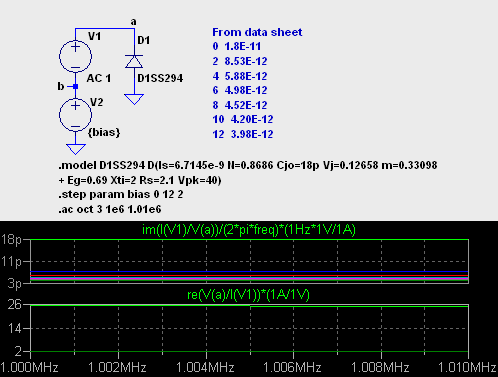

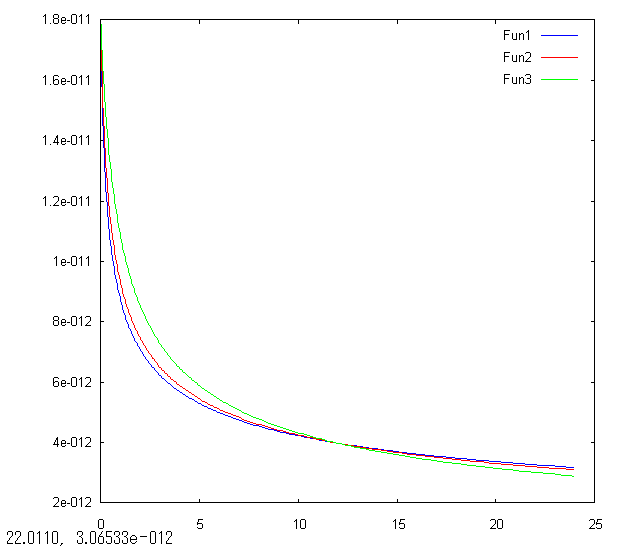

次は逆電圧時の端子間容量です。 まずはデータシートを読み取ります。 う〜ん、12V あたりを境に、どうも不連続のように見えます。 そんな高電圧領域を使うことは少ないと 思いますので、ここでは 12V 以下の逆電圧印加時のみを問題にします。 逆電圧 0V 時の標準容量 18p は 動かしません。 データシートのグラフを読み取りますが、私は pdf 拡大表示 → print screen → MsPaint 画面にペースト 後、カーソル位置を読み取って記録し、あとは計算で値を求めました。 cjo_vj_m.txt 方法は「バリキャップのカーブフィッティング」の最初のほうに書いておきました。 それを自動化 したわけです。 得られたパラメーターで AC 解析を行って容量値を求めます。  結果は、グラフのウィンドウが選択されている状態で File → Export します。 Format は Cartesian re,im で、「im(I(V1)/V(a))/(2*pi*freq)*(1Hz*1V/1A)」のみをエクスポートします。 0 1.80000e-011 2 7.07485e-012 4 5.68101e-012 6 4.98448e-012 8 4.53954e-012 10 4.22071e-012 12 3.97629e-012 逆電圧 0V と 6V 以上の場合は問題ないのですが、2V, 4V 時の容量が少なすぎます。 そこでプログラム を修正し、中間点の電圧を 4V, 2V としたパラメーターを算出し、シミュレートして みました。 cjo_vj_m2.txt

グラフに描くとこうなります。  元のデータシートのグラフをもう一度眺めると、22V で 3pF というのは信じたくなります。 これを 満たすのは D1SS294-2 です。 初 めから 0, 12, 22V とかのデータを使っていれば一回で済んだのに。 なんて、後の祭り。 もう少し 言うと、データシートの値は避けがたい浮遊容量も含んでいるはず。 これを入れても 22V, 3pF という ことは、理論式での計算は 3pF より小さいはず。 となれば、上記の Fun1 → Fun2 → Fun3 より もっと進んだ方向に、現実があるのかも。 schottky.zip こちらの sbd_cap をご覧下さい。 |

| ○ |

ダイオードには浮遊容量があるとして、これ

を考慮した式をガウスの最小自乗法を使って数値的に解いてみました。 まずは大まかな値を求めておき、その

後改めて Cjo, Vj, m, Cp (並列容量) の4変数をフィットさせます。 cjo_vj_m3.txt 次のようなパラメーターが計算できました。 Cjo=1.75011E-11 Vj=0.5193 m=0.4964 Cp=1.99796E-13 シミュレーションを行って、結果を前項と同様に Export します。 カッコ内はシミュレーション結果と データシートから読み取った値の比です。 1.77009e-011 (0.9834) 8.19084e-012 (0.9602) 6.17870e-012 (1.0508) 5.18439e-012 (1.0410) 4.56442e-012 (1.0098) 4.13063e-012 (0.9835) 3.80525e-012 (0.9561) 前項の方法ではデータシートから読み取った値と比較して最大 10% 近い差がありますが、今回の方法 では約 5% に収まりました。 理論式での計算値とシミュレーション値の違いはちょっと気になっています。 schottky.zip こちらの sbd_cap_cp をご覧下さい。 ・ 端子間容量の計算式は、ダイオード逆電圧を正としています。そのため一般の SPICE パラメーター 解説と符号が異なっている箇所がありますが、誤りではありません。 ・ 逆電圧時の漏れ電流は、高温になると無視できない値です。 これは BV, Ibv で指定でき ます。 Tt (transient-time) についてはデータシートに記載がないのでそのままにしま した。 そのほか Kf, Af (フリッカーノイズ係数、指数) も必要なら指定します。 ・ Fc (順バイアス時の容量減少係数) について何も言いっていません でした。 これはデフォルトの 0.5 のままにしてあります。 ・ 非直線性のあるキャパシタンスは Q=<式> を使って指定することもできます。 IF や table も使えます。 説明書のほか、LTspice ユーザーグループの files/Tut/Nonlinear Capacitance of Capacitors/ を参照して下さい。 |

| ● |

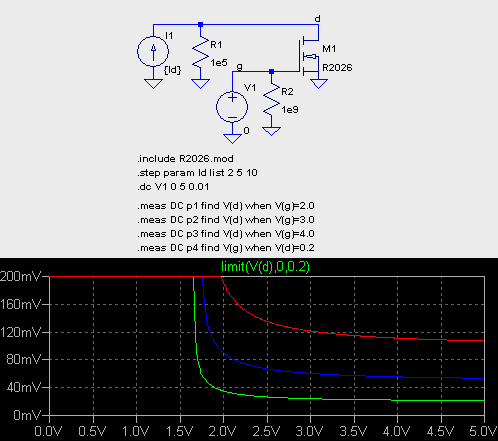

VDMOS FET LTspice には VDMOS という縦型パワー MOSFET のモデルがあります。 別のモデルを設けた 理由は次のように説明されています。 (i)モノリシック MOSFET の場合 body diode はサブストレートに接続されている が、VDMOS FET の body diode は外部端子に接続されている。 (ii) VDMOS FET のドレイン − ゲート間容量 (Cgd) は Vgd が 0V 付近で不連続的に大きく変わる。 ルネサステクノロジに HAT2026R という製品があります。 これの Vto, Rd, Rs, Kp の値を求めます。 方針は: (1) データシートから Vg - Id 値のペアを読み取り、あらかじめ適当なパラメーター初期値を設定しておく。 (2) デバイスパラメーター値は *.mod ファイルで受け渡す。 C 言語のプログラム で LTspice (scad3.exe) を -b オプション付きで起動し、結果 を .meas[ure] で *.log ファイルに出力させる。 (3) 同プログラムは *.log ファイルからデータを読み出し、データシートの値と比較しながらパラメーターを修正する。 (4) 上記 (2), (3) をくり返す。 LTspice のコントロールパネル、Operation の設定で、.net, .log ファイル を自動消去しないように指定しておく必要があります。 回路を作成後一回は シミュレーションを行って *.net ファイルを作成しておきます。  結果を示します。 C:\Program Files\LTC\asc\R2026>vdmos_cvfit 0 0.0417833 0.0351536 1 0.0580826 0.0617747 2 0.104791 0.109556 0 0.0407186 : 1.6894 0.00509963 300.268 1 0.0320963 : 1.679 0.00510003 300.534 ・・・ 48 0.000665062 : 1.55287 0.00555352 294.616 49 0.000664039 : 1.55268 0.00555325 294.402 Difference ratio: 1.0006 0.979852 1.01614 Id 値のデータシート値に対する比 Vto=1.553 Rd=5.553m Rs=4.165m Kp=294.4 最終的に求まったデバイスパラメーター たった3点のフィットだから、とてもよく合わせられるだろうと考えていたのですが、現実はそれほど甘くなかったようです。 R2026.zip こちらの vdmos_cvfit をご覧下さい。 C 言語プログラムは MSYS + MinGW 環境で作成しました。 makefile をご覧 下さい。 MSYS と MinGW の入手先はこちらです。 http://sourceforge.net/project/showfiles.php?group_id=2435 Windows ユーザーであれば: http://prdownloads.sourceforge.net/mingw/MSYS-1.0.10.exe?download http://prdownloads.sourceforge.net/mingw/MinGW-4.1.1.exe?download 私の場合、C プログラムの作成は msys\1.0\home\ 以下で行い、実行可能オブジェクト は makefile 中の cp で C:\Program Files\LTC\asc\R2026\ にコピーしてい ます。 作成したプログラムの実行は、・・\R2026 ディレクトリーにコマンドプロンプトへの ショートカットを作っておき、その作業ディレクトリーも同ディレクトリーとしておいて、 いわゆる DOS ウィンドウから vdmos_cvfit を実行しました。 なお C:\Program Files\LTC\ltsputil\WaitSec.exe を使用しています。 このプログラムは 指定した時間だけ実行を停止する機能を持っています。 LTspice user group から ltsputil と 共に入手できますが、clib の sleep() に置き換えることもでき ます。 但し sleep() を使うと実行停止時間が1秒単位になってしまいます。MSYS + MinGW 環境 では usleep() が使えないので、代わりに WaitSec を使いました。 |

| ○ |

パラメーターが3つで3点に合わせるのだし、Vto, Rd+Rs, Kp

の性質から見てもっとよくフィットできるはず、と考えてプログラムを作り直しました。 Vd の値は、電流の小さい領域で Vto

に大きく依存し、中電流では Kp に、大電流では Rd+Rs に大きく依存する、という性質を使っています。 収束がどうも遅いのですが 0.2%

程度まで合わせられました。 なお、R2026.mod の内容は最終レポート通りに更新されていません。 ご注意願います。 Vto=1.277 Rd=4.902m Rs=3.681m Kp=157.0 R2026.zip こちらの vdmos_cvfit2 をご覧下さい。 |

| ● |

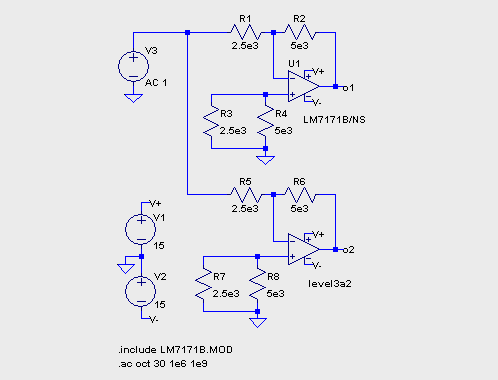

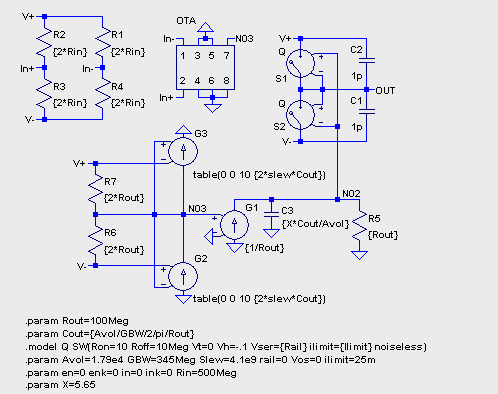

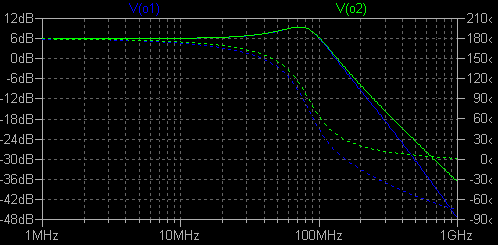

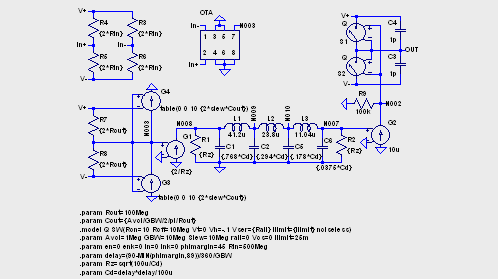

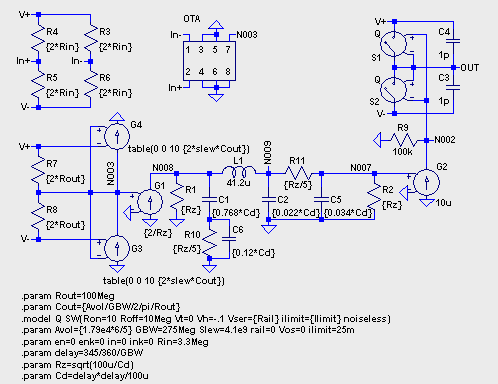

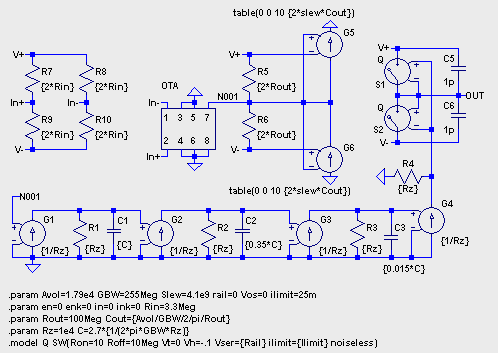

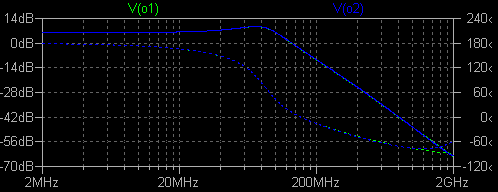

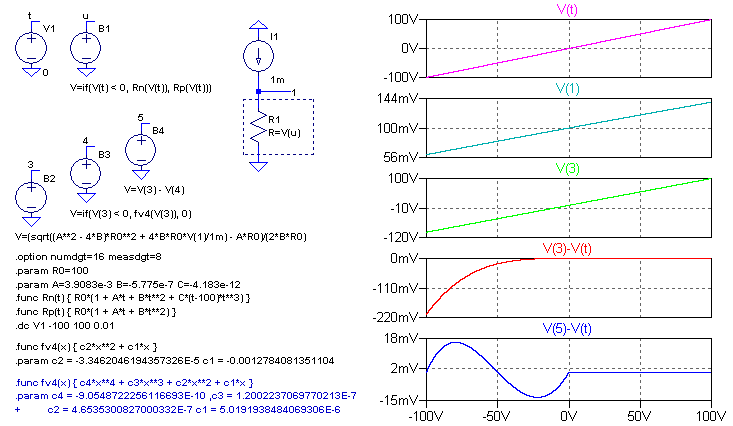

OP アンプ LTspice には UniversalOpamp という .subckt があって、下記のパラメーターを指定できます。 Avol = DC gain GBW = GBW product Slew = Slewrate limit ilimit = current limit rail = output stage saturation voltage Vos = offset voltage phimargin = phase margin en = equiv. input noise voltage density enk = equiv. input noise voltage density corner freq. in = equiv. input noise current density ink = equiv. input noise current density corner freq. Rin = Input resistance 最近安価に売られている LM7171 という高速 OP アンプがあります。 これの SPICE モデルは ご本家の NS が公開しているので、改めて作る必要はありません。 http://www.national.com/models/ → Amplifier Products → LM7171A.MOD, LM7171B.MOD (7171A と 7171B は 1 つのパラメータ値が少し異なるだけです。) UniversalOpamp を使って LM7171 をどの程度まで近似できるのか、level3a, level3b という 二種類の .subckt で試してみました。 しかしどちらを使っても、利得 >= 2 でないと不安定 という LM7171 の性質を実現できません。 また位相特性を見ると level3a と level3b の中間的 なものが欲しくなります。 調べてみると level3a は位相余裕 29 〜 86°間はていねいに処理されているのですが、もっと 位相余裕の少ない領域は放っておかれています。 level3b のほうはポールの数が多すぎるよう です。 そこでまずは level3a の中身を調べて、位相余裕の少ない領域に設定できるように 修正しました。 同時に、階層のある回路に書き直しました。 U1 は手本になる LM7171B/NS で、出力は o1 としています。 ノード o2 に出力しているのが、 今回作成した階層化回路 level3a2 です。  下位階層の回路とシミュレーション結果です。 パラメーター X が位相余裕の目安になっています。   およそ 100MHz あたりまではうまく合わせられるのですが、それを超えるとどうにもなりません。 opamp.zip こちらの a7171-3a2.asc, level3a2.asc をご覧下さい。 |

| ○ |

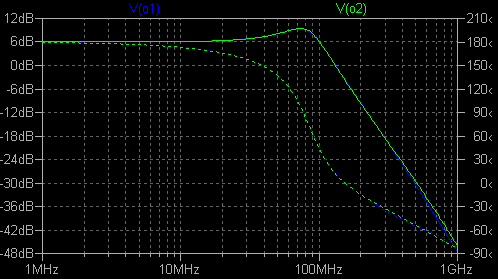

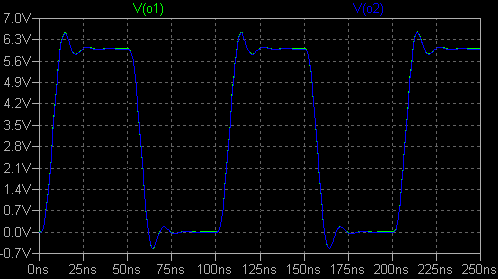

そこで UniversalOpamp level3b

の中身を調べました。 (level3b.asc) なんと3段の LC フィルターが追加されています。 これで試したのですが、今度は 位相遅れの段数・量がどうにも多すぎて困ります。 しかたなく level3b の回路を変更しました。  これを使ってシミュレートすると、約 500MHz くらまで合致させられました。  過渡解析も行ってみましたが、ほとんど重なります。 (見やすくするため、グラフの色割り当てを 以前とは逆にしてあります。)  opamp.zip こちらの a7171-3b2.asc, level3b2.asc をご覧下さい。 |

| ○ |

前項で紹介した level3b2 の

回路は、どうもやみくもに部品をくっつけて定数を調整した気配がありますね。 そこ

で、もう少し組織的な方法で試しました。  これで約 1GHz まで合致させられました。 しかしながら、帰還後の利得を 5, 10 などに変える と、LM7171B/NS とは合いません。 その理由はよくわかっていません。 現在はブラックボックス として扱っている OTA 部分に関係しているのかも知れません。 opamp.zip こちらの a7171-3b3.asc, level3b3.asc をご覧下さい。 こうなると LM7171B.MOD の中身がどうなっているのか知りたくなります。 opamp.zip 中 の cir7171.asc を見て下さい。 なかなか参考になります。 |

| ● |

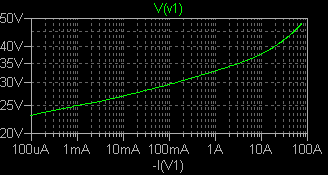

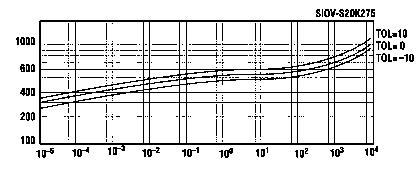

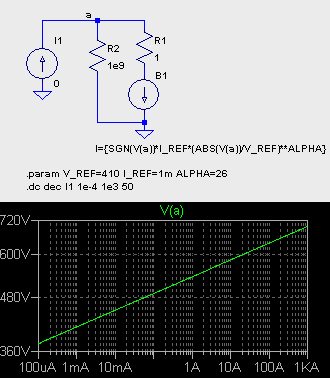

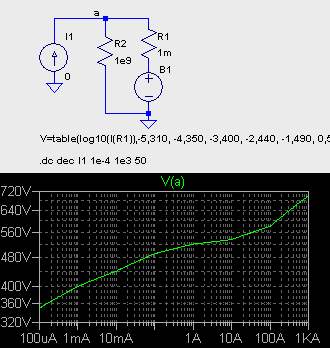

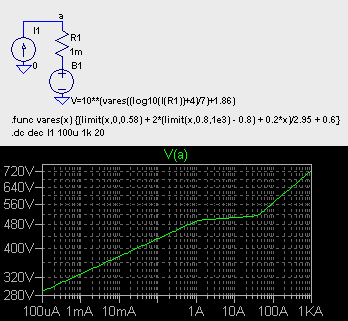

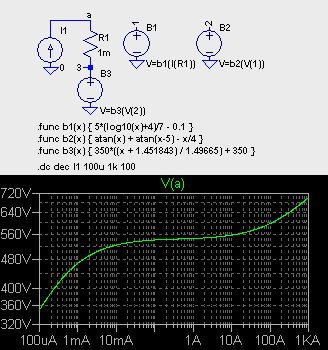

バリスター 回路の過電圧保護に用いられるバリスターは、探せば SPICE モデルが見つかります。 http://groups.yahoo.com/group/LTspice/ こちらの Files > Lib > Varistor > から入手したものを試してみました。  モデルが入手できる品種の場合は問題ないのですが、そうでない場合はどうしたらいい のか。 一般に使われているバリスターのモデルはかなり複雑で、5〜6個のパラメーター を設定しなくてはなりません。 もう少し簡便な方法を試しました。 ターゲットは、およそ 次のようなバリスターとします。 誘導性・容量性の寄生素子は除外しています。  (1) 両対数グラフで直線。 これならパラメーターは2つで済みます。  (2) 電流の対数と table() を使用する。 表の記述がちょっと長くなりますが。  (3) どうせ不連続点があるなら、4点の折れ線グラフで表現。  (4) atan() 関数で表現。 1mA 〜 100mA 付近の電圧が大きすぎます。 うまい 関数が見つかればいいのですが。  others.zip こちらの varistor-1 〜 varistor-4 をご覧下さい。 前記の (2) 〜 (4) について、正負対称の特性が必要なら abs() と sgn() を 追加した式に改める必要があります。 (1) の B1 式を参考にして下さい。 |

| ● |

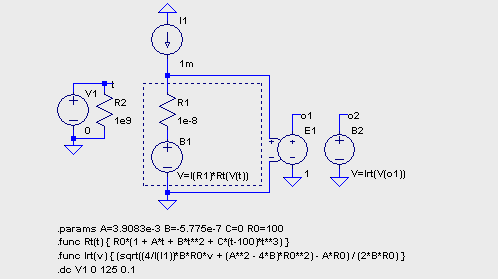

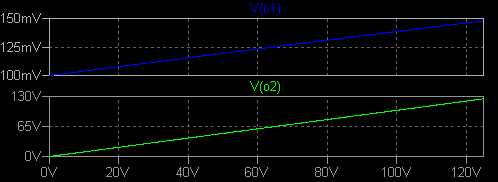

白金測温抵抗体 Pt100 これの温度特性を Web 検索したのですが、あまり見つかりません。 この分野 では温度を摂氏で表すのが普通です。 なお日本では JIS が改定になって、今だに その話題を聞かされます。 ・RT = R0*(1 + α*T + β*T^2 + γ*(T-100)*T^3) α = 3.9083e-3 β = -5.775e-7 γ = -4.183e-12 (below 0 degC), zero (Above 0 degC). ・SPICE の書式で書いたもの。 .param A=0.0039083 B=-0.0000005775 C=0 R0=100.00 .param Rt=R0*(1 + A*SensT + B*SensT*SensT + C*SensT*SensT*SensT*(SensT-100)) 3次・4次の係数は > 0℃ での話であるとして 0 にしました。 V(t) が測定点の温度を表しています。 .func Rt(t) が抵抗値を計算します。 .func Irt(v) は測定電圧 → 摂氏温度の変換用です。   others.zip こちらの Pt100 をご覧下さい。 注: 後日、抵抗器を R= の表現で書き表せることを知りました。  V1 が摂氏温度を決め、B1 が PtRTD の抵抗と温度係数を表現しています。 R1 が Pt100 です。 グラフの横軸は 1℃ = 1V に換算していますので、表示の温度範囲は -100 〜 100℃ です。 B2, B3, B4 で 測定電圧 → 温度 の逆変換をしています。 計算上の誤差は最大 ±16m℃ 程度です。 正の温度範囲の補正は B2 の式で、負の温度範囲の非直線補正は2次多項式を使い、 その係数は MAXIMA で求めました。定数の桁数がやたらに多いのですが、そのままにしておきました。 PtTS6.asc PtTS6.plt なお B2 式の計算は除外して、多項式近似で一挙に補正計算をするほうが実際的だと思います。 |

| もどる |

| |