| アナログ PLL |

|

| ● |

PLL と言っても

いろいろな使用目的がありますが、ここではデジタルデータ伝送に関して

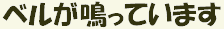

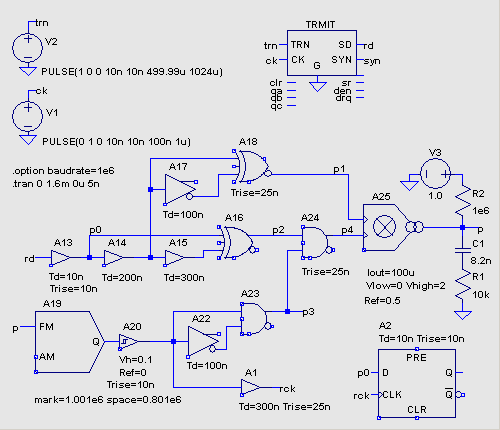

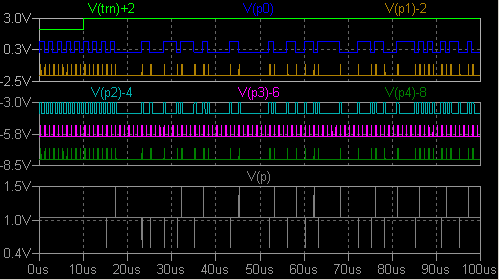

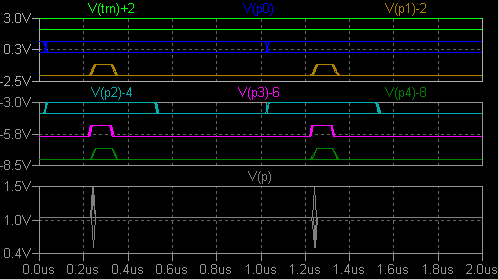

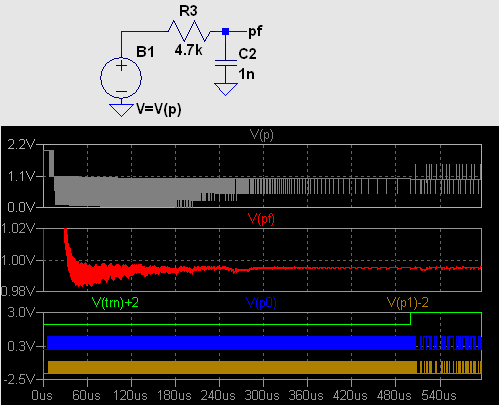

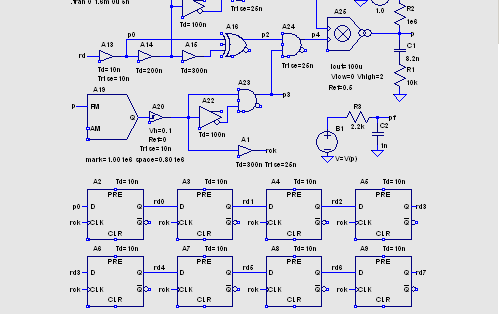

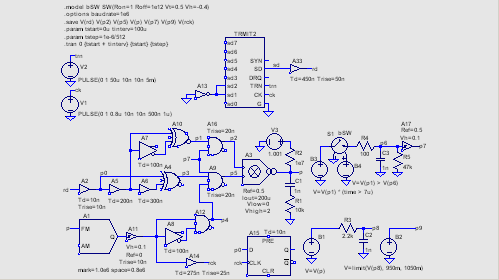

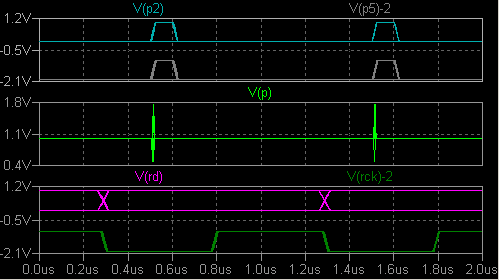

しばしば必要になるクロック信号の再生を話題にします。 部品として lib\sym\Digital\ に phidet 位相比較器が あります。 これと lib\sym\SpecialFunctions\ の modulate を使った PLL を構成してみました。  TRMIT は下位階層の回路で、CK (クロック) と TRN に応じてテスト信号を発生 します。 TRN が 0 のとき 0, 1 の交番信号を、1 のときデータと PN 信号 (擬似 ランダム信号) を乗算したデータを送出します。 データはベースバンド信号 で、とりあえずビットレートは 1Mbps にしてあります。 これの内容に ついては次項で説明します。 PLL の役割はクロックの再生です。 まず受信データの正負のエッジを A18 で検出 します。 A19 FM 発振器出力の正エッジと A16 で発生させた位相比較ゲート信号 の論理積を A25 PHASEDET で位相比較し、ローパスフィルター (C1, R1) を 通して A19 の発振周波数を制御します。 A25 PHASEDET には Iout, Vhigh, Vlow, Ref のパラメーターが あり、A19 MODULATE には mark, space といったパラメーターがあります。 これら を適当に設定します。 あとは LPF の CR 値ですが、C は応答周波数 (振動する 周波数) を決め、R はダンピングファクターを決定します。 細かく計算して も、シミュレーションして結果を見るとやはり変えてみたくなるものです。 受信クロック発振器のフリーラン周波数誤差を +0.1% としてあります。 全体の 大まかな動作は次のようになります。  およそ 300μs ほど経つと動作が安定しています。 0, 1 交番信号の区間の比率を やたらに大きくしてありますが、これはシミュレーション上の都合で、データ送信区間 をもっと長く取ることは可能です。 (後述) 490 〜 590μs の区間のデータのみを取り出し (.tran 0 590u 490u 5n)、さら に Eye Diagram を見てみます。 (アイダイアグラムについて は「デジタル信号伝送の歪み」を参照して下さい。)  Eye Diagram  p1 と p4 の立ち上がり時刻がうまく同期しています。 p3 の位置が、p2 が 1 である 区間の中央にあることも重要です。 apll1.asc trmit.asc apll1.plt trmit.asy 「300μs ほど経つと動作が安定」なんて言ったのですが、3つ前のグラフでは読み取り 困難ですね。 下記回路を追加してグラフを描かせました。  |

| ● |

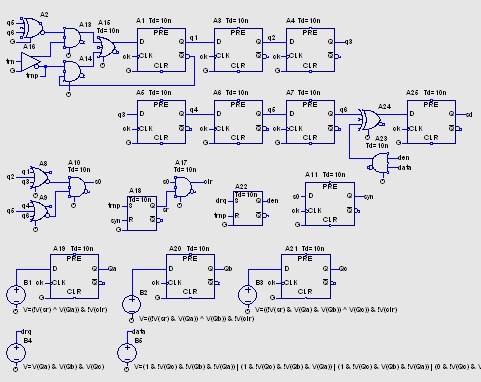

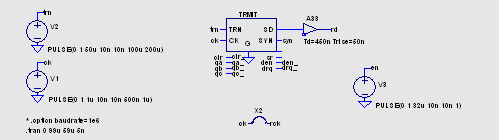

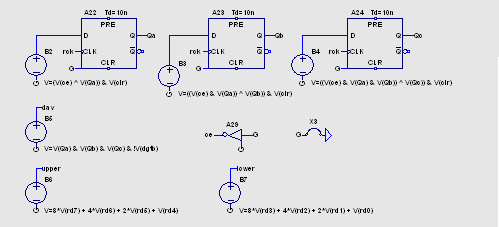

TRMIT (trmit.asc) の内容を次に示します。 上半分は PN 信号/0, 1 交番信号の発生器で、trn によって機能が切り換わり ます。 交番信号の直後の 8 bit は変調なしの PN 信号です。 それ以降は データと PN 信号を EXOR して送出します。 A23, A24 が データ変調あり/なしを切り換えています。 syn は PN シーケンスの 先頭を表すタイミング信号で、動作モニター用です。 A19 〜 A21 は 8 つのクロックを数える binary counter です。 ステアリング ロジック (D 入力につながる論理回路) は B の V= 式で書いてあります。 このほうが 記述が楽です。 drq (data request) はデータを取り込むタイミングを表し ます。 B5 が 8 bit パラレルデータをタイミングに応じて振り分けるデータ セレクターで、これも V= 式で書いてしまいました。 (長い!) 現在パラレルデータの内容は式の中に書いてある 0, 1 によって決まり ますが、これを V(SDn) とかに置き換えれば望みのデータを送信できます。 trmit.asy には部品の枠外に端子があります。 これらはテストポイントで、いずれは消す つもりです。 Control Panel → Save Defaults → Save Subcircuit Node Voltage に チェックをつけてもいいのですが、仮想メモリー・ディスク容量が余分に 必要になり、シミュレーション時間にも影響するでしょう。 トップレベルの 回路では、.save で必要なノードのみを指定すると処理が軽くなります。 |

| ● |

この回路に受信用のシフトレジスターを追加

すると、シミュレーションがハングして完了した % 値が増えていかなくなります。 Tools Control Panel → SPICE の Default Integration Method を modified trap から Gear に変えると最後までシミュレートできました。 それぞれ の積分方法の性質を Web 検索で調べてみました。

どうやら timestep が大きすぎたようです。 これを 2ns に変えると modified trap 法 でも実行できました。 しかし、結果が出るのに時間がかかります。 ここは やはり rck 生成までの部分とそれ以降を分けて、最後に統合シミュレーションを 行ったほうが能率的でしょう。 |

| ● |

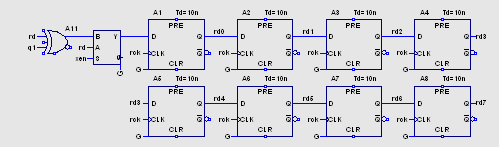

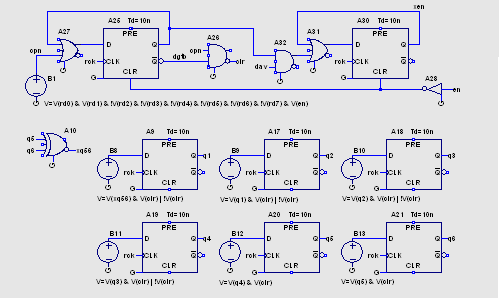

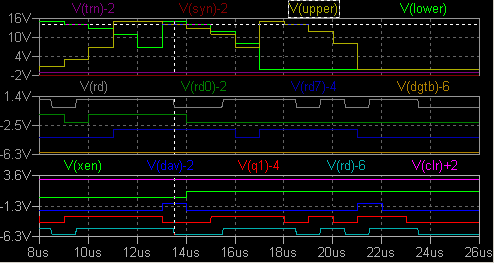

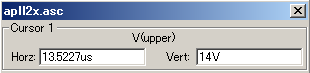

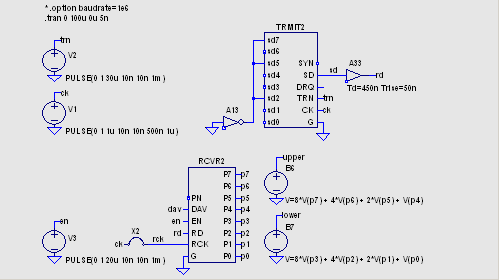

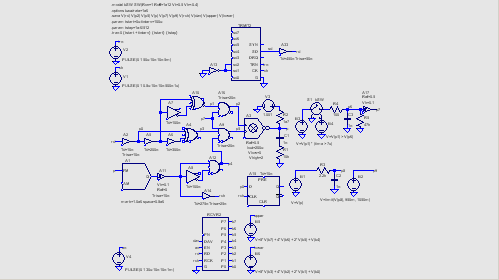

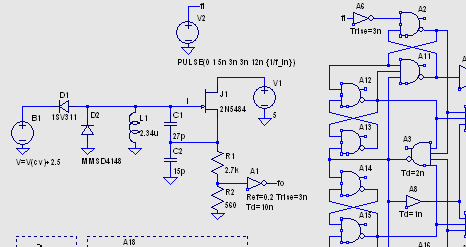

受信ロジック部分の動作確認を

しました。 一時 PLL は除外して、送信データを少し遅らせて受信部に

入力し (rd 信号)、受信クロック=送信クロックとしてあります。 ck は送信用クロック、trn は 0, 1 交番信号送出/データ送出を制御 します。 TRMIT が下位階層のデータ送信部です。  これ以下が受信部で、いずれは下位階層の回路として分離するつもりです。 A11 は PN 信号と受信データ EXOR します。A11 の右側にあるのは データセレクターで、1/4 74157 相当です。 xen が 1 のとき A11 出力 が A1 の D に入力されます。 それに続く 8 つの dflop は受信用シフトレジスターです。  A26, A30 dflop をクリアーしている en 信号は hunt mode に入れという意味を 持っており、ここで clr, xen を作り出します。 B1 が 0, 1 交番信号に 続く sync パターンを検出しています。 現在の sync パターンは 00000011 としてあります。 送信部の 6 ビットの PN 発生器 から出力される、実に特徴のある符号です。 A10 と 6 bit のシフトレジスター が PN 信号発生器で、プリセット機能付です。  A22 〜 A24 は 3 bit 同期カウンターで、同期クリアー付です。 B5 はそれのリップルキャリーです。 B6, B7 は受信シフトレジスターの値を D/A 変換し (uppder, lower)、過渡応答 グラフから 2 桁の 16 進数として容易に読み取れるようにするためのもので、動作試験用です。  D/A 変換器を実際に使っている場面のスクリーンショットです。 dav が 1 になって いる区間の rd7 〜 rd0 の上位 4bit を読み出しています。 画像が小さくて見にくいですが。   これで上位 4bit が 16 進数の E であることが読み取れます。 V(lower) のラベルを クリックすると下位の 4bit が読み出せます。 |

| ● |

送受信ロジック部を階層化した回路が一応

完成し、パラレルデータの送受信ができるようになりました。 シミュレーション

による動作試験は三段構えになっています。 (1) apll2.asc。 送信部と受信部を直結しての試験。 PLL 部は除外してあります。  (2) apll3.asc。 PLL 部改良のための構成。 受信部は除外してあります。  (3) apll4.asc。 全体の統合シミュレーション。 実行時には Gear 積分法を選択してください。  データは固定値を送っていますが、これは A13 の出力をつなぎかえれば 変更できます。 ハードウェアが認識する sync パターンは 0x03 で、これは 受信側に伝わりません。 受信側に伝わる最初の byte は 0xef で、この後に データバイトが続きます。 受信部にはパラレル 8 bit 出力データレジスターを追加してあります。 ファイル数が多くなりましたので zip 形式にしました。 apll234.zip LTSpice が動作中なら一旦終了します。 *.asy ファイルは LTC\SwCADIII\lib\ 以下の適当な ディレクトリーに移動またはコピーします。 apll?.asc を初めとする 8 つの *.asc ファイルを 選択して LTSpice を起動し、apll2.asc, apll3.asc, apll4.asc のうちの1つを選択して Run を クリックするとシミュレートできます。 TRMIT2, RCVR2 のほかに、いくつかの階層化回路を使っています。 dsel.asc/asy データセレクター (1/4 74157/158 類似) reg8e.asc/asy 同期ロード 8bit レジスター sqsell.asc/asy 同期シーケンサーの基本セル たまに意図に反して Plot Settings の Eye Diagram が Enable されてしまうことが あります。 過渡応答グラフ表示の表示が不審なときは Eye Diagram の設定を見直して下さい。 |

| ● |

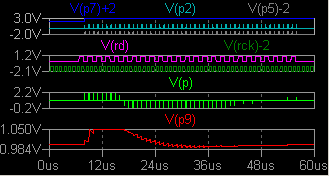

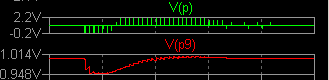

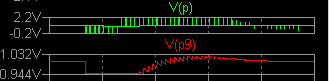

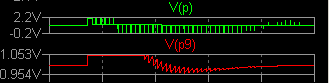

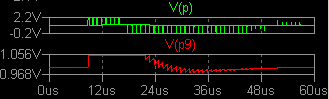

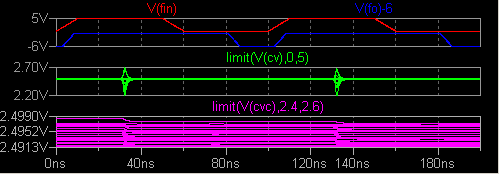

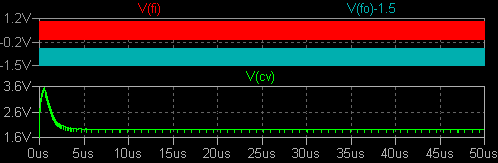

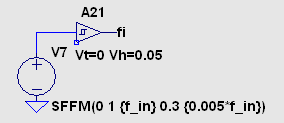

PLL の引き込み時間を調べていくと、初期の

無信号区間でも位相比較器が動作しているせいで、安定までに長い時間を要していた

ことがわかりました。 信号有無の検出回路を追加すると 40 〜 50μs で安定します。 apll3.asc で調べた 60 〜 160μs の区間のアイダイアグラムです。 目で 見た限りでは文句の付けようがありません。  位相比較器が動作を始めた瞬間の2信号の位相差によって PLL 応答の見た目の様子は 異なります。 この位相は V1 の Tdelay で設定できます。 なお V(p9) は limit() で 1V ±50mV に クリップしています。 0.2μs  0.4μs  0.6μs  0.8μs  1.0μs  このグラフの横軸は時刻 0 から始まっており、最初の約 8μs は無信号区間です。 |

| ● |

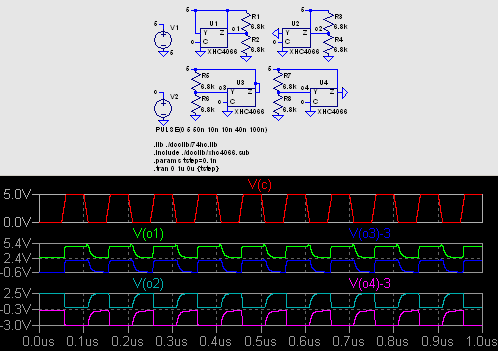

できあいの Phidet と modulate は少し抽象的過ぎる

気もします。 入手容易な部品で構成した場合のシミュレーションを試しました。 まずは位相比較器ですが、ランプ UP/DOWN の電流源がここでの悩みの種になり ます。 ダイオードスイッチ、CML スイッチ、JFET スイッチ、74HC125 なども 考えてみたのですが、Philips Semiconductors から 74HC4066 のトランジスターモデルが 入手できたこともあって、まずは HC4066 の基本的な Vdd, Gnd へのスイッチ動作を調べました。  少し波形がきれいすぎです。 Y と Z を入れ換えても、この接続ではほとんど差が見られません。 apll2.asc xhc4066.sub xhc4066.asy (74hc.lib は http://groups.yahoo.com/group/LTspice/files/Lib/Digital%2074HCxxx/ から 入手しました。 X74HC4066 のモデルは http://www.standardproducts.philips.com/support/spice/ から 入手したファイルの必要な部分を抜き出したものです。 Philips 社のこのモデル は注意書きがたくさんある通り、使用がむづかしい面があります。) 次に位相比較器の出力に接続してみます。 (但し負荷は 6.8k // 6.8k)  これもきれいすぎです。 apll3.asc どちらにしても、トランジスターレベルのシミュレーションでは時間がかかりすぎ ます。 かといって timestep を大きく取ると信じられないような波形が見えます。 そこで SW を使った動作モデル (behavior model) に乗り換え、スイッチ制御信号 の feed-through (信号への漏れ) を模擬する場合はコンデンサーを接続します。 |

| ・ |

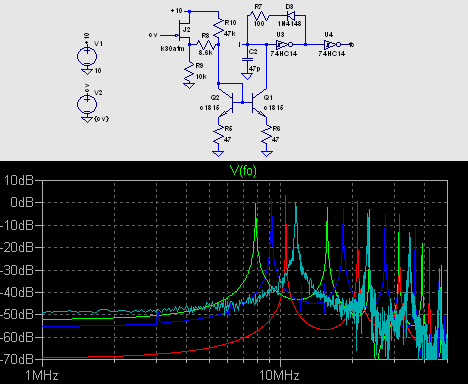

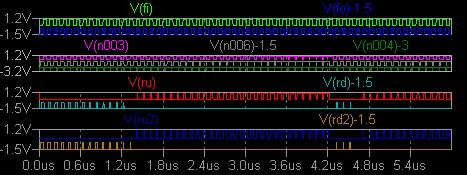

VCO (10MHz) は安価な部品で構成しました。 量産品

にはとても使えない回路です。 JFET の Idss や HC14 のトリップポイント、ダイオードの

パラメーターにとても敏感です。 次の FFT グラフは制御電圧 cv を 1, 2, 3, 4V と 変化させています。 約 16MHz 以上の成分は方形波の高調波です。 +10V 電源を使っています が、工夫の余地はあるでしょう。 この種の回路は位相ノイズが大きくなりがちです。 これを シミュレーションに含めるには積極的にノイズ源を導入する必要があります。  上記シュミットトリガー発振回路をシミュレートするとき、V(i) の初期値を .ic で指定しないと うまく実行できない場合があります。 74HC4046 の VCO を使うつもりなら、出来あいの modulator とシュミット回路で 充分ではないかと思います。 発振周波数の非直線性も考慮したいのであれ ば B 電圧源で演算するとよいでしょう。 |

| ● |

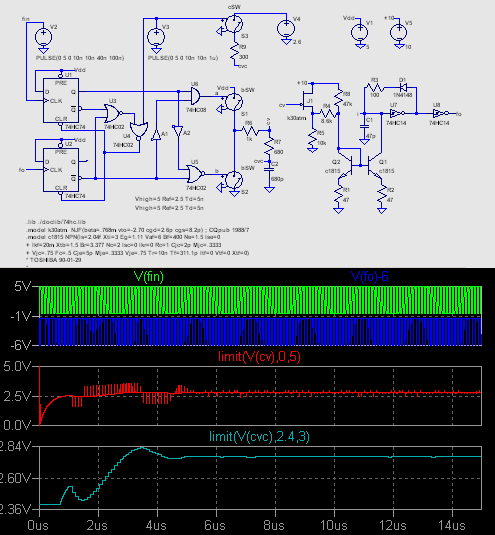

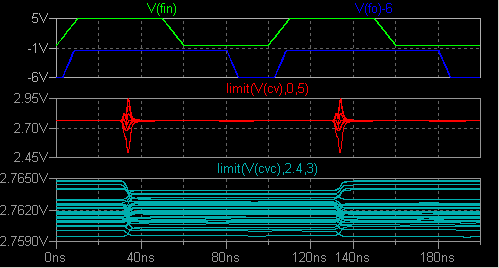

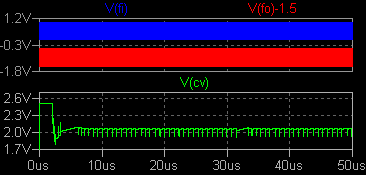

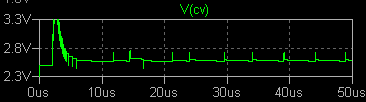

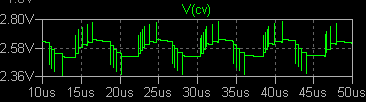

基本的な PLL の過渡応答です。最初の 1μs は

ループ動作を禁止しています (V3 が禁止信号)。 Timestep を思い切って小さくしない

と、うまくシミュレートできません。 一般に Timestep を変えると結果の評価が大きく異なるよう

であれば、その値を見直すのがよいでしょう。 応答は少しオーバーシュート気味です。 安定したと思われた後も V(cvc) 電圧にノイズが見られ ます。 しかし 8 〜 16μs の区間のアイダイアグラムを見た限りでは V(fo) の 位相ジッターが格別大きいわけでもないし、まあ問題なさそうです。  apll4.asc |

| ● |

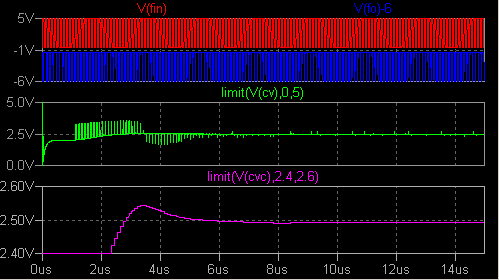

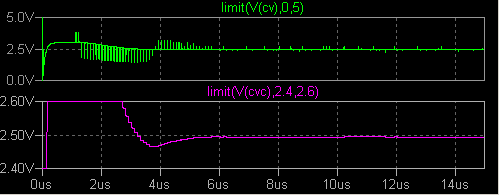

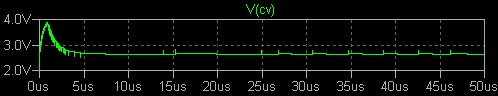

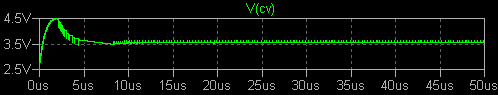

もう少し動作点を追求してみました。 各部の

部品定数のほか、VCO の 1N4148 を MMSD4148 に変更しました。 VCO のフリーラン

バイアス電圧 2V と 3V の場合の過渡応答グラフを示します。 なお先頭

の 1μs は PLL のループ動作を禁止しています。 V4=2V  V4=3V  V4=2.4V、7 〜 15μs の区間のアイダイアグラム  VCO の制御電圧と発振周波数の関係を調べるのに .step と FFT が便利に使えました。 とは 言っても各部の波形を確認した後で FFT を行わないと、落とし穴にはまる危険があります。 最後の最後には、位相比較器のオーバーラップ時間を決める A1, A2 遅延素子 の Td を設定しました。 PLL の応答にかなり影響があります。 apll5.asc ★ 注意 ★ 例にあげた位相比較器は 2 つの D-FF をクリアーしている期間がデッドタイム になるため、周波数が同じで位相がおよそ 180°ずれた信号に対して誤った 動作をすることがあります。 これは非同期順序回路を使って解決でき ます。 http://www.fairchildsemi.com/ds/MM/MM74HC4046.pdf の FIGURE 5. PLL State Tables および FIGURE 6. Logic Diagram for Phase Comparator II を 参照して下さい。 |

| ● |

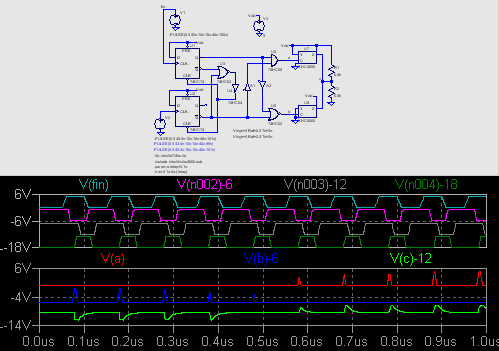

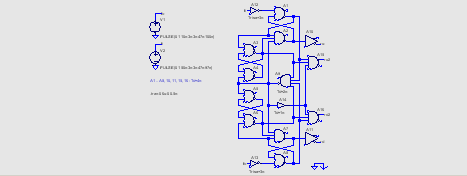

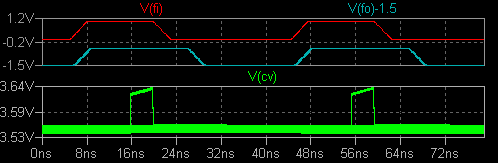

前項で紹介した「非同期順序回路による位相比較器」

を試してみました。 ru2, rd2 信号を作っている A14 〜 A16 は、私が即席に

追加した「ramp up/down のオーバーラップ」修正

回路です。 本格的には、もっと賢いやりかたがあると思います。  fi と fo を入れ換えて実行すると、一応全部を見たことになります。 asphdet.asc asphdet.plt |

| ● |

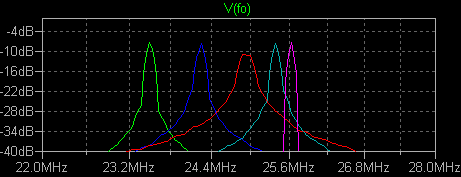

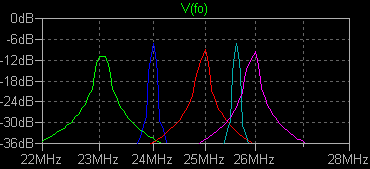

バリキャップ (varactor) を使用

した 25MHz VCO を試しました。 1SV311 のモデルはデータシートの値に

合うように Cjo, m, Vj を調整したもので、逆電圧 1V 以下・4V 以上の

ときの容量値は少しいいかげんです。 制御電圧 V(cv) を 0, 1, 2.5, 4, 5V と変化させた場合の発振周波数です。  制御電圧が 4 〜 5V あたりが少し詰まっていますが、1 〜 4V の間を見れば、けっこう 直線的です。 B1 は 単なるレベルシフターで間に合いますが、VCO 発振周波数での出力インピーダンスは 十分小さくなくてはなりません。 3種類の入力周波数について 0 〜 50μs の過渡応答を示します。 どちらか と言うと安定化後の位相ジッターを重視しています。 24.7MHz  25.0MHz  25.3MHz  入力信号 25.3MHz 時、20 〜 60μs 区間のアイダイアグラムです。  バリキャップ VCO 使用時、制御電圧パルスが発振器に望ましくない影響を与えることがあり ます。 ノッチフィルターなども試してみたのですが、回路図の A1、発振器と 位相比較器の間に入れるバッファー増幅器の遅延時間を調整するのが最も効果がありました。 apll6.asc apll6.plt 回路図のうち、破線に囲まれた部分はテスト用です。 R5, C3 接続点のラベル cv を V3 + 出力に移動させ、コメント化されている * .step param cv list 0 1 2.5 4 5 * .tran 0 10u 2u {10u/16384} uic を生かせば、VCO の制御電圧・発振周波数の関係を調べることができます。 A1 出力のラベル fo を A19 出力に移動させると、VCO を理想 modulator に置き換えることが できます。 Modulator のパラメーターは mark={(f_mid + 1.5*f_low)/2.5} space={f_low} としてありますので、 .params f_mid=25e6 f_low=23e6 ; for modulator のように、中心周波数・最低周波数で指定できます。 中心周波数に対応する 制御電圧は 2.5V ですが、これは modulator の mark 指定式を 修正すれば変えられます。 |

| ● |

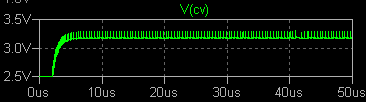

入力周波数が時間と共にゆっくり変動したり、信号の

遷移時刻が理想とは異なって激しく小変化 (ジッターといいます) した場合の動作を調べます。 まずはバリキャップ 1SV311 のモデルパラメーターを再検討しました。 (計算式は ここ を参照してください。) データシートに記されている標準値は C1V/C4V = 2.1、Rser = 0.28 です。 容量値をグラフから読み取ると: 1V 10**(294/289) = 10.41p 2V 10**(256/289) = 7.688p 3V 10**(226/289) = 6.054p 4V 10**(200/289) = 4.921p ln(c1v/c2v)/ln(c1v/c4v) = ln((Vj+2)/(Vj+1))/ln((Vj+4)/(Vj+1))、Vj=2.610 ln(c1v/c3v)/ln(c1v/c4v) = ln((Vj+3)/(Vj+1))/ln((Vj+4)/(Vj+1))、Vj=3.114 幾何平均をとって Vj = sqrt(2.610*3.114) = 2.85 とすると、 m = ln(c1v/c4v) / ln((Vj+4)/(Vj+1)) = 1.30 Cjo = c1v * (1+1/Vj)**m = 15.38p 検算 Cjo/(1+1/Vj)**m = 10.41p Cjo/(1+2/Vj)**m = 7.708p Cjo/(1+3/Vj)**m = 6.041p Cjo/(1+4/Vj)**m = 4.921p よって .model D1SV311 D(Is=2p Cjo=15.38p m=1.30 Vj=2.85 Rs=0.28) を使います。 一部の定数を修正後、VCO 制御電圧 V(cv) を 1, 2, 2.5, 4, 5V と変えて発振周波数を調べました。  動作開始直後の 2μs は PLL のループ動作を禁止する回路を追加し、入力周波数 を 24.7, 25.0, 25.3MHz と変えて応答を調べました。 (このグラフ先頭 の 2μs は PLL 動作が禁止されています。 V6 がループ動作許可信号です。) 24.7MHz  25MHz (+方向が少しクリップしていますが、電圧幅を統一しました。)  25.3MHz  |

| ・ |

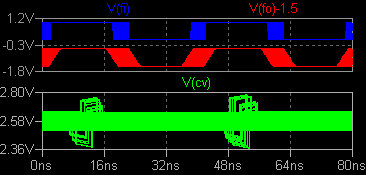

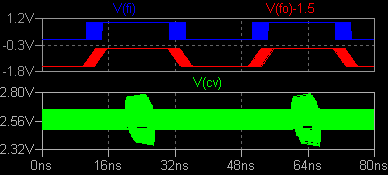

入力周波数を正弦波で FM 変調した場合の挙動を

調べました。 キャリアは 25MHz、変調周波数 125kHz、ピーク周波数偏移は ±78.5kHz です。  10 〜 60μs の区間のアイダイアグラムを次に示します。 アイダイアグラムの 周期は 1/25MHz 固定ですから、入力信号 V(fi) の遷移時刻も広がって見えます。入力の ジッターに比べて、出力のジッターがやや大きいのが特徴的です。  |

| ・ |

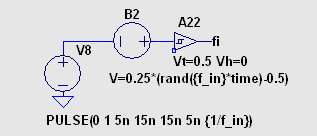

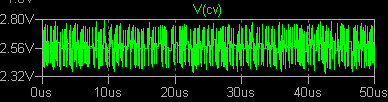

次にランダムなジッターに対する影響を調べ

ます。 B2 式の rand() については「おぼえ書き (使い方メモ)」を参照して下さい。  10 〜 60μs の区間のアイダイアグラムを次に示します。  前項の FM 変調の場合と比べて、アイダイアグラムで見た入力のジッターの程度はほぼ 同じです。 こちらのほうが V(cv) の変化が激しいにもかかわらず、出力 V(fo) の ジッターは小なくなっています。 これは、FM 変調の場合は周波数変化が一方向に進むのが 普通であるのに対して、ランダムノイズの場合は周波数変化が短い時間内で打ち消し合う 傾向にあるからでしょう。 apll7.asc apll7.plt A21, A22 の Trise を指定し忘れました。 位相比較器入力には Trise を指定した インバーターがあって、結果に影響はありませんので放ってあります。 |

| もどる |

| |