���@�����e�[�}63

�����e�[�}63�F�uPIC24F�ɂ��AAD9834 DDS���W���[���̎����v

�iStrawberry Linux�Ђ̏��^DDS���W���[���̊ȒP�Ȏ��������Ă݂܂����B�s���Ŏ莝����6MHz

X'tal OSC�œ������܂����B�j

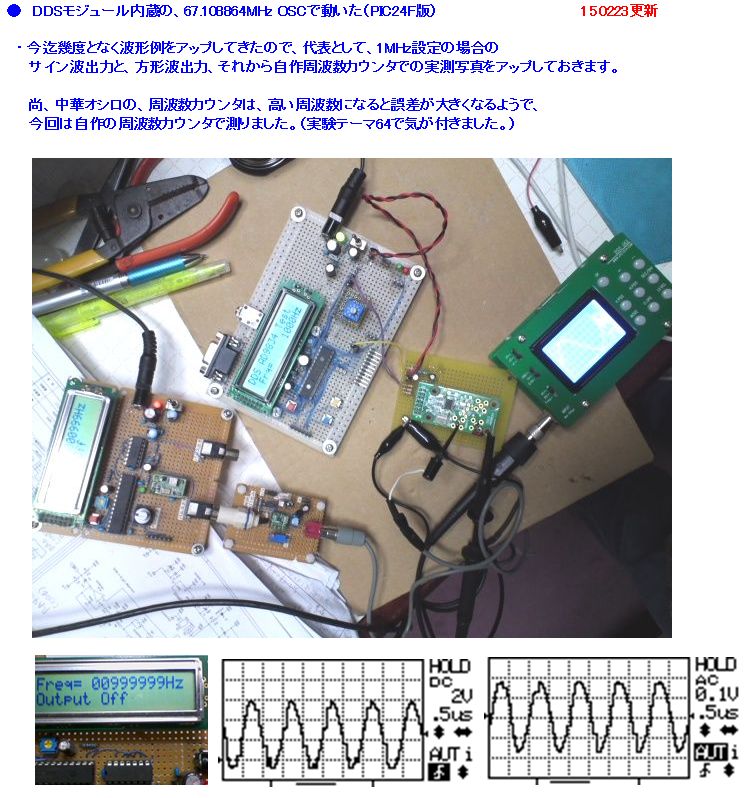

���@2015/2/23�X�V

�@�@ �����́A67.108864MHz OSC�œ����܂����I�I

�E�ȉ��A���̎����̓^���L�ł��B

���@2014.12.10

�@�@�EDDS�i�_�C���N�g�E�f�W�^���E�V���Z�T�C�U�j�����̔��U��������̂͏��߂Ă����A

�@�@�@�́A�T�C���g�́A1�T�C�N�����̐U���f�[�^���i�[�����ASIN

ROM�́A�A�h���X���J�E���^�ʼn�

�@�@�@ROM�o�͂̌�ŁADAC���@LPF����ăT�C���g�o�͂�悤�Ȃ��Ƃ͌o��������B

�@�@�@DDS����{�I�ɂ́A����Ɠ��������̂悤���B

�@�@�@DDS�́A�������g���̃N���b�N��p���ď��x�̍����T�C���g���\�ł���B

�@�@�@DDS�̐S�����́u�N���b�N���ƂɎ��g�����W�X�^������̐������Z�����

�@�@�@�A�h���X�E���W�X�^= �ʑ��A�L�������[�^�v�ł���B

�@�@�@�܂�A�O�L�́A�A�h���X�J�E���^�ɑ�������Ǝv���Ă悢�Ǝv���B

�@�@�@����̎����ړI�́ADDS�̂����݂��A������ʂ��Ċw�K���邱�ƂƁA���̃v���O���~���O��

�@�@�@�̌����邱�Ƃɂ���B

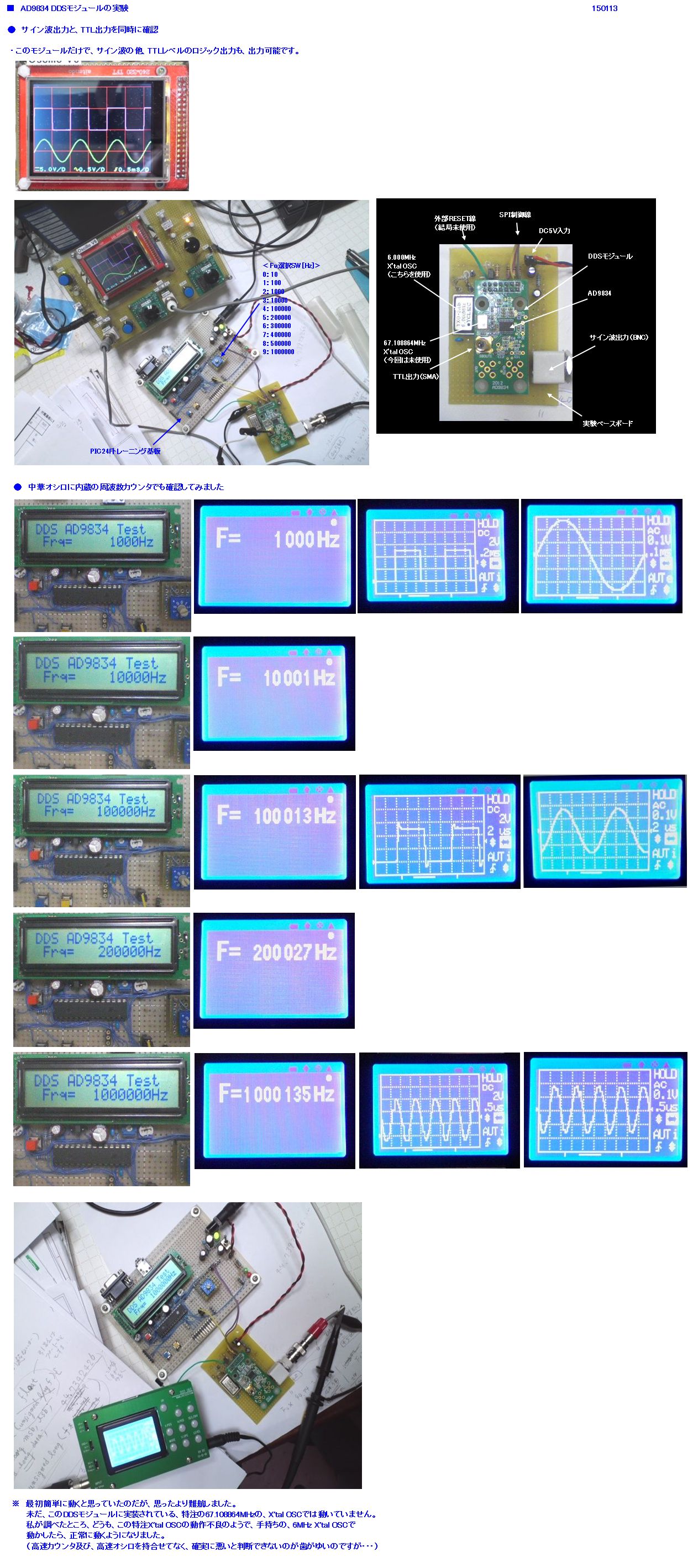

�@�@�E���̃��W���[���́A3����SPI�Ő��䂳���B

�@�@�@DDS���W���[���̓d�����A�}�X�^�[�N���b�N���W���[�����܂߂āA5V�Ȃ̂ŁA5V�n��MPU��

�@�@�@�g���̂��悳�����B

�@�@�@WEB������Ă��APIC�ł���Βf�R�APIC18F���g���Ă���Ⴊ�����B

�@�@�@��������́A�R���p�C��C18���C���X�g�[������K�v������B�i�����ł͂��邪�E�E�E�j

�@�@�@����͎莝���̃g���[�j���O��Ƃ��Ďg������Ă���A�d����3.3V�n�ɂȂ邪�A

�@�@�@�uPIC24FJ64GA002�v���g�����Ƃɂ����B

���@2014.12.12

�@�@�EPIC24F��3�̃|�[�g�ŁA�\�t�g�E�G�ASPI��g�݁AAD9834�𐧌䂷�邱�ƂɂȂ�B

�@�@�@�����n�[�h�I�ɖ��Ȃ̂́A�e�f�o�C�X�̓d���d���̈Ⴂ����A���W�b�N���x���̐�����

�@�@�@���Ȃ��Ƃ������Ƃł���B

�@�@�@���ׂ��Ƃ���AAD9834�́ASPI�s���̃��x���d�l�́A

�@�@�@Vih(min)= 2.8V�iVdd=4.5�`5.5V���j

�@�@�@Vil(max)= 0.8V�iVdd=4.5�`5.5V���j

�@�@�@����APIC24F�̏o�̓s���d�l�́A

�@�@�@Voh(typ)= 2.6V�i�W���ŁAVdd-0.7�j

�@�@�@Vol(typ)= 0.4V

�@�@�@�Ȃ̂ŁALo���x����OK�����AHi���x���́AHi�Ƃ��ĔF������Ȃ����ƂɂȂ�B

�@�@�@�����ŁAPIC24F�́ASPI�|�[�g�o�͂́AO.D�i�I�[�v���h���C���j�ݒ�ɂ��A�O���v���A�b�v

�@�@�@�i10k�ɂ�+5V�ɂ�j���邱�Ƃɂ����B

�@�@�ESPI�̃^�C�~���O�\�t�g�͂Ȃ�Ƃ��Ȃ肻���Ȃ̂ŁA

�@�@�@DIP SW�Ő��_�X�|�b�g���g����ݒ�ł���悤�ȊȒP�ȃe�X�g�v���O�������쐬���Ă݂�B

�@�@�E�܂��͐������ʼn�H�}���쐬�����B

���@2014.12.13

�@�@�E�X�g���ׂ�E���i�b�N�X�Ђ́uAD9834 ���^DDS���W���[���v���A1����z�����B

�@�@�@���̑��A�����p�p�[�c��������z��

���@2014.12.17

�@�@�E�X�g���ׂ�E���i�b�N�X�Ђ́uAD9834

���^DDS���W���[���v���A�ǂ���������H

�@�@�@�@�@���W���[���L�b�g�ɂ́ASMA�R�l�N�^���A3�t�����Ă��邪�A�g���ɂ����̂�

�@�@�@�@�@ �g��Ȃ��B

�@�@�@�A�@�T�C���g�̏o�͂́A�莝����BNC�R�l�N�^�֏o�������̂ŁADAC-Iout�s����

�@�@�@�@�@ �o�̓R���f���T�FC12=20p�̗��[�́A�����h�i5.08mm�s�b�`�j�𗘗p���āA

�@�@�@�@�@ ������3�s���̃s���w�b�_ ��2�ԃs���������̂��������A���̎����x�[�X�{�[�h��

�@�@�@�@�@ �X�^�b�N�ڑ����邱�Ƃɂ����B

�@�@�@�@�@ �x�[�X�{�[�h�̕��ɁABNC����������悢�B

���@2014.12.19

�@�@�E�|�[�g���t�A�����v���A�b�v�̐ݒ�AO.D�ݒ蓙�������A�e�X�g�v���O������g�ݎn�߂�B

�@�@�EAD9834�́ASPI����ɂ��Ă��������AWEB�������Ď荠�Ȃ��̂��������̂ŁA�ŏ��͂����

�@�@�@�q���邱�Ƃɂ����B

�@�@�@�q�،��́Ahenteko.org�́A�uAD9834���g�����A�����p�@DDS-VFO�̐���v�y�[�W�ł��B

�@�@�@�����ɋL�ڂ���Ă����A�\�[�X�̒��́A2�̃T�u���[�`���������p�����Ē����܂����B

�@�@�@����2�����ŁAFOUT�ł������Ȋ��G�ł��B

�@�@�@dds_dataset���ƁAfreq2serial���́A2�ł��B

�@�@�@freq2serial���ŁA�����Ƃ��ēn���ꂽ��]�o�͎��g���̒l����A���ۂ�SPI�]���ő��M����

�@�@�@14LSBs�ƁA14MSBs�̎��g�����W�X�^�̒l���Z�o���Adds_dataset���̈����Fdata�ɂ��̒l��

�@�@�@�n���A�����SPI�^�C�~���O�ŁAAD9834�֑��M����`�ɂȂ�܂��B

�@�@�@���A���g�����W�X�^�փZ�b�g����l�̌v�Z���́A�}�X�^�[�N���b�N�̎��g�����A67.108864MHz�i2^26�j

�@�@�@�Ƃ��Ă��邽�ߔ��ɊȒP�Ȍv�Z�ōς݂܂��B

�@�@�@�܂�A���g�����W�X�^�l=

�i�o�͎��g���^�}�X�^�[�N���b�N�̎��g���jx2^28

= �i�o�͎��g���^2^26�jx2^28

= �o�͎��g��x4

�@�@�@�ƂȂ�܂��B

���@2014.12.20

�@�@�E�ꉞ�A�ݒ���g�����t���֕\���������̂ŁA��Վ��쐬�́A16�L�����N�^*2�s�t���p�́ALCD

�@�@�@���C�u�������g�����Ƃɂ��܂����B

�@�@�@�\�[�X�쐬�͍ςB

�@ �R���p�C���`HEX�쐬�܂ŁAOK�ɂȂ����B

���@2014.12.23

�@�@�E�����x�[�X�{�[�h�̐��삪�������������A����܂łɊ��������B

�@�@���`�F�b�N�J�n��

�@ �܂��́A���W���[�����}���œd���m�F

�@�@�@+5V���@5.22V, +3.3V���@3.24V

�@�@�@���̏�ԂŁAHEX������OK

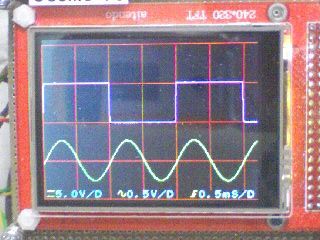

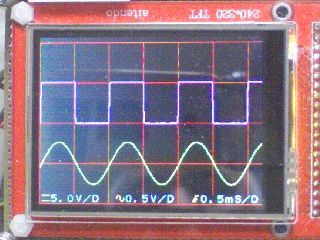

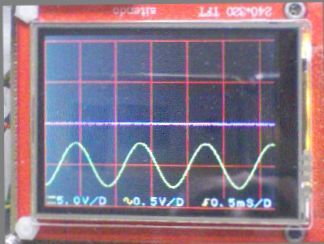

�@�@������m�F��

�@�@�@�@�@����́ADDS���ʖ�

�@�@�@�@�@ 1000Hz�ݒ�ŁA���x���́A��0.6Vp-p�����A�g�`���ʖځB

�@�@�@�@�@

���܂ɃT�C���g�ɂȂ邪����������Ȃ��B�i���߂ɂȂ�j

�@�@�@�@�@ �ʖڂȎ��́A�o�͂��o�Ȃ���������B

�@�@�@�@�@ �܂����g���ؑւ��Ă����g���ς�炸�H�H

���@2014.12.24

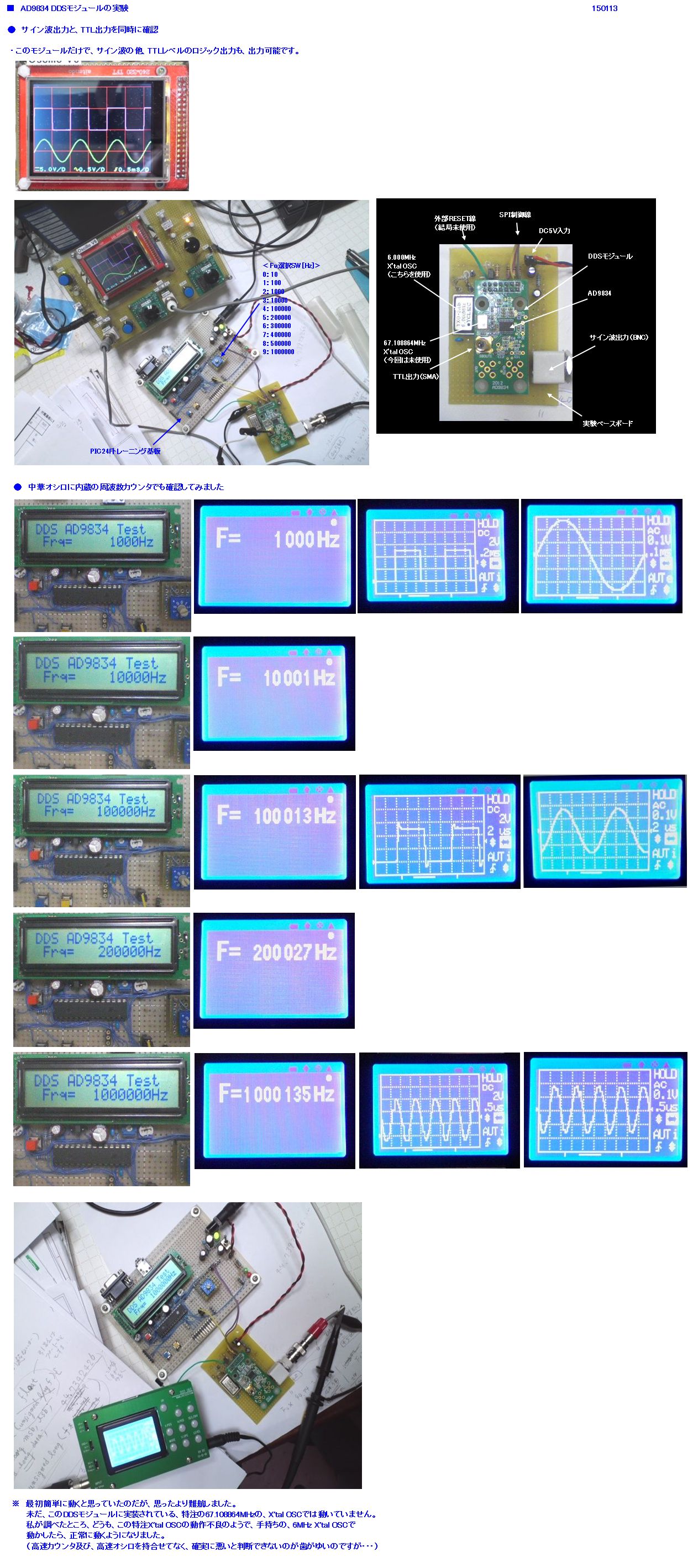

�@�@�E�q�����\�t�gSPI�̃^�C�~���O�������m�F���Ă݂��B

�@�@�@�����A�������W�A�i���������ĂȂ��̂ŁASCLK�̃X�s�[�h���ɒ[�ɒx���A��1kHz�ɂ��ă^�C�~���O����

�@�@�@�m�F�����Ă݂��B

�@�@�@���ɁA14LSBs=0x0000 +0x4000= 0x4000���ASPI�]���������̃^�C�~���O���������B

�@�@���@AD9834�́ASPI�́ASCLK�̗�����ŁA�f�[�^��Ǎ��ނ��ƂɂȂ��Ă��邪�A������������́A

�@�@�@�@

�����̃^�C�~���O�ŁA�f�[�^�r�b�g���̒������T���v������^�C�~���O�ő����Ă���悤�Ɍ�����B

�@�@�@�@ �\�[�X������ƁAFSYNC���ALo�A�N�e�B�u�ɂ�����A�����Ƀf�[�^���Z�b�g�������SCLK�𗧉����Ă���̂ŁA

�@�@�@�@ �Z�b�g�A�b�v���Ԃ�����Ȃ��\��������B

�@�@�@�@ AD9834�́A����SPI�Ȃ̂ŁA�X�y�b�N�����Ă����̃Z�b�g�A�b�v���Ԃ̋K��l�́A5nS(min)

�Ȃ̂ŁA

�@�@�@ ���Ȃ��悤�ȋC�����邪�A���I�ɂ́A�}�[�W�����グ�邽�߁ASCLK�̃p���X�����̒x�����ꂽ����

�@�@�@�@ �x�^�[�ƍl����B

�@�@�@�@ ���A���̎��A�g�������́AWEB�Ⴛ�̂܂܂ŁA�ȉ��̒ʂ�ł��B

�@�@�@�@ ���̃T�u���[�`�������̂܂g���A

�@�@�@�@ dds_dataset(0x4000, 16);

�����s���������́A�^�C�~���O�𑪒肵�����̂ł��B

�@��SPI�v���O�����၄

/***************************************************************

* serial data send (MSB first)

***************************************************************/

void dds_dataset(unsigned long data, unsigned int bt)

{

unsigned int i;

DDS_FSYNC = 0;

for(i = bt; i > 0 ; i--) {

DDS_SDATA = (data

>> (i - 1)) & 0x00000001;

DDS_SCLK = 0;

delay_us(500); // ����p�ɓ��ꂽ�i�I���W�i���̂ɂ͓����ĂȂ��j

DDS_SCLK = 1;

delay_us(500); // ����p�ɓ��ꂽ�i�I���W�i���̂ɂ͓����ĂȂ��j

}

DDS_FSYNC = 1;

}

�@�@�E�����ŁA�Z�b�g�A�b�v���Ԃ̃}�[�W�����グ�邽�߁ASCLK�̃p���X�����̒x������Ă݂����

�@�@�@�^�C�~���O�����̌��ʂ��ȉ��Ɏ����܂��B

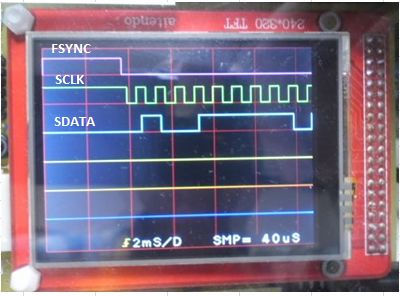

�@�@�@14MSBs=0x0FA0 +0x4000= 0x4FA0�i1000Hz�o�͑����j���ASPI�]���������̃^�C�~���O�ł��B

�@���Z�b�g�A�b�v�}�[�W�����グ��SPI�v���O�����၄

/***************************************************************

* serial data send (MSB first)

***************************************************************/

void dds_dataset(unsigned long data, unsigned int bt)

{

unsigned int i;

DDS_FSYNC = 0;

for(i = bt; i > 0 ; i--) {

�@�@�@ DDS_SDATA = (data

>> (i - 1)) & 0x00000001;

�@�@�@ delay_us(250); //

���ꂪ�Ȃ��ƁA�Z�b�g�A�b�v���Ԃɗ]�T���Ȃ��A���m�ɓǂݎ���Ă���Ȃ��\��������

DDS_SCLK = 0;

delay_us(500); // ����p�ɓ��ꂽ�i�I���W�i���̂ɂ͓����ĂȂ��j

DDS_SCLK = 1;

delay_us(250); // �f�[�^�Z�b�g���250us�x���lj������̂ŁA�N���b�N�̃f���e�B��50%�Ƃ��邽�ߕύX�@141224

}

DDS_FSYNC = 1;

}

�@�@�E�^�C�~���O�͗ǂ��悤�����A����ł������ʖځB

�@�@�@�����A1000Hz�ݒ莞�A���܂ɐ����������ŁA�T�C���g���o�͂���邱�Ƃ��m�F�����B

�@�@�@�����܂Ō��ă^�C�~���O�͗ǂ������Ȃ̂ŁA���̏Ǐ�́A��l������̂́ARESET�����Ȃ��B

�@�@�@AD9834�̃f�[�^�V�[�g������ƁA�uAD9834�̃p���[�A�b�v�v�Ƃ������ڂ��������B

�@�@�@�u�f�o�C�X�́A���Z�b�g����K�v������B�v�Ɩ��L����Ă���B

�@�@�@�\�t�g���Z�b�g���o�������Ȃ̂ŁA����Ă݂�������ł��ʖځB

�@�@�@��������e�́A�ȉ��̒ʂ�B

�@�@�@������A���C�����[�v�ɓ���O�́ASPI��3�M���̃��x���������̌�ɓ��ꂽ�B

//// ��AD9834�́A�p���[�A�b�v���@�@�@�@141224 22:40 �lj�

dds_dataset(0x0100, 16); // �������Z�b�g���A�N�e�B�u�ɂ���

dds_dataset(0x4000, 16); //

���g�����W�X�^�@14LSBs���A0�ɏ�����

dds_dataset(0x4000, 16); //

���g�����W�X�^�@14MSBs���A0�ɏ�����

dds_dataset(0x0000, 16); // �������Z�b�g����������

���@2014.12.27

�@�@�E�\�t�g���Z�b�g�����������ǂ������Ă݂邱�Ƃɂ����B

�@�@�@�f�[�^�V�[�g�ł́A���������A���g�����W�X�^�̑��A�ʑ����W�X�^�̏�����������悤�ɏ�����

�@�@�@�������̂Łi�܂��A����́A�T�C���g���o�������ňʑ��͐��䂵�Ȃ��̂ŊW�Ȃ��Ƃ͎v�����E�E�j

�@�@�@dds_dataset(0xC000,16); // �ʑ����W�X�^�̏�����

�@�@�@��lj����Ă݂��������B

���@2014.12.31

�@�@�E�\�t�g���Z�b�g�̂����ɂ́A������l������B

�@�@�@�O�L�̃��C�����[�v�̑O��1���s���p���[�I�����Z�b�g�łȂ��Afreq_to_serial�������s����

�@�@�@���ɁARESET ON���@F���W�Z�b�g�]�����@RESET OFF�����{������@�ł���B

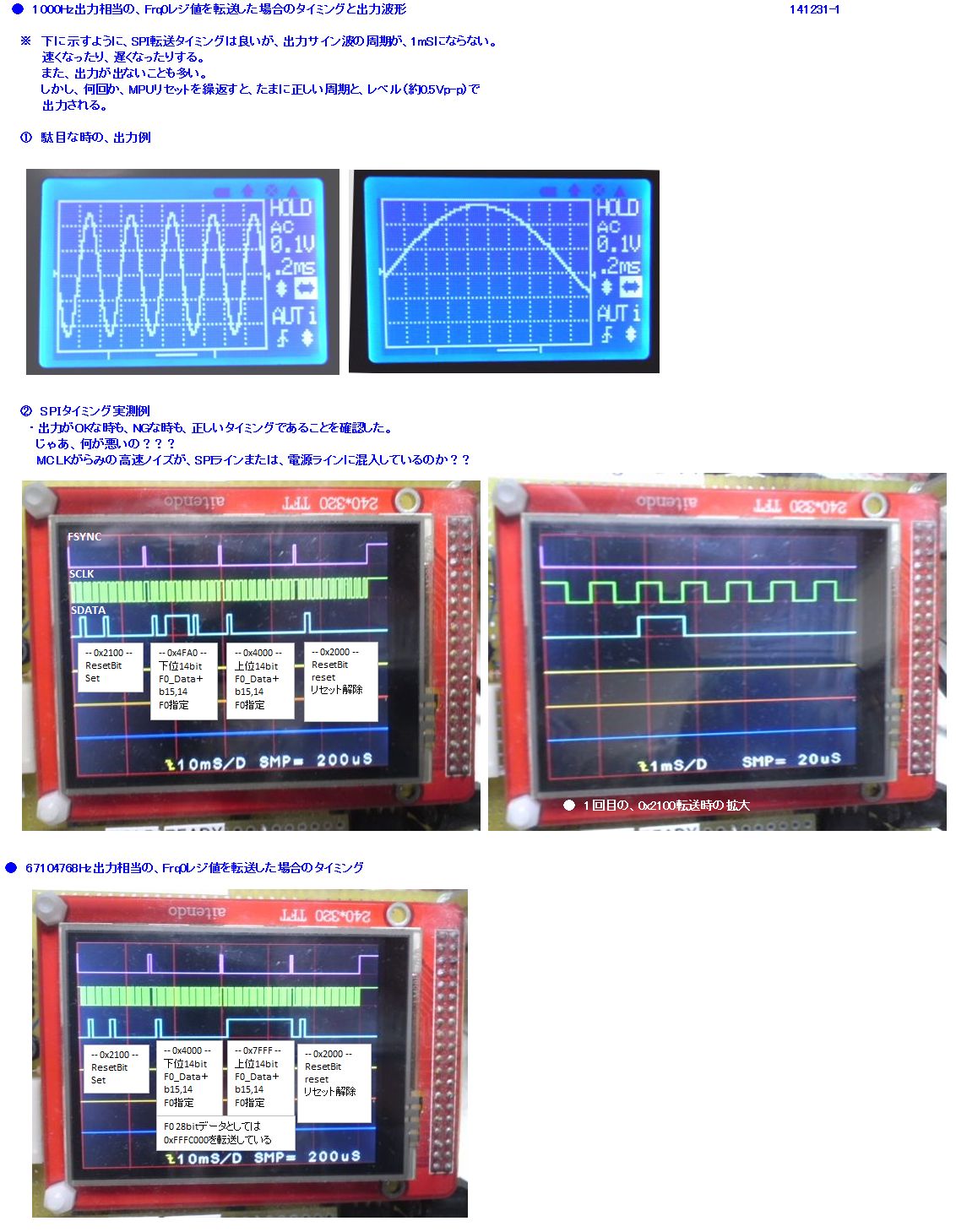

�@�@�@RESET ON�Ƃ���ɂ́A0x2100�𑗂�悢�B

�@�@�@������RESET OFF�Ƃ���ɂ́A0x2000�𑗂�悢�B

�@�@�@���̊ԂŁA�f�[�^�Z�b�g�]�����s���悢�B

�@�@�@�i�ʑ����W�X�^�̏������͍���W�Ȃ������Ȃ̂ŏȗ������B�j

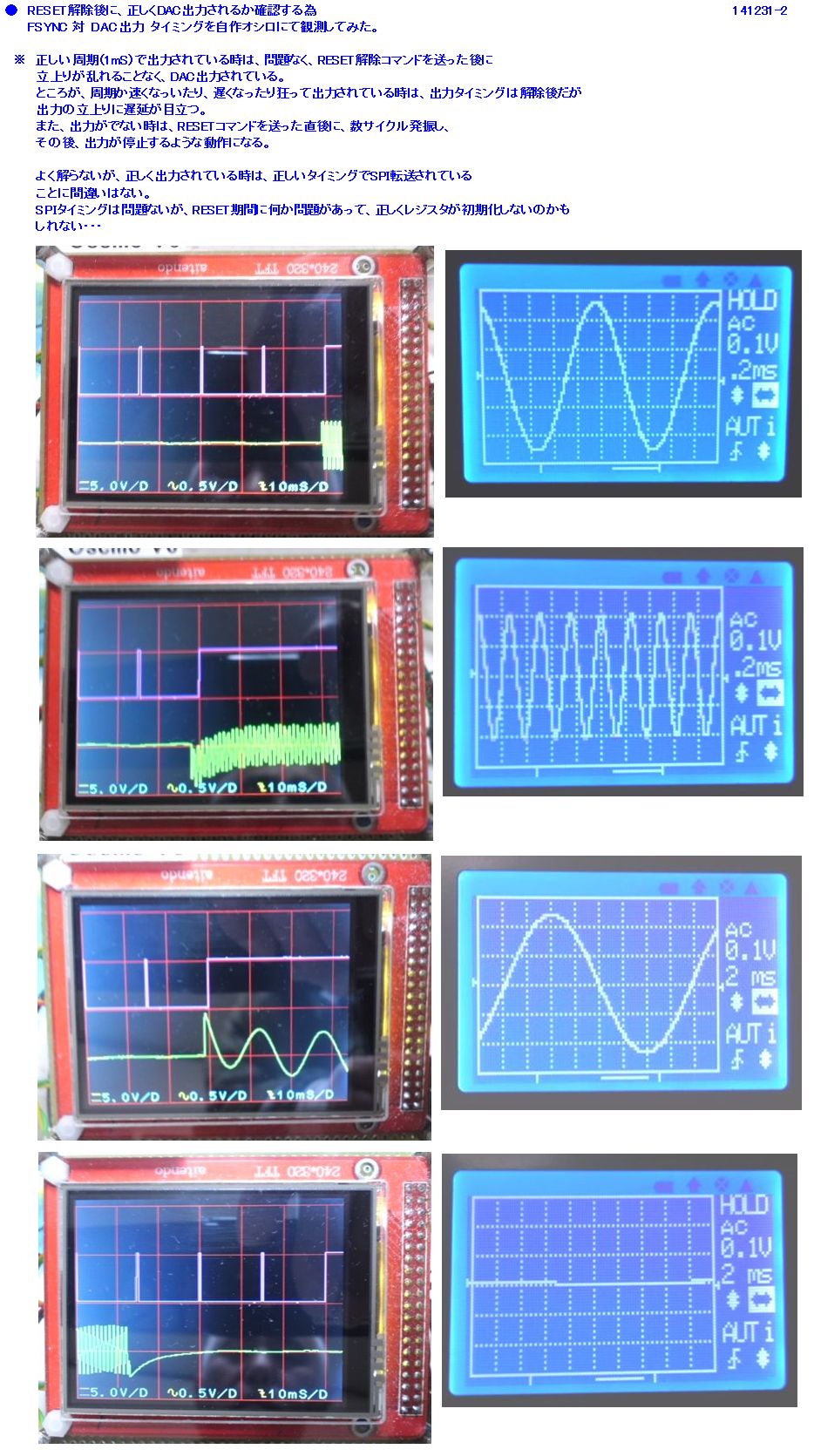

�@�@�@����ł���Ă݂����ʂ��ȉ��Ɏ������A���ʓI�ɂ͂���ł����܂��s���Ȃ������B

�@�@���@���̎��A�g�����\�[�X�́A����ł��B���@AD9834_DDS_TEST_141231.c

���@2015.1.1

�@�@�E����Ȃ��܂܁A�N�������Ă��܂����B

���@2015.1.2�`�@2015.1.4

�@�@�E���悢�����Ȃ��Ȃ��Ă����̂ŁA�ŋߕ��������A��Վ�HP�iPIC

FAN�j�́A�u�F����̌f���v�ɁA���̌�

�@�@�@�𓊍e���Ă݂邱�Ƃɂ����B

�@�@�@���̓��A���e���āA�b���́A���Ȃ������̂ł����A1��4���ɁA��Վ����珕��������܂����B

�@�@�@���̓��A4��قǂ��Ƃ���J�Ԃ��܂������A���lj��炸���܂��ł����B

�@�@�@���݁i1��14���j�A1��4���@23:09�t�̎��̓��e���Ō�ɁA���Ƃ肪�~�܂��Ă��܂��B

�@�@�@���Ƃ�̗l�q�́A�������Q�Ƃ��Ă��������B���@��Վ�HP�f�����uAD9834

DDS���W���[���ɂ��āv

�@�@�@�ȒP�ɏ����������������Ƃ��A�܂Ƃ߂�Ǝ��̂悤�ɂȂ�܂��B

�@�@�@�@�@�@DDS����5V����̂悤�ł��̂�DDS�̃N���b�N������ɔ��U���Ă��Ȃ��̂ł͂Ȃ��ł��傤���H

�@�@�@�@�A�@�C�ɂȂ�̂́APIC����3.3V��DDS����5V�ł���ˁB���������SPI�̐ڑ��̓d�����قȂ邱�Ƃ�

�@�@�@�@�@�@ �Ȃ�܂���ˁB

�@�@�@�@�@�@ ���̂�����͂ǂ����Ă��܂����H

�@�@�@�@�B�@���˂��N���Ă��邩������܂���A�M�����C����330�I�[�����x�̒�R��ɑ}������

�@�@�@�@�@�@ �_���s���O���Ă݂Ă��������B

�@�@�@�@�C�@�N���b�N�ƃf�[�^�̗����オ��A������̃^�C�~���O�͖��Ȃ��ł��傤���H

�@�@�@�@�@�@ �܂��ARESET���Ɏ��s���āA���Ƃ�����g����ݒ肵�Ă݂Ă͂ǂ��ł��傤���B

�@�@�@�@�ɂ��ẮA�����C�ɂȂ��Ă���̂ł����A�����I�V�����A�����J�E���^���������킹�ĂȂ��̂�

�@�@�@���f�̂��悤������܂���B

�@�@�@�A�ɂ��ẮA���̃y�[�W�̓��ŏ������悤�ɁAPIC24F�̃I�[�v���h���C���ݒ���g���ĊO���v���A�b�v

�@�@�@���Ă���̂Ŗ�肠��܂���B

�@�@�@�B�͎����܂������A�ʖڂł����B

�@�@�@�C�̃^�C�~���O�ɂ��ẮA������������͖��Ȃ��ƍl���Ă���B

�@�@�@RESET���ɂ�����@�͊��Ɏ��������A�ʖڂ������B

�@�@�E1��3���ɁA�A�i�f�o�̉p���̃A�v���P�[�V�����}�j���A���iAN1070�j�ɁA

�@�@�@�uAD9833/AD9834

�v���O���~���O�v�Ƒ肵�āA�v���O���~���O�̋�̓I�ȗႪ�ڂ��Ă��邱�ƂɋC���t���B

�@�@�@�����������A��{�́A�������N�̕��i12/31�j�Ɏ������A0x2100�ŁARESET

ON������@�̎菇��

�@�@�@�S���ꏏ�ł��邱�Ƃ��킩�����B��{�I�Ɏ菇�͊ԈႢ�Ȃ������悤���B

�@�@�@�����ʑ����W�X�^���A0�ɂ��鏉�����������Ă��邾���ł���B

�@�@�@�����ŁA0xC000�𑗂�̂�lj����Ă݂����A����ł��ʖڂ������B

���@2015.1.5

�@�@�E�����Ȃ�Ɩ{���ɁA�����́A67.108864MHz X'tal OSC�̕s�ǂ�������Ȃ��B

�@�@�@�����J�E���^�����̓I�V��������Έꔭ�Ŕ���̂����A���Ƃ������䂢�B

�@�@�@�ʂ̕��@�ŗǔۂ̔��f���o���Ȃ����̂��H

�@�@�@�ƍl������A�P���@������̂ɋC���t�����B

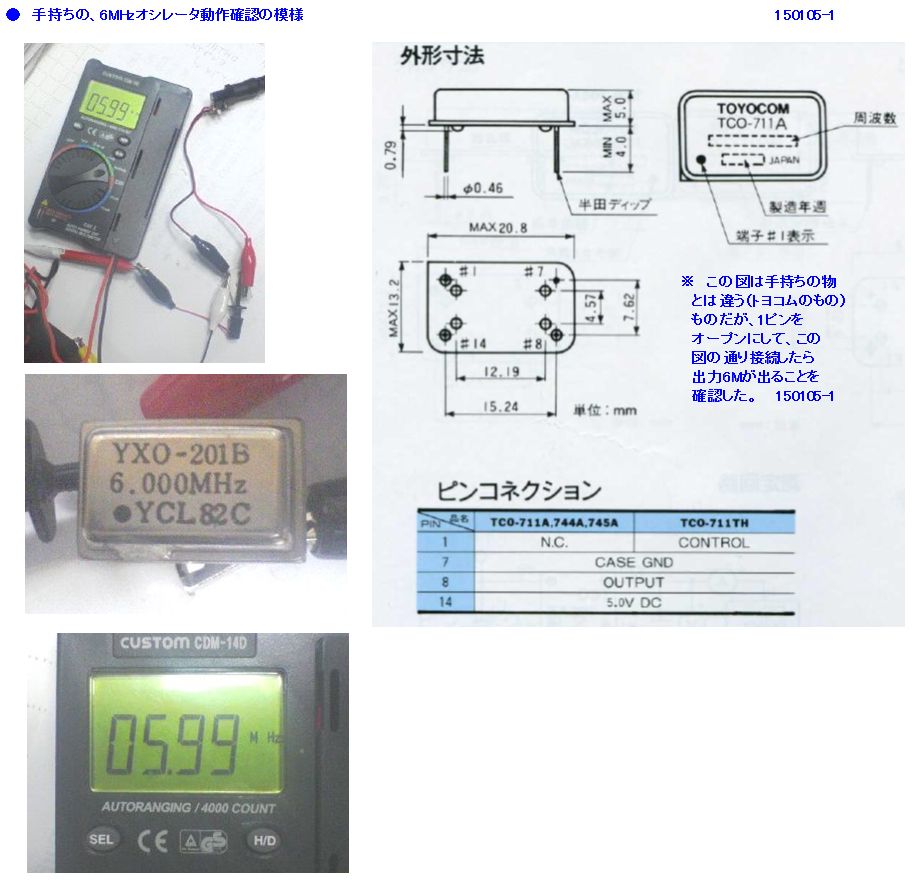

�@�@�@��̎d���Ŏg���Ă���6.000MHz�́AX'tal OSC���莝���ł���̂��v���o�����B

�@�@�@���[�h���C���������K�т��Ă��邪�ʂ����ē������ǂ����H

�@�@�@�������AWEB�������Ă�����������Ȃ������̂ŁA�s���A�T�C�������s���E�E�E

�@�@�@���Ԃ�TTL����̂��̂Ȃ̂ŁA+5V�d���Ƃ͎v�����E�E�E

�@�@�@���Ȃ݂ɁA�^�Ԃ́A�uYXO-201B 6.000MHz�v�ł��B

�@�@�@����ł��P�̂Ń`�F�b�N���Ă݂��瓮�����̂ŁA�������Ď������Ǝv���B

�@�@�@���ɁA�`�F�b�N�������̗l�q���A�b�v���܂����B

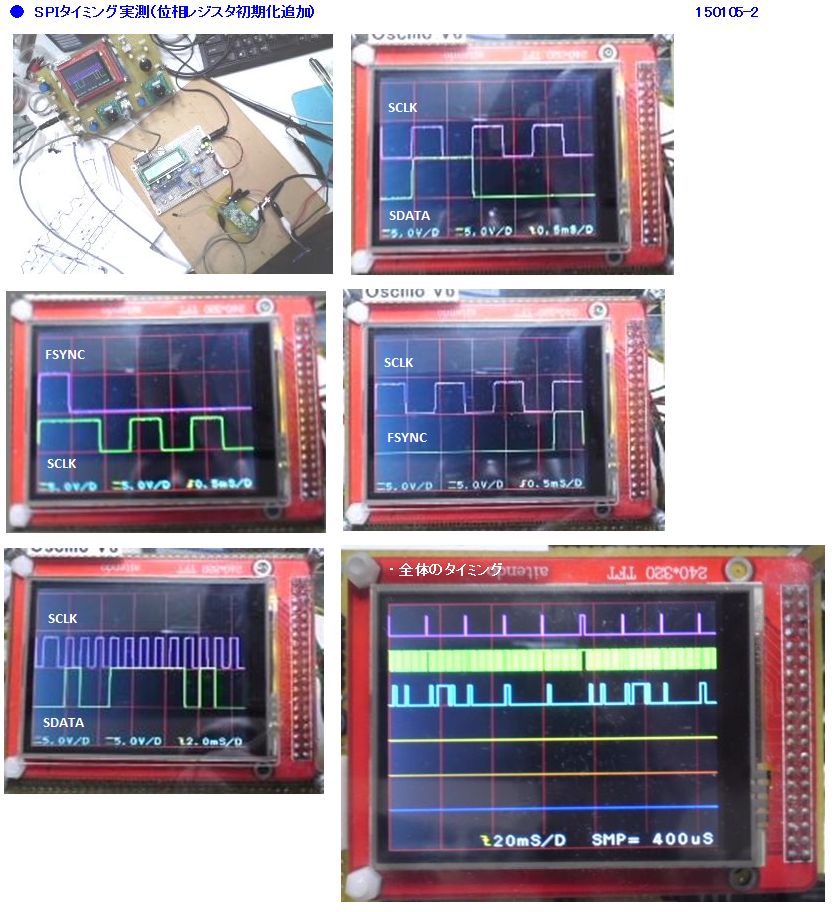

�@�@�E�������Ď����Ă݂�O�ɁA����́Afreq_to_serial���ɁA�ʑ����W�X�^��0�ɏ���������X�e�[�g�����g

�@�@�@��lj�������ԂŁi�A�i�f�o�̎菇��ƑS�������j�A�O�ׁ̈A�ēx���x�͎���I�V����

�@�@�@���W�A�i�Ń^�C�~���O���m�F���Ă݂��B

�@�@�@���ʁA��͂�^�C�~���O�͖��Ȃ������ł���B

���@2015.1.6

�@�@�E�Ƃ�����ŁA�莝����6MHzX'tal OSC�œ������Ă݂�B

�@�@�@�������邽�߂ɁA���W���[����Ɏ�������Ă���A67.108864MHz X'tal OSC���O���K�v�͂Ȃ��B

�@�@�@���W���[����ŊO���̂́AR2�F22���̃_���s���O��R�����ł悢�B

�@�@�@�܂��AX'tal OSC�́AE/D�i���^�֎~�j�s���́ACN1-14pin���AGND�ɗ��Ƃ����Ƃɂ���Ĕ��U��~

�@�@�@�ɂ��Ă����K�v������B

�@�@�@���̏�ԂŁACN1-12pin�iMCLK���́j�ɁA6MHzX'tal OSC�̏o�́i�_���s���O��R�́A�Ƃ肠����

�@�@�@�莝����20����t�����j��ڑ�����悢�B

�@�@�@�Ƃ肠�����A���g�����W�X�^�l�́A6M���ƁA1000Hz�o�͂ŁA�v�Z��44738.9�ɂȂ�̂�

�@�@�@�l�̌ܓ����āA44739�iAEC3h�j�̌Œ�l�ł���Ă݂邱�Ƃɂ����B

���@2015.1.7

�@�@�E����A���V���Ă�������������Ă݂����A�����ʖځB

�@�@�@�@�@6MHz X'tal OSC�̏o�͂��A�e�X�^�[��F�v�Ŋm�F����ƁA��ɁA5.99MHz�o�Ă���B

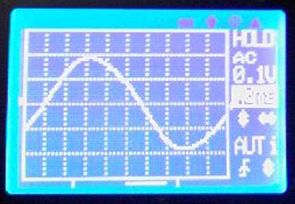

�@�@�@�A�@�ʖڂ����AFo=10Hz�ƁA100Hz�ł͐����������ŏo�͂���邱�Ƃ��m�F�����B

�@�@�@�B�@Fo=1000Hz�ł́A���̂��g�`���c�ނ��A�������������Ȃ��H

�@�@�E�܂����\�t�g�́A�������Ⴍ���āA0.2�b���ɓ����ݒ���ARESET

ON�� �ݒ聨 RESET OFF�Ƃ�������

�@�@�@�J�Ԃ��Ă���̂ŁA����̂������Ƃ��Ă͗ǂ��Ȃ��B

�@�@�@�܂��Œ�l�œ���Ă���̂��A�S�������I�ł͂Ȃ��B

�@�@�@������ŁAFSW�i���g���ؑփf�B�b�vSW�j���g���āA�ݒ��ύX�������̂݁A�ݒ���X�V���悤��

�@�@�@�v���O������ύX���ׂ��I�I�i�ŏ�������ׂ����������E�E����ł����Ȃ��Ă��܂����j

�@�@�@�v���O�����C���ŁA10, 100, 1000, 10000,

100000, 200000, 300000, 400000, 500000, 1000000Hz

�@ �̑S�ĂŁA����������OK�ɂȂ����B�ؑւ��u�Ԃɍs���Ă���B

�@�@�@�����A1000Hz�ƁA200kHz�ŁA�d�����グ���A�������������Ƃ��������B�i��RESET��́AOK�ɂȂ�j

�@�@�@�������S����Ȃ��E�E�E

�@�@�@

�@�@�@

���@2015.1.9

�@�@�E�T�C���g�o�݂͂̂͂�������OK�Ȃ̂ŁASB-OUT�i���`�g�o�́j�������B

�@�@�@SB-OUT�i�f�W�^���o�́F0-5V�j���̐ݒ�i0x2100���@0x2120�ɕύX�j

�ɂ��āAF�J�E���^�Ŋm�F���Ă݂�B

�@�@�@�@�@�@�R�}���h�F0x2120�Ƃ��āARESET���|���Ȃ���ASB-OUT�������AF���W�Z�b�g�]���{RESET�����ł́A

�@�@�@�@�@�@ �T�C���o�͂͏o�邪�A�R���p���[�^�o�́iSB-OUT�j�͏o�Ȃ��B

�@�@�@�@�A�@�X�g���x���[���i�b�N�X��HP��ɂ���悤�ɁA���ɁARESET�𐧌䂵�Ȃ��Ă��i�������Ȃ��Ă��j

�@�@�@�@�@�@ 0x2020�Ƒ�������AF���W�Z�b�g�]�������ŁASB-OUT�ɁA�T�C���g�����́A/2�����ŋ�`�g�i0-5V�j��

�@�@�@�@�@�@ �o�͂���邱�Ƃ��m�F�����B

�@�@�@�@�@

��������ł��A�o�͂��o�Ȃ�������A������������肷�邱�Ƃ�����B

�@�@�@�@�B�@���I�ɂ́A�T�C���g�����Ɠ��������ŁASB-OUT�ɏo�͂������̂ŁAbit3�FDIV2='1'�ɂ�0x2028�ɕύX�����B

�@�@�@�@�@�@

���̐ݒ�̎��́A�ŏ����o�͂ɁA�����o�Ȃ������B

�@�@�@�@�@�@ �Ƃ��낪���AMPU RESET���|�������i�����グ�����j������A����Ɋ�]�ʂ�o�͂����B

�@�@�@�@�C�@���̓������猩��ƁA��͂�d�����グ���̃��Z�b�g�́ADDS�ɂ��Ă��K�v�Ȃ悤���B

�@�@�@�@�@�@ �����ŁADDS POWER ON RESET�Ƃ��āADDS�������̂Ƃ���ɁA

�@�@�@�@�@�@ dds_dataset(0x0100,16); // RESET ON

�@�@�@�@�@�@ dds_dataset(0x0000,16); // RESET OFF��lj������B

�@�@�@�@�@�@ �������A����ł������Ǐ����B

�@�@�@�@�D�@���ƁA�ʑ��͍��䂵�Ȃ����A�ʑ����W�X�^�̏������Ƃ��āA'0'��ݒ肷��̂͂���Ă������Ƃɂ����B

�@�@�@�@�@�@ ���̂悤�ɂ��Ă��A�Ǐ�͓����������B

�@�@�@�@�E�@�܂��ARESET���g��Ȃ����@�ɖ߂��A0x2038�iSB-OUT���R���p���[�^���`�g�{�@Iout�����g�j�Ƃ��Ă݂Ă��A

�@�@�@�@�@�@

���o�͂Ƃ��o�͂͏o�Ȃ�������A�T�C���g�����o���肷��B

�����̑��̃���������

�{�������́ASPI�^�C�~���O�E�\�[�X�͈ȉ�

/**************************************************************************

* serial data send (MSB first)

* 16�r�b�g�ibt=16�Ŏw��jSPI�]��

* AD9834�́ASCLK�̗�����G�b�W�Ńf�[�^��Ǎ��ށ@�iSCLK����4MHz�j

****************************************************************************/

void dds_dataset(unsigned long data, unsigned int bt)

{

unsigned int i;

DDS_FSYNC = 0;

for(i = bt; i > 0 ; i--) {

DDS_SDATA = (data >> (i - 1)) & 0x00000001;

asm("clrwdt"); //Td=125nS(62.5nS x 2) ���̒x�������Ȃ��ƌ듮�삷��B

DDS_SCLK = 0;

asm("clrwdt"); //Td=125nS(62.5nS x 2) �N���b�N�̃f���[�e�B��50%�Ɋm�ۂ��邽�߂ɓ��ꂽ�B

DDS_SCLK = 1;

}

DDS_FSYNC = 1;

}

���@2015.1.10

�@�@�E�����A1�����ȏォ���Ă���Ă������������AX'tal OSC�̕s�ǂ炵���Ƃ���܂ł͔������̂����A

�@�@�@���`�g���ꏏ�ɏo���ݒ�ɂ���ƁA�ǂ����Ă���肭�s���Ȃ��B

�@�@�@�܂��T�C���g�݂̂̐ݒ�ł����S�ł͂Ȃ����E�E�E�i���X���������Ȃ�j

�@�@�@�����ŁA�ēx�T�C���g�݂̂̐ݒ�ɂ��āA��芮�S�ȓ����ڎw���B

�@�@�E������邱�Ƃ��Ȃ��Ȃ��Ă������A����ł��Ђ������A�F�X�������Ă�����ɁA1���������ƗL�I�I

�@�@�@ �@�@����J�E���^���A����ATT�����Ŗ������A�I�V���[�^�̃_���s���OR�̐ڑ����āA���g������

�@�@�@�@�@�@����ƁA6.000010MHz�Ɛ��x�悭�m�F�ł����B

�@�@�@

�A�@��{�I�ɂ͔��U���Ă���悤�����A�����Ƀv���[�u���q���ƁA�T�C���g�̎��g�����ς���Ă��܂�

�@�@�@�@�@�@���ۂ��m�F�����B

�@�@�@ �B�@������������A�_���s���OR=20���̒l���s�K���ŁA���˂�����������ĂȂ��̂�������Ȃ�

�@�@�@�@�@�@�Ǝv���AR=100���ɕύX���Ă݂��B

�@�@�@�@�@�@��������A���Z�b�g���J�Ԃ��Ă�����OK�ɂȂ����B

�@�@�@�@�@�@�T�C���g�݂̂̐ݒ�Ȃ�A���̃o�[�W�����ł悳�����ł���B

�@�@�@�@�@�@�܂��A���g���ؑւ����Ȃ��s���Ă���B

�@�@�E�����A6M OSC�̏o�͂̃_���s���O��R�l=100���ł��A�T�C���g�o�݂͂̂̐ݒ�ł�OK�����A

�@�@�@���`�g�����o�͐ݒ�ɂ���Ƒʖ�

���@2015.1.11

�@�@�EDDS�������̑O�ɁAMCLK�����肷��܂ł̑ҋ@���Ԃ�lj����Ă݂�B

�@�@�@CQ�o�ŎЃg���C�A���V���[�Y�ɍڂ��Ă����\�[�X�ɂ��̑ҋ@���Ԃ��L�q����Ă����̂œ���Ă݂����A

�@�@�@�ʖڂȎ��͏o�͂��łȂ�������������x���Ȃ����肷��B

�@�@�@��������͓���Ă����ׂ��ƍl����̂œ���Ă����B

�@�@�@���������Ȃ�ƁA�f�q�̃o���c�L�ŁARESET���|��ɂ����f�q�Ȃ̂��ȂƎv�������Ȃ�B

�@�@�@�T�C���g�݂̂̏o�͐ݒ�̏ꍇ�́AOK

�@�@�@���ꂪ�s���I�I

�@�@�E��������Ȃ��Ȃ��Ă������A��͂�RESET��肾�Ǝv���̂ŁA

�@�@�@�V���ɁAAD9834_PowerUp����lj����ADDS RESET��A�e���W�X�^�l���A0�ɏ������A���̌�RESET�������A

�@�@�@�A�i�f�o�Ō����uAD9834�̃p���[�A�b�v�v�����s�A���̌�A�{�Ԃ̃��W�X�^�����݂�������A���`�g�����o�͂ł��A

�@�@�@OK�ɂȂ�B

�@�@�@�܂�FSW�ݒ��ύX�����ꍇ���p���[�A�b�v���K�v�B

�@�@�@���ꂪ�Ȃ��ƍX�V���Ȃ���������B

�@�@�@�����A�R���p���[�^�o�͐ݒ�̏ꍇ�́A������肭�s���Ȃ��B

�@�@�@�R���p���[�^�o�͈ȊO�́AOK�Ȃ̂����E�E�E�E

���@2015.1.12

�@�@�ECQ�o�ŎЃg���C�A���V���[�Y��ǂ�ł�����A�R���p���[�^�o�͂ɂ��Ď��̋L�q���������B

�@�@�@�u�R���p���[�^���͂�AC�����ɂȂ��Ă��āA�J�b�g�I�t��4MHz�́A�n�C�p�X�t�B���^�ɂȂ��Ă���悤�ł��B

�@�@�@

�Ⴂ���g������͂���ƃR���p���[�^�o�͂Ƀ����_���ȐM��������Đ���ɓ��삵�܂���B

�@�@�@�E�E�E�����E�E�E

�@�@�@

���x�̍����T�C���g���~�������́A�R���p���[�^�m�C�Y�i�X�v���A�X�j�̉e�����Ȃ��悤�ɁA�R���p���[�^

�@�@�@ �͎~�߂Ă����������ǂ��B�v

�@�@�@���̋L�q�̒ʂ�A�Ⴂ���g���ł͐������R���p���[�^���삵�Ȃ��悤�Ȃ̂ŁA���̃��[�h�͎g��Ȃ�

�@�@�@���ƂƂ����B

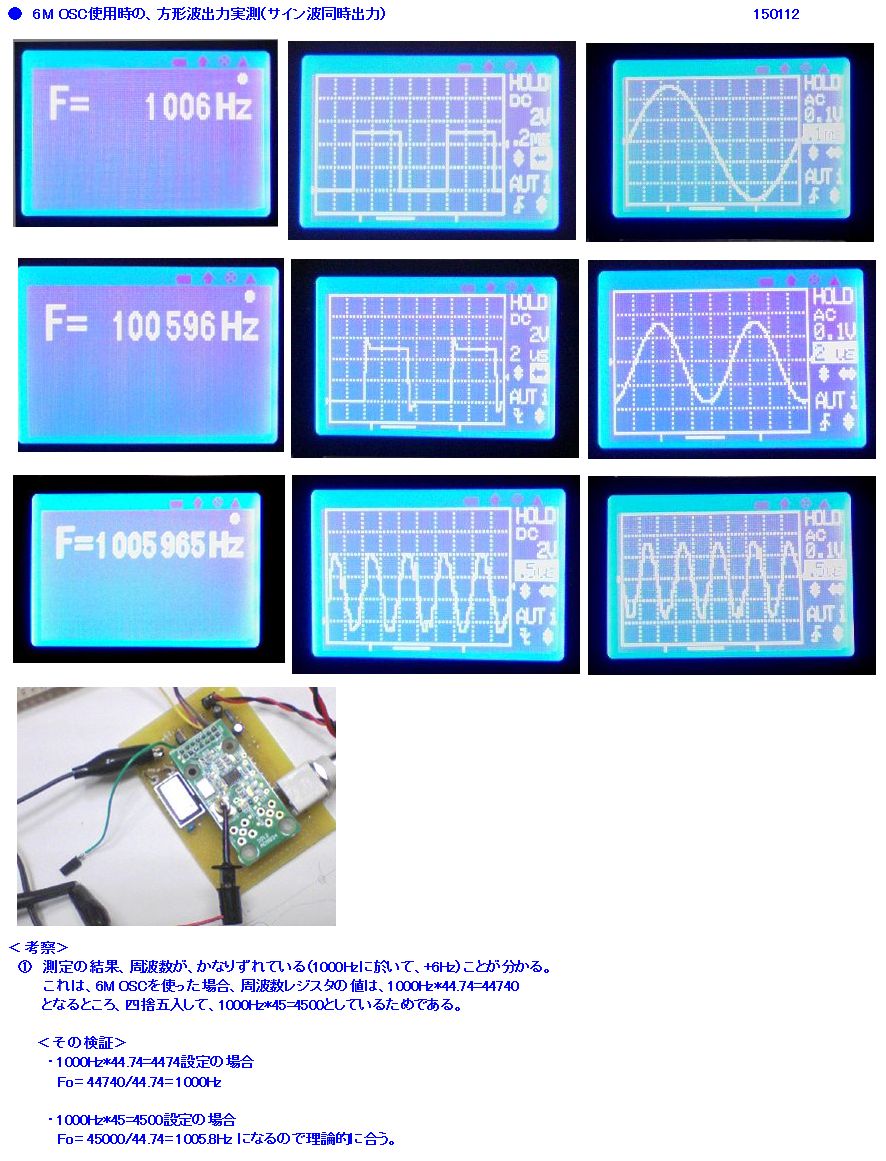

�@�@�E�����Ŋ���g�`��肵���̂ŁA�������ăA�b�v����B

�@�@�@���Ă�����̂悤�ɁA���g�����x���悭�Ȃ��B

�@�@�@1000Hz�ŁA6Hz����Ă���B

�@�@�@����́A6M�̏ꍇ�A���g�����W�X�^�l�̌v�Z���ʂ��A�����_�ȉ�������ł���B

�@�@�@���͊ȈՓI�ɁA�l�̌ܓ����Ă��邽�ߌ덷�ɂȂ�B

�@�@�@������Ƃ��������B

�@�@�@�܂��A67.108864MHz X'tal OSC�������Ă���Ζ��Ȃ��̂����E�E�E

���@2015.1.13

�@�@�E6MHz OSC�̏ꍇ�A�l�̌ܓ����Čv�Z������ƁA1000Hz�Ł{6Hz�̌덷�ƂȂ�̂�

�@�@�@data = (unsigned long)(f * 44.7392426);

�@�@�@�Ƃ��ď����_�v�Z�̌��ʂ��A32bit�����^�փL���X�g���Ă݂��B�i����f�̌^�́Afloat�ɕύX�j

�@�@�@�R���p�C���͒ʂ�A���܂��s���B

�@�@�@1000Hz�ŁA+0Hz�A10000Hz�ŁA+1Hz�̌덷

�@�@�@1000000Hz�ŁA+136Hz�̌덷�ɗ��܂����B�i��0.01%= 100ppm�̌덷�j

�@�@�@���̐������Â��āA�d�l�s���ŁA���g������x�̒�i������Ȃ����A�^�Ԃ��猩��ƁAYXO-***

�@�@�@�ƂȂ��Ă���̂ŁA���x�⏞�iTCXO�j����ĂȂ��^�C�v�Ǝv����B

�@�@�@TCXO�Ȃ�A1ppm�̈���x�����邪�A���̃^�C�v���ƁA��100ppm�قǂƎv����B

�@�@�@�����l����A���\�͏o�Ă���悤�ł���B

�@�@�@�i�����܂ł��A���̍l���ł��B�j

�@�@�E���g�����x���ǂ��Ȃ����̂ŁA6M�łƂ��āA�����܂ł�HP���J���邱�Ƃɂ����B

�@�@�@���ʂ̎ʐ^�́A���̃y�[�W�̖`�����Q�Ƃ��Ă��������B

���@2015.2.18 �����ɂ����܂������A�ǎ������܂����B�i2015/2/23�X�V�j

�@���ǎ�1�F_Fcy�_�E���{�v���A�b�v�폜�Ŏ�����

�@�@�E2015.2.17�̒i�K�ŁA�����e�[�}64�ɂāAPIC18F14K50�i5V�n�j�ł́A

�@�@�@�����́A67.108864MHz OSC�ŁAAD9834 DDS���W���[���𐳂������������Ƃ��o�����B

�@�@�@PIC24F�Ƃ̈Ⴂ�͈ȉ��ł���B

�@�@�@�@�@�@�d�����A3.3V

�@�@�@�@�A�@SPI���C�����{5V�Ńv���A�b�v���Ă���B

�@�@�@�@�B�@Fcy�������i4M�ɑ��A16M�j

�@

�E�����ŁA�\���͏��Ȃ��Ǝv�����A�܂��B�ɂ��āAFcy���A16M����A4MHz�ɂ��Ă݂��B

�@�@�@����́AConfig2�ł̃N���b�N�ݒ�i����8MHz�{x4PLL=32MHz�j�́A���̂܂܂ŁA

�@�@�@�|�X�g������̐ݒ���A1/1����A1/4�ɕς��邾����OK�B

�@�@���@����Ă݂����A�S���Ǐ�ς�炸�B

�@ �E�c��Ⴂ�́A�A�����Ȃ��̂ŁA���������Ă݂��B10k�Ńv���A�b�v���Ă��邪�A���̐ڑ���ؒf���āA

�@�@���ɁA�s���\�P�b�g�́ASPI���s���ɁAPIC24F�|�[�g����̐M������ڑ��C�������B

�@�@�@���YSPI�|�[�g�́A�I�[�v���h���C���ݒ����߂��B

�@�@���@���Ƃ���ŏ�肭�s�����I�I

�@�@�@�@ �������A���`�g�����o�͂ł��I�I

�@�@�@�@ SPI�^�C�~���O�L�q�Ɉ�̒x���v�f�����ĂȂ��A�v���O�����̃X�s�[�h�ł��A���W�b�N���x���̐�����

�@�@�@�@ ���Ȃ��悤�ŁA�����Ă���B

�@�@�@�@

���I��Ԃł̃��x���́A�����I�V���������̂Ŋm�F���悤���Ȃ���

�@�@�@�@ �ÓI�ȏ�Ԃł́A����Hi= 3.23V, Lo=0V ��

�@�@�@�@ AD9834�́ASPI���̓��x���K�i�́AVih(min)= 2.8V�iVdd=4.5�`5.5V���j�AVil(max)=

0.8V�iVdd=4.5�`5.5V���j

�@�@�@�@ �ł���̂ŁA�����͎��邱�ƂɂȂ�B

�@�@�@�@ �܂��APIC24F�̏o�̓s���d�l�́A�W���Ō���ƁAVoh(typ)=

2.6V�i�W���ŁAVdd-0.7�j�AVol(typ)= 0.4V�Ȃ̂ŁA

�@�@�@�@ Lo���x����OK�����AHi���x���́AHi�Ƃ��ĔF������Ȃ����ƂɂȂ邪�A

�@�@�@�@ �����ł́A3.23V����̂ŃM���M���Z�[�t�̂悤���B

���@2015.2.19

�@���ǎ�2 �v���A�b�v��R�̒l��ύX���Ď�����

�@�@�E���́A10k�������A���ꂾ�ƑʖځA����菬�����l�ɂ���B

�@�@�@�莝���̒�R���A2.2k�ƁA1k�Ŏ������B

�@�@�@PIC24F�́AVoh�́C�W���ŁA2.6V�Ȃ̂ŁAPIC�f�q�̃o���c�L�ŁA���̒l�Ɏ��܂��Ă���ƁAAD9834�́A

�@�@�@Vih=2.8Vmin �Ȃ̂ŁAHi�Ƃ��ĔF�����Ȃ��\��������B

�@�@�@�Ȃ̂ŁAO.D�ݒ�{�O���v���A�b�v��͂��Ă����������x�^�[�ł���B

�@�@�@�����ʁ�

�@�@�@�@�E2.2K�ŁASCLK�̒x���}�������̃t���X�s�[�h���ƁA���P�͂���邪���XNG�ɂȂ�B

�@�@�@�@�@F�ؑ֎��ɂ��������Ȃ邱�Ƃ������B

�@�@�@�@�@2.2k�ŁASCLK�̂Ƃ���̒x���}�������āA��4MHz�ɗ��Ƃ��ƁA����ɗǂ��Ȃ邪�A����ł�100%

OK�ɂȂȂ�Ȃ��B

�@�@�@�@���@���ǁA1k���ɂ��āASCLK��4MHz�ŁA100%

OK�ɂȂ����B

�@�@�@�@�����I�V�����������킹�ĂȂ��̂ŁA���Ƃ������܂��A

�@�@�@�@O.D�i�I�[�v���h���C���j�ݒ�̏ꍇ�A��v���A�b�v�i10k���j�ł́ASCLK���̗���莞�Ԃ��\�������o���Ȃ�

�@�@�@�@�悤�ŁASPI���듮�삵�Ă������̂Ɛ������܂��B

���@�ȉ��́A150223�X�V�Łi67.108864MHz OSC�œ������o�[�W�����j�̉�H�}�ƃ\�[�X�ł��B

���ŏI��H�}��

�@�E�����炩��A�ǂ������@�uAD9834 DDS���W���[��������H�v

�@���ŏI�\�[�X��

�@�E�����炩��A�ǂ������@�@DDS_AD9834_Test2.c

-------------------------------------------------------------------------------------------------------------------------------------------------

���@�ȉ��́A�X�V�O�́A67.108864MHz�ł͓������A6MHz�œ��������o�[�W�����̉�H�}�ƃ\�[�X�ł��B

�@�@ �Q�l���x�Ɍ��Ē�����Ǝv���܂��B

���ŏI��H�}��

�@�E�����炩��A�ǂ������@�uAD9834 DDS���W���[��������H�v

�@�@�@�@�@�@�@�@�@�@�@�@�@�@�@�uAD9834

���^DDS���W���[����H�v

���ŏI�\�[�X��

�@�E�����炩��A�ǂ������@�@DDS_AD9834_Test.c

���@�����e�[�}1�ɖ߂��@�@�@TOP PAGE�ɖ߂��@�@�@�����e�[�}64�ց@��

�@

�@