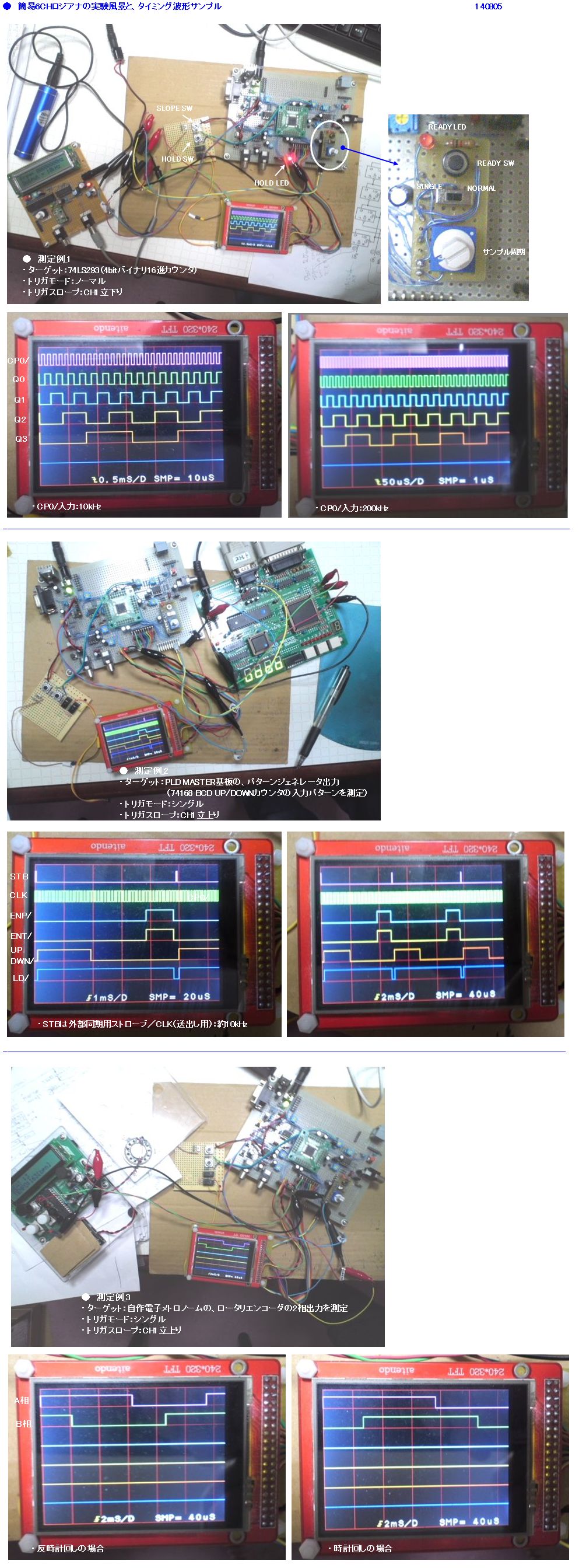

● 実験テーマ55

「PIC32MX_簡易6CHロジアナの実験」

(2CH追加して6CHとしました。ソフトを、さらに改善し、シングルトリガモードを追加しました。その実験の顛末記です。)

以下より、顛末記です。

■ 2014.7.25

・横置き表示のままでも、少し上の方へ各CHの表示位置をずらせば、何とか6CHまでなら

表示できそうなので、6CH化の実験をしてみることにした。

これからの予定であるが、暫くは、PIC32MXトレーニング基板を使っての実験をしてみたい。

作業を細分化して考えてみた。

<作業その1>

現在の仕様のまま、6CH化する。

<作業その2>

今のに、シングルトリガモードを追加する。

今回の簡易ロジアナは、多CHのロジック・スコープの位置付けでよい。ロングメモリは省略。

<作業その3>

作業その2の実験結果を受け、使える形にする。(本番)

基板化(今回は、たぶんユニバーサル基板になる予定)+ ケーシング

■ 2014.7.26

・初めから、<作業その2>までを想定して、回路図を作成した。

幸い、6CH化に当たっては、5Vトレラント仕様の入力ピンが、RF0〜

RF5まで連続していたので

この部分のソフト作成は楽になりそう。

(今迄の、4CHの時は、PIC32MX(TQFP64パッケージ)のピン配列の関係から、隣通し並んでいる

4つのピンが目に留まり、RF2〜 RF4を、CH1〜4に割り当てたのだが、(RF0,1はこれらから離れた

辺にピンが配置されている)この時から、RF0〜3に、CH1〜 4を割り当てるべきだったと反省している)

また、NORMAL/SINGLEの切替SW, READY SW等は、今迄の、ロータリーディップSW治具基板に

追加する形にした。(とりあえずは、治具改造はしないで、作業を進めた)

・ソフトの方は、まずは、シングルトリガ抜きということで、座標表示位置・波形表示位置の変更と、

6CH分の読込部分の修正が主な部分なので、楽であった。

■ 2014.7.28

・プロジェクトを組み、コンパイル〜HEX焼きまでOK。

→ まず駄目。CH1入力しても、初期メッセージ表示で止まったままになっている。

<調査〜対処>

① CH1(RF0ピン)に、パルスは入力されている。

② RF0ピン単体のチェックを行ったが、入力ピンとして動いていることを確認。

(RF0ピンの状態を、読込み、それをHOLD LEDに出力して確認した。)

③ パルジェネからの10kHzパルス入力が、RF0ピンに入力されているか、自作オシロにて確認

してみたが、問題なく入力されている。

④ これでも、何故か、T3割込みに入ってこない?

T3初期設定後までは、RUNしている。

ところが、そこから、メイン頭の、while(1);の手前までは、RUNしてない?

その間で、暴走?しているように見える。

結局これは、SWを押してないのに関わらず、CN割込みを許可した直後に、

状態変化割込み(CN割込み)が発生していて、暴走しているように見えただけであった。

よくよく考えると、RTOSで、PIC32MX MP3プレーヤを作った時も、同じようなことがあったことを思い

だした。もう既に忘れてしまっていたのだ。

これを回避するためには、CN割込み許可前に、読込SWポートの状態合わせが必要なのだ。

具体的には、当該ポートの状態をダミー入力(適当な変数名のテンポラリに入力)することで、

内部状態と、外部状態を一致さればよい。(これを状態合わせと称している。)

これを実行することで、割込み要因をリセットすることが出来る。

(後閑さんの著書「PIC32MX活用ガイドブック」の中に書いてあった。)

尚、この前の簡易4CHロジアナでは、この記述がなくても問題なく動いていた。その時はREADY

SW

を追加する前で、たまたま状態合わせをしなくてもよい状態になっていたものと推測する。

※ このダミー入力での状態合わせを追加したら、動作OKになった。

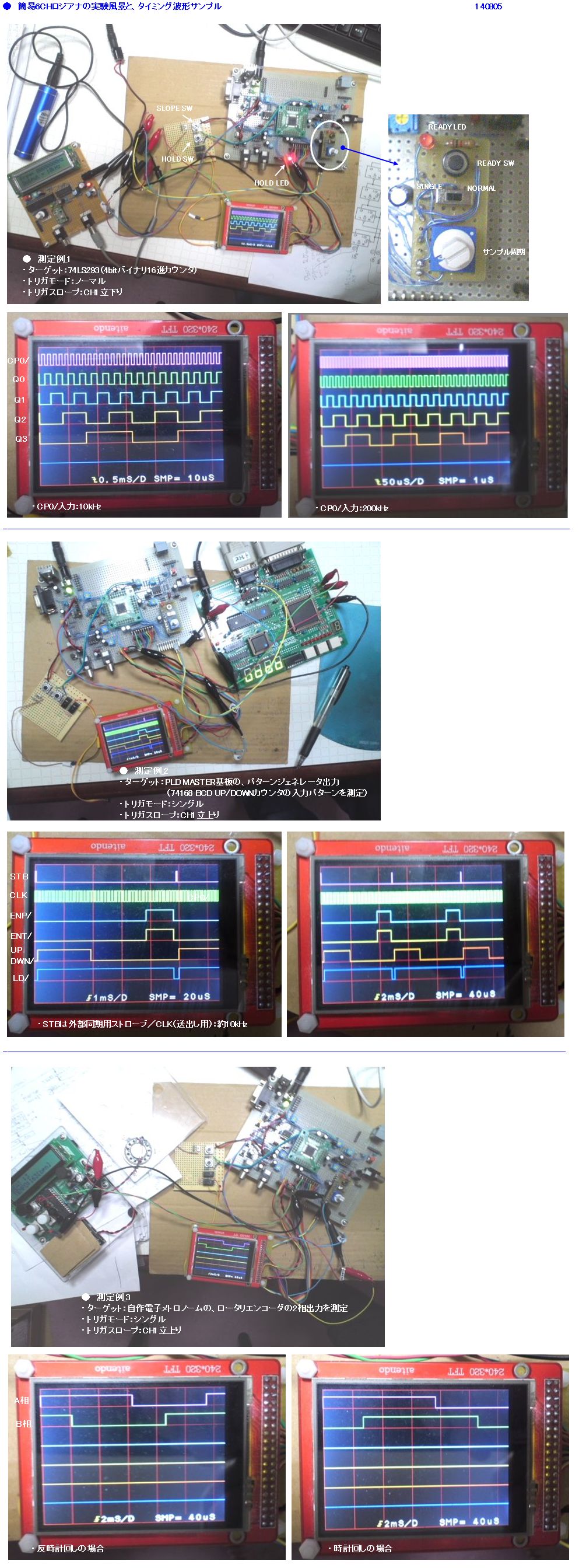

・74LS293での、5CH入力(6CHは、GND入力)で、100kHzクロックまで十分使えることを確認した。

また、表示バランスも良さそうである。

■ 2014.7.29

・作業その1は、よさそうなので、今日から、作業その2:シングルトリガモードの追加実験

を開始することにした。

ロータリディップスイッチ治具基板上に、NORMAL/SINGLE

SWと、READY SW+LEDを追加する

改造と、ソース作成を行った。

ソースは、大方、自作オシロの仕様に準ずる形で進めていきたいと考えている。

■ 2014.7.30

・昨日中に治具改造と、ソース作成は終了した。

コンパイル〜HEX焼きまでOK。

<動作確認と調査>

・NORMALモードは、今迄通りの動きでOKだが、SINGLEモードに切替えた時の動作が

うまく同期してないかのような動きをする。

例えば、画面表示が崩れたりする?

・この画面表示の乱れ現象は、具体的には次のようになる。

CH1入力しっぱなしで、NORMALから、SINGLEに切替えて1回目の、READY

SW ONでは、

READY LEDが点灯しなかったり、

READY LED 点灯はしても、その後、本来は、CH1入力が入っているので、直ぐにエッジ検知し、

READY LEDが、消灯するはずが、消灯せず画面は、全クリア後、座標表示して、その後

おかしくなっている。(全クリアのままだったり、波形表示が中途までしか表示しなかったりと乱れる)

そして、2回目の、READY SW ONでようやく、トリガ検知され、READY

LED が消灯し、

波形は表示されるようになる。

このような、暴走しているような動きをする。

■ 2014.8.1

・うまく行かない理由を、気になっている点を含めて考えてみた。

→ 自作オシロとの大きな違いは、バッファリングである。

自作オシロの場合は、とにかくバッファフルになるまで無条件で格納し、後で、その内容から

トリガ検知を行っているが、現状考えた簡易ロジアナは、トリガ検知をした時点から、

バッファリングを開始し、バッファフルになるまで格納している点である。

→ 後、現状の簡易ロジアナで気になっている点がある。

これを含めて、プログラム上修正が必要な点を考えてみた。

① NORMALでも、SINGLEの場合でも、トリガが検出されない場合、常にメインはループして

いる必要がある。

さもないと、SW類のリードが常に出来なくなる。

しかし現状では、トリガが検知されない場合は、T3割込みと、メインの、EndFlagセット待ち

の間で、検知するまで繰り返すループに入ってしまうので、メイン頭に戻れなくなっている。

つまり、信号が入力されない限りメインループしないようになっている。

まあ、NORMALだけなら、それでも実験レベルとしては許せるのだが・・・

信号を断つと、SW類を読込めなくなるのは、まずいので、これは修正することにする。

バッファリングと、エッジ検知の方法を、自作オシロと同じに修正することにした。

② トリガが検出されるまでは、液晶画面上に、「Waiting

for trigger」メッセージを

表示させた方が、スマートなので修正する。

■ 2014.8.2

・昨日の考えでソフトを修正し、動作確認を行った。

NORMALは、OKだが、SINGLEは、ソフト修正前と同じ症状である。

暴走しているかのような動きに変わりはない。

ソースを追ったが、今のところ、お手上げ状態・・・

自作オシロと同じ書き方をしているのだが、ロジアナのシングルが上手く行かない。

なんとなく、こういう動きをしている時は、割込みがらみのことが多い気がしているが・・・

■ 2014.8.4

・動きが暴走ぽいので、何となく気がめいってくるが、ソースから整理して作成した、フローチャートを眺めて

いたら、一点、原因らしきところに気が付いた!!

どうも、治具で使っている、READY SWの押して離した時、発生するチャッターによって、READY

SW ON

待ちループを抜けた後の、画面クリア当たりのタイミングでもう一度、CN割込みが入ってしまう為、

クリア画面が途中でおかしくなっている可能性がある。

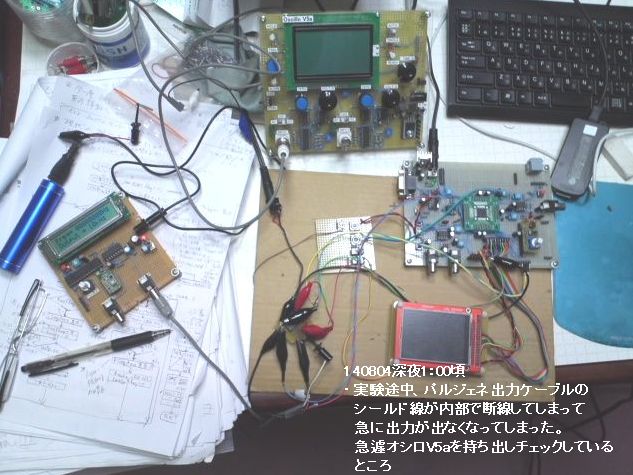

これに気が付いたのは、深夜1時30分頃のこと。

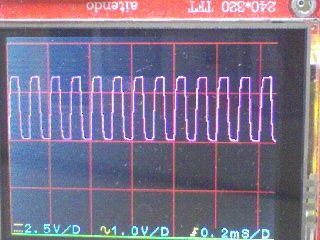

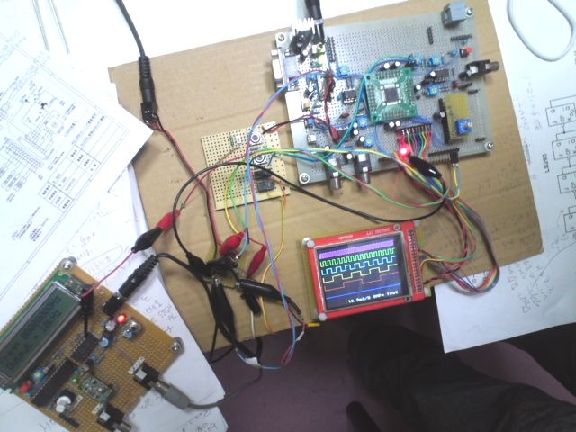

作業の途中でパルジェネ出力に使っているシールドケーブルの、シールドが内部で断線したらしく、

急遽それを確かめるために、自作オシロV5aを持ち出す場面もあり・・・(下にその時の様子をアップしました)

早速、眠気を抑えながら、READY SW ON待ちルーチンに入る前で、CN割込みを許可し、ONされて

このルーチンを抜けたら、CN割込み禁止するようにソースを修正してみた。

ちょっと見た所では、暴走のような動作は止まったように見えた。

もう深夜で眠いので、ここで就寝!!

・朝になって、深夜のことを再確認したところ、信号入力しておいて、NORMALからSINGLEに切替え

READY SWを押すと、最初の内は、トリガ検知して、波形描画をして、再びREADY

SW ON待ちになる

ということを繰返すが、READY SWを早く何度もひつっこく押していると、CN割込みに入ってこなくなる

のか、動作がおかしくなることが判明。

未だ解決してないではないか・・・

CN割込みに関するソフト記述に何か問題があるのかな?

そういえば、以前PIC32MXを使って、RTOSで、ソフト作成した、MP3プレーヤのソースにも

同じような、CN割込みの記述があったような・・・

早速、ソースを見てみたら、CN割込みの初期設定のところで必要な、スイッチの状態合わせが、

CN割込みの中でも記述されているではないか!!

何故これに早く気が付かなかったのだろうか?

さらに、CN割込みの中でやる、状態合わせのタイミングは、CN割込みに入った頭でやっている

各SWの押されたか?のチェックの後、直ぐではなく、押されている状態から離すまでの間に発生する

チャッタを回避する数mSのウエイトの後、行っている。

これで謎が解けた。

このように修正したら、今迄の動きが嘘のように、快適に動き出した。

デバッグ期間が長かったせいで、ソースも、だいぶ汚くなっていたので、ここで一度、整備

(コメントアウトしているデバッグ行削除等)し、念のため最終確認を行った。

問題ないようなので、シングルトリガでのサンプル取りを行った。

ターゲットとして、自作電子メトロノームの、ロータリーエンコーダの、2相出力を観測してみた。

このページトップの表紙の写真を参照してください。

(写真の日付は、140805となっていますが、ロータリーエンコーダの、2相出力は、8/4に撮影し

他の、74LS293の、5信号と、PLD MASTER基板の、6信号は、8/5に撮影しました。)

これで、その1と、その2の実験が終わったので、HP公開しようと思います。

<最終回路図>

・こちらから、どうぞ→ 「PIC32MX_簡易6CHロジアナ実験 回路図」

<最終ソース>

・こちらから、どうぞ→ Easy_6CH_LogAna_TEST.c

(この他に、カラーQVGA液晶用のライブラリソースとヘッダーファイル+フォントデータファイルが必要ですが、これらは、実験テーマ53のものと同様です。)

← 実験テーマ1に戻る TOP PAGEに戻る 実験テーマ56へ →