仠丂幚尡僥乕儅53

乽PIC32MX_娙堈4CH儘僕傾僫偺幚尡乿

乮慜偐傜傗偭偰傒偨偐偭偨儘僕傾僫偺幚尡傪丄PIC32MX僩儗乕僯儞僌婎斅偱傗偭偰傒傑偟偨丅乯

仭丂2014.7.3

丂丂丒僆僔儘_V6傕丄HP岞奐傑偱嵪傫偩丅

丂丂丂師婜僥乕儅53傪壗偵偡傞偐丠丂岓曗傪楍婰偡傞偲師偺傛偆側傕偺偑峫偊傜傟傞偑丒丒丒

丂丂丂亙岓曗亜

丂丂丂丂嘆丂娙堈儘僕傾僫

丂丂丂丂嘇丂WAV僾儗乕儎

丂丂丂丂嘊丂崅懍ADC傪巊偭偨丄僆僔儘_V7

丂丂丂丂嘋丂僷儚僄儗娭學乮D媺傾儞僾懠乯

丂丂丂丂嘍丂MP3僾儗乕儎偺僜僼僩VUP乮楢懕嬋憲傝偺捛壛乯

丂丂丒娙堈儘僕傾僫傪傗傞偲偟偰丄儘僕傾僫偲僆僔儘偱偼壗偑堘偆丠

丂丂丂丂嘆丂傑偢丄ADC偼晄梫

丂丂丂丂嘇丂僨僕僞儖偺傒偱僴乕僪偼傛偄偼偢丅乮2抣偺傒埖偆乯

丂丂丂丂嘊丂偮傑傝擖椡偺丄Hi, Low儗儀儖偺敾暿偼丄'0'偐丄'1'偐偺1bit偱帠懌傝傞丅

丂丂丂丂丂丂 侾僶僀僩偺儊儌儕傪梡堄偡傟偽丄8CH暘偺丄儗儀儖敾暿偑偱偒傞丅

丂丂丒偳偆偄偆偺傪嶌傞偺丠

丂丂丂丂嘆丂幚嵺丄幚尡婡偲偟偰嶌傞帪偼丄4CH擖椡偱傛偄偲巚偆丅

丂丂丂丂嘇丂PC傪棙梡偡傞曽朄偼媝壓丅僗僞儞僪傾儘儞偵偡傞丅乮僇儔乕QVGA塼徎昞帵乯

丂丂丂丂嘊丂WEB偵偼丄奜晅RAM傪巊偭偨椺偑懡偄偑丒丒丒乮梫専摙乯

仭丂2014.7.4

丂丂丒偟偐偟丄儘僕傾僫傪傗傞偺偼弶傔偰偩偟丄晘嫃偑崅偄婥傕偡傞丅

丂丂丒傕偆堦偮偺埬偼丄乽3CH僆僔儘偺幚尡乿偑峫偊傜傟傞丅

丂丂丂婛偵丄TRIG CH娷傔偰丄4CH摨帪僒儞僾儖偺妋擣偑弌棃偰偄傞偺偱恑傔傗偡偄丅

丂丂丂偨偩丄偁偲1CH丄摨偠傾僫儘僌傾儞僾偑昁梫側偺偱柺搢側偺偑僱僢僋偵側偭偰偄傞丅

丂丂丒柪偭偰偰傕偟傚偆偑側偄偺偱丄堦墳丄乽娙堈儘僕傾僫幚尡乿偺曽岦偱恑傔傞偙偲偵偟偨丅

丂丂丂偞偭偲峔惉埬傪峫偊偰傒偨丅

丂丂丂亙峔惉埬亜

丂丂丂丂嘆丂CH悢丗丂4乣 8CH

丂丂丂丂嘇丂僒儞僾儕儞僌廃婜丗丂悢100u乣丂1uS傑偱偺娫偱丄悢揰DSW偱慖戰壜

丂丂丂丂嘊丂昞帵丗丂2.8僀儞僠丒僇儔乕QVGA塼徎乮320x 240dot乯墶抲偒昞帵

丂丂丂丂嘋丂PIC丗丂PIC24H偐丄PIC32MX

丂丂丂丂丂丂丂丂丂丂乮幚尡傪僩儗乕僯儞僌婎斅偱傗傞偺偼丄PIC32MX偺曽偑巊偄堈偄丅乯

丂丂丂丂嘍丂懠僴乕僪峔惉丗僩儕僈亄傾僪儗僗僇僂儞僞亄SRAM

WEB偱偼丄偙傟傜傪慡偰僴乕僪儘僕僢僋乮昗弨儘僕僢僋IC偲偐丄CPLD,

FPGA乯

丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂偱峔惉偟偰偄傞椺傕懡悢尒傜傟傞偑丄偙偙偼娙扨側峔惉傪栚巜偟偨偄偺偱丄

丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂 PIC撪偺僴乕僪傪巊偄丄慡偰偼丄僜僼僩偱僐儞僩儘乕儖偱偒偨傜偲巚偭偰偄傞丅

仭丂2014.7.7

丂丂丒崱擔偼丄偞偭偲偱偼偁傞偑丄幚尡僾儘僌儔儉偺1曈傪峫偊偰傒偨丅

丂丂丂嬌僔儞僾儖側忦審偱幚尡偟偰傒傞丅

丂丂丂T1妱崬傒乮僒儞僾儖廃婜乯娭悢偺拞偱埲壓傪幚峴丅

丂丂丂丂嘆丂僩儕僈丒僜乕僗偼丄CH1偺傒偲偡傞丅

丂丂丂丂丂丂

傑偢擖椡僷儖僗偺僄僢僕丒僙儞僗傪峴偆丅乮嵟弶偼丄棫忋傝偺傒偱傛偄偩傠偆丅乯

丂丂丂丂嘇丂擖椡僨乕僞乮4CH暘乯傪儊儌儕乮SRAM乯偵彂崬傓丅

丂丂丂丂嘊丂SRAM傾僪儗僗傪丄1偮恑傔傞丅

丂丂丂丂嘋丂傾僪儗僗亖丂FULL偵側偭偨偐敾抐偟丄FULL偱側偗傟偽丄嘇偵栠偭偰孞曉偡丅

丂丂丂丂嘍丂FULL偱偁傟偽丄彂崬傒傪廔椆偝偣傞丅

丂丂丂丂嘐丂僨乕僞廂廤偑廔椆偟偨傜丄EndFlag傪僙僢僩偡傞丅乮妱崬傒張棟偼婎杮偙偙傑偱乯

丂丂丂丂嘑丂儊僀儞偱丄EndFlag傪妋擣偟丄僙僢僩偝傟偰偄偨傜QVGA偵儊儌儕偺撪梕偐傜

丂丂丂丂丂丂 敾抐偟偨儘僕僢僋忬懺乮Hi or Lo or 棫忋傝 or

棫壓傝乯傪塼徎偵丄

丂丂丂丂丂丂 1夋柺暘昞帵偡傞丅

丂丂丂丂嘒丂應掕丒昞帵峏怴僒僀僋儖偼丄1昩偲偡傞丅

丂丂丂丂仸丂偙偆尒偰偔傞偲丄偙偺棳傟偺婎杮偼丄崱傑偱傗偭偰偒偨帺嶌僆僔儘偺棳傟偲

丂丂丂丂丂丂 堦弿偱偁傞偙偲偑傢偐傞丅

丂丂丒僴乕僪峔惉懠傕惍棟偟偰傒偨丅

丂丂丂丂嘆丂奜晹儊儌儕丒奜晹僇僂儞僞偼巊傢側偄丅

丂丂丂丂嘇丂PIC偼丄3.3V宯偺PIC32MX340F256H乮Fcy=

80MHz, DATA儊儌儕丗32k僶僀僩乮256k價僢僩乯

丂丂丂丂丂丂 傪巊偆丅

丂丂丂丂嘊丂擖椡CH悢偼丄4CH偲偟丄PIC偺亄5V僩儗儔儞僩巇條偺僺儞偵妱傝摉偰傞丅

丂丂丂丂嘋丂2.8僀儞僠丒僇儔乕QVGA塼徎乮320x 240dot乯墶抲偒昞帵偲偡傞丅

丂丂丂丂嘍丂妋擣偑梕堈偵弌棃傞傛偆偵丄HOLD SW偲丄TRIG MODE SW(僩儕僈丒僗儘乕僾愗懼乯傪梡堄偡傞丅

丂丂丂丂嘐丂僒儞僾儕儞僌廃婜丗丂悢100u乣丂1uS傑偱偺娫偱丄悢揰DSW偱慖戰壜偵偡傞丅

丂丂丂丂嘑丂僾儘僌儔儉偼丄慡偰C尵岅偱婰弎丅

丂丂丒塼徎夋柺僨僓僀儞傕峫偊偰傒偨丅

丂丂丂捠忢丄儘僕傾僫偱偼丄僆僔儘偺傛偆側丄帪娫幉栚惙乮嵗昗儔僀儞乯偼堷偄偰側偔丄夋柺偺忋偺曽偵

丂丂丂帪娫宱夁偺栚惙偑堷偐傟偰偄偰丄昁梫側僞僀儈儞僌帪娫傪尒傞偵偼丄帪娫僇乕僜儖傪堏摦偝偣偰

丂丂丂帪娫傪撉庢偭偰昞帵偡傞傛偆偵側偭偰偄傞丅

丂丂丂崱夞偼丄娙扨側幚尡側偺偱丄僆僔儘曽幃偺嵗昗栚惙傪梡堄偟丄SMPLE廃婜偲丄1栚惙摉偨傝偺

丂丂丂帪娫乮*S/D乯媦傃丄僩儕僈僄僢僕嬌惈傪塼徎塃壓偵昞帵偝偣傞傛偆偵偟偨丅

丂丂丂彯丄嵟弶偺僾儘僌儔儉偼丄僩儕僈嬌惈偼億僕僥傿僽偺傒偱丄SMPLE廃婜偺傒偺昞帵偵偟偨丅

丂丂丂崱夞偺偼丄儘僕傾僫偲偄偆傛傝丄儘僕僢僋僗僐乕僾偲偄偭偨曽偑傛偄偐傕丒丒丒

仭丂2014.7.8

丂丂丒崱尰嵼峫偊偰偄傞僥僗僩僾儘僌儔儉偼丄儕僺乕僩丒僩儗乕僗丒儌乕僪偱丄僆僔儘偱尵偆

丂丂丂僲乕儅儖丒僩儕僈丒儌乕僪偵憡摉偡傞丅

丂丂丂偲傝偁偊偢偙傟偱僜僼僩偺姶怗傪尒偰丄婎杮揑側峫偊偵娫堘偄偑側偄偐妋擣偟偰傒傛偆偲巚偆丅

丂丂丒崱夞丄撈帺偵峫偊側偗傟偽側傜側偄偺偼丄

丂丂丂儊儌儕偺撪梕偐傜敾抐偟偨儘僕僢僋忬懺乮Hi

or Lo or 棫忋傝 or 棫壓傝乯傪塼徎偵丄

丂丂丂1夋柺暘昞帵偡傞娭悢偱偁傞丅乮偦偺懠偵傕妱崬傒娭悢摍偁傞偑丒丒乯

丂丂丂埲慜嶌偭偨帺嶌僆僔儘偺丄Oscillo娭悢偵憡摉偡傞晹暘偱偁傞丅

丂丂丂偙偺晹暘偺娭悢柤傪丄乽LogAna乿偲偟偨丅

丂丂亙LogAna娭悢傪峫偊傞亜

丂丂丂丒儘僕僢僋忬懺傪敾抐偡傞偨傔偵丄慜夞偺僨乕僞偲崱夞偺僨乕僞傪斾妑偟偰

丂丂丂丂嘆丂Lo儗儀儖偱曄壔偑側偐偭偨応崌仺丂Lo儗儀儖昤夋乮Lo懁傊僪僢僩昞帵乯

丂丂丂丂嘇丂Hi儗儀儖偱曄壔偑側偐偭偨応崌仺丂Hi儗儀儖昤夋乮Hi懁傊僪僢僩昞帵乯

丂丂丂 嘊丂慜夞偑丄Lo偱崱夞偑丄Hi偩偭偨応崌仺丂棫忋傝偲偟偰昤夋乮儔僀儞昞帵乯

丂丂丂丂嘋丂慜夞偑丄Hi偱崱夞偑丄Lo偩偭偨応崌仺丂棫壓傝偲偟偰昤夋乮儔僀儞昞帵乯

丂丂丂丂偺傛偆側敾抐丒昤夋傪偟側偗傟偽側傜側偄丅

丂丂丂丒億僀儞僩偼丄敾抐偲昤夋偺僞僀儈儞僌偱偁傞丅

丂丂丂丂嵟弶偺僒儞僾儖偺僄僢僕専抦偼丄専抦偲丄僶僢僼傽儊儌儕傊偺奿擺偼峴偆偑丄昤夋偼丄

丂丂丂丂僩儕僈傪専抦偟偰偐傜2夞栚偺僒儞僾儖偺帪偐傜峴偆偲偄偆揰偱偁傞丅

丂丂丂丂儘僕僢僋忬懺偺曄壔傪敾抐偡傞偨傔偵偼丄慜夞偲崱夞偺2偮偺僒儞僾儖偑昁梫偵側傞

丂丂丂丂偺偱摉慠偲尵偊偽摉慠偩偑丒丒丒

丂丂丂丂偮傑傝丄僶僢僼傽億僀儞僞丗index= 0;偐傜偱側偔丄index=

1;偐傜昤夋偡傞偙偲偵側傞丅

丂丂丒偙偺懠丄斾妑曽朄偺儘僕僢僋側偳専摙偟偰丄僥僗僩僾儘僌儔儉傪彂偒廔偊偨丅

仭丂2014.7.9

丂丂丒HEX從偒傑偱OK丅

丂丂亙摦嶌妋擣亜

丂丂丂嘆丂傑偢丄START儊僢僙乕僕昞帵偺屻丄摦偐側偄丅

丂丂丂仺丂T1妱崬傒偵擖偭偰偙側偄丅

丂丂丂丂丂 偙傟偼丄僀乕僕乕儈僗偱丄T1妱崬傒嫋壜偺丄Config婰弎偑敳偗偰偄偨丅

丂丂丂丂丂

偙偺廋惓偱丄妱崬傒儖乕僠儞偵擖偭偰偔傞傛偆側偭偨丅

丂丂丂丂丂 CH1擖椡偺僄僢僕僙儞僗偼摦偄偰偄偰丄儊僀儞儖乕僾偼夞偭偰偄傞傛偆偩偑丄昞帵偑慡偔

丂丂丂丂丂 懯栚丅

丂丂丂丂丂 崱丄CH1偺傒偵丄1kHz 3V儗儀儖偺嬮宍攇傪擖傟偰偄傞偺偩偑丄昞帵偼Hi儗儀儖偺傑傑偵尒偊傞丅

丂丂丂嘇丂傑偨丄僒儞僾儕儞僌廃婜傪愗懼偰傕丄200uS昞帵偺傑傑偵側偭偰傞丅

丂丂丒婥偢偄偨揰偁傝丅

丂丂丂崱夞丄ADC偼巊傢側偄偺偱丄偙傟偲楢摦偟偰偄傞T3埲奜傪巊偍偆偲巚偭偰丄T1傪巊偭偰偄傞偺偩偑

丂丂丂T1偵偼丄撪憼僾儕僗働乕儔偺暘廃愝掕偺拞偵丄1/2乮儅僋儘婰弎偱丄T1_PS_1_2乯偑側偄偙偲偵婥偑

丂丂丂偮偄偨丅

丂丂丂偦偙偱丄偄偮傕偺T3傪巊偆偙偲偵偟偨丅

丂丂丂偳偆傕丄ADC偵楢摦偱巊偆T3乮ADC妱崬傒乯偺愝掕乮儅僋儘傪巊傢側偄儗僕僗僞捈愙傾僋僙僗婰弎乯

丂丂丂偱偼忋庤偔峴偐側偄傛偆偩丅

丂丂丂T3傪扨弮僞僀儅妱崬傒偱巊偆応崌偼丄儅僋儘婰弎乮OpenTimer3()偱偺婰弎乯偵偟側偄偲懯栚偩偭偨丅

丂丂丒嘇偵偮偄偰偼丄DSW-1弌椡傪撉崬傔側偔丄僒儞僾儖廃婜昞帵丗SMP=

**偑曄壔偟偰側偄傛偆偩丅

丂丂丂偙偺尨場偼捈偖傢偐偭偨丅

丂丂丂嵟弶偼僴乕僪傪媈偭偨偑丄僴乕僪偵偼堎忢側偔丄寢嬊偼丄億乕僩偺僀僯僔儍儔僀僘偺嵟弶偵

丂丂丂傗傞傋偒丄傾僫儘僌丒僺儞偵偡傞偐丄僨僕僞儖丒僺儞偵偡傞偐偺愝掕傪丄崱夞偼丄慡偰僨僕僞儖丒僺儞

丂丂丂偲偟偰巊偆偺偱丄僨僼僅儖僩偺傑傑偱OK偩傠偆偲徣棯偟偨偺偑偄偗側偔丄

丂丂丂AD1PCFG= 0xFFFF;傪捛壛偟偰OK偵側傞丅

丂丂丒偙傟偱傛偆傗偔摦偒弌偟偨丅乮怺栭0丗30崰乯

丂丂丂SMP昞帵OK

丂丂丂儘僕僢僋昞帵偼丄傑偲傕偱側偄偑丄CH1偺帪娫幉偑丄僒儞僾儖廃婜愝掕偲崌偭偰偄傞偙偲傪妋擣偟偨丅

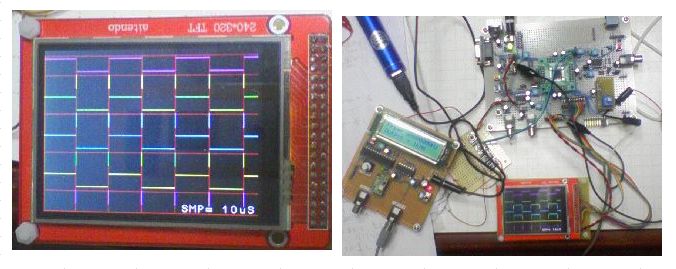

丂丂丂SMP= 10uS偵偰丄1栚惙500uS丄CH1偺傒偵1kHz擖椡帪丄2栚惙偱丄1廃婜偵側偭偰偄傞丅

丂丂丂偟偐偟丄昞帵億僕僔儑儞偑忋偵偢傟偰偄傞傛偆偱偁傞丅

丂丂丂Hi儗儀儖偺儔僀儞偟偐昞帵偟偰側偄傛偆偵尒偊傞丅

丂丂丂亙懳張偟偨帠亜

丂丂丂丒僾儘僌儔儉儈僗

丂丂丂丂僶僢僼傽偺撪梕偐傜丄儘僕僢僋忬懺乮Hi or Lo or

棫忋傝 or 棫壓傝乯傪敾抐偡傞儖乕僠儞

丂丂丂丂傪丄堷悢偵傛偭偰丄奺CH偱嫟捠偵屇傋傞娭悢偵偟偨偑丄偦偺娭悢偺拞偱丄CH枅偵

丂丂丂丂塃價僢僩丒僔僼僩悢傪曄偊側偗傟偽偄偗側偄偲偙傠丄偦偆偟側偐偭偨丅

丂丂丒偦傟傪捈偟偨傜丄2CH偵摨偠廃婜偺嬮宍攇擖椡帪丄戝曽摦偔偲偙傠傑偱棃偨丅

丂丂丂傑偩傑偩昞帵偑偍偐偟偄偑丒丒丒

丂丂丂Hi, Lo儗儀儖昞帵偼丄OK側偺偩偑丄棫忋傝丒棫壓傝偺僄僢僕昞帵偑丄偲傫偱傕側偔壓偵

丂丂丂偢傟偰昞帵偝傟偰偄傞丅

丂丂丂偨偩帪娫娭學偼崌偭偰偄傞丅

丂丂丂傑偨丄嵗昗儔僀儞偲丄Lo儗儀儖昤夋偑彮偟忋偵偢傟偰偄傞丅

丂丂丒偙偺帪偺夋柺幨恀偼嶣偭偰傑偣傫偱偟偨丅

丂丂丂暥復偩偗偩偲丄偪傚偭偲夝傝偵偔偄偐傕偟傟傑偣傫偑丒丒丒

仭丂2014.7.10

丂丂丒偝傜偵挷嵏傪恑傔偨丅

丂丂丂1偮敪尒両両

丂丂丂channel堷悢偺抣偵婰弎儈僗偁傝丅

丂丂丂CH1巜掕偺帪偼丄channel= 1, CH2巜掕偺帪偼丄channel= 2

偙傟偼OK

丂丂 CH3巜掕偺帪偼丄channel= 4, CH4巜掕偺帪偼丄channel=

8偲偟側偗傟偽偄偗側偄偲偙傠

丂丂丂CH3巜掕偺帪丄channel= 3, CH4巜掕偺帪偼丄channel= 4偲偟偰偟傑偭偨丅

丂丂丂偙偙偼丄價僢僩丒僔僼僩悢偲楢摦偡傞偲偙傠側偺偱丄價僢僩埵抲偲CH偑懳墳偟偰側偄偲傑偢偄丅

丂丂丂偙偙偼丄儅僋儘偱婰弎偟偨曽偑夝傝堈偄偺偱丄偦偆婰弎偡傞偙偲偵偟偨丅

丂丂丂偙偺廋惓偱丄CH3偲丄CH4傕丄僄僢僕昞帵埵抲偼偢傟傞偑丄儗儀儖昞帵偼惓忢偵弌傞

丂丂丂傛偆偵側偭偨丅

丂丂丂壓偺幨恀傪嶲徠偟偰偔偩偝偄丅乮4CH偲傕偵丄1kHz偺嬮宍攇傪擖椡偟偰妋擣乯

丂丂

丂

丂丂

丂丂丒寢嬊丄偙偺栤戣偼丄嵗昗埵抲偺峫偊曽偑丄僪僢僩昤夋娭悢乮Glcd_Pixcel乯偲丄儔僀儞昤夋娭悢乮Glcd_Line乯

丂丂丂偱堎側偭偰偄偨偙偲偑尨場偩偭偨丅

丂丂仸丂椉曽偺娭悢偲傕偵丄嵍忋妏偑丄尨揰乮0,0乯偲巚偭偰偄偨偺偩偑丄儔僀儞昤夋娭悢乮Glcd_Line乯偼丄

丂丂丂丂 嵍壓妏偑丄尨揰乮0,0乯偱偁偭偨丅

丂丂丂丂 偙傟傪丄幚徹偟偨帪偺儊儌傪壓偵傾僢僾偟傑偡丅

丂丂丒偙偺栤戣傪廋惓偟偨傜丄崱搙偼丄傑偲傕側昞帵偵側偭偨両両

丂丂丂CH1偺丄Lo儗儀儖嵗昗慄偑昞帵偝傟偰傑偣傫偑丄偦偺晹埵暘偺僾儘僌儔儉婰弎偑敳偗偰偄偨

丂丂丂偩偗側偺偱丄偁偟偐傜偢丅

仭丂2014.7.11

丂丂丒嶐擔偺丄嵗昗巜掕廋惓偱丄昤夋偑曄偵側傞栤戣偼夝寛偟偨丅

丂丂丂偙傟偱丄崱夞嵟弶偵峫偊偰偄偨偙偲偼戝曽僋儕傾偱偒偨偑丄偁偲壗揰偐捛壛丄妋擣偟偨偄偙偲偑偁傞丅

丂丂亙捛壛婡擻摍亜

丂丂丂嘆丂尒塰偊偺栤戣偩偑丄

丂丂丂丂丂 尰嵼偺奺CH昞帵偼丄偪傚偭偲忋偵婑傝偓傒側偺偱丄壓偵壓偘偰尒塰偊傪挷惍偟偰傒傞丅

丂丂丂嘇丂SMP= *uS偺昞帵偺懠丄僨價僕儑儞昞帵乮*uS/D乯傕捛壛偡傞丅

丂丂丂丂丂

傑偁丄捠忢偺儘僕傾僫偱偼丄偙偺昞帵偼柍偄偺偑晛捠偩偲巚偆偑丄崱夞偼娙堈幚尡偲偄偆偙偲偱

丂丂丂丂丂

屌掕栚惙偵偟偨偨傔丄偙傟傪捛壛偡傞丅乮僆僔儘偲摨摍乯

丂丂丂嘊丂TRIG MODE SW婡擻偺僜僼僩傪捛壛偡傞丅

丂丂丂丂丂

棫忋傝懠丄棫壓傝傪僙儗僋僩偱偒傞傛偆偵偡傞丅乮儗儀儖僩儕僈偼徣棯乯

丂丂丂丂丂

僆僔儘偲摨偠傛偆偵丄帪娫幉儗儞僕昞帵偺慜偵丄偦偺僉儍儔僋僞傪昞帵偝偣傞丅

丂丂丂嘋丂僒儞僾儖廃婜偺嵶偐偄乮僒儞僾儖廃攇悢偺崅偄乯曽偑偳偙傑偑忋尷偐妋擣偡傞丅

丂丂丂丂丂 1uS偼OK側偺偱丄0.4uS, 0.2uS乮偙傟偼柍棟偐傕偟傟側偄偑丒丒乯

丂丂丂丂丂 偺2偮傪捛壛偡傟偽條巕偑敾傞偲巚偆丅

丂丂丒嘆乣嘊偺廋惓乣妋擣偼OK両両

丂丂 嘋偵偮偄偰偼丄僒儞僾儖廃婜偼丄1uS偑忋尷偱偁偭偨丅

丂丂丂乮0.4uS, 0.2uS偼丄惓偟偔嬮宍攇廃婜偑曄壔偟側偐偭偨丅乯

仭丂2014.7.12

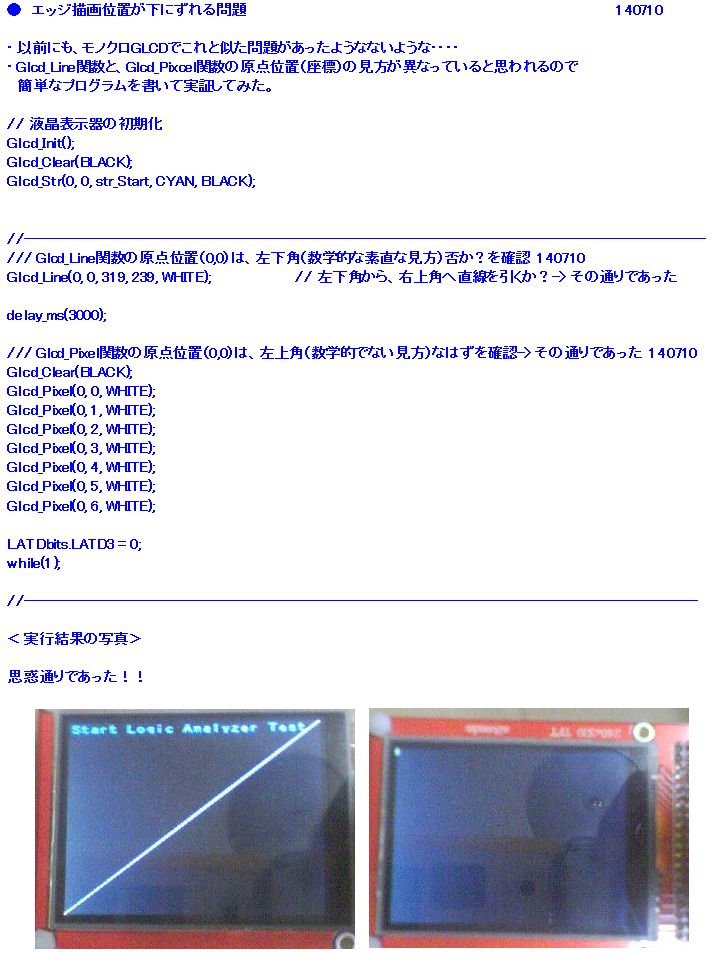

丂丂丒偙傟偱丄捛壛婡擻傕OK偵側偭偨偺偱丄崱擔偼僞僀儈儞僌攇宍偺僒儞僾儖庢傝傪峴偭偰傒偨丅

丂丂丂壗傪僞乕僎僢僩偵偟傛偆偐柪偭偨偑丄寢嬊僶僀僫儕僇僂儞僞偺4bit弌椡傪尒傞偺偑堦斣

丂丂丂夝傝堈偄偲巚偄丄僞乕僎僢僩偺儘僕僢僋IC傪丄僕儍儞僋敔傛傝扵偟巒傔偨丅

丂丂丂栚摉偰偼丄74HC393偱偁偭偨偑丄393偼柍偔丄偦傟埲慜偺丄74LS293偑2屄僕儍儞僋敔偵

丂丂丂偁偭偨丅

丂丂丂憡摉愄偺傕偺偱丄IC僺儞傕崟偔嶬傃偮偄偰偄傞傛偆偵尒偊傞丅

丂丂丂偙傟偱摦偔偺偐偲巚偄側偑傜傕丄憗懍4bit僶僀僫儕16怴僇僂儞僞偲偟偰偺攝慄傪巒傔偨丅

丂丂丂偦偺帪偺幚尡偺條巕偲丄僞僀儈儞僌攇宍偺僒儞僾儖偼杮儁乕僕偺僩僢僾偺幨恀傪嶲徠偟偰偔偩偝偄丅

丂丂丂崱夞偺幚尡偼偙偙傑偱偱偡丅

丂丂丂崱屻偺壽戣偱偡偑丄偙傟偲摨偠僶乕僕儑儞偺丄6CH擖椡壔傪峫偊偰偄傑偡丅

丂丂丂8CH擖椡偲偄偒偨偄偲偙傠偱偡偑丄崱偺墶抲偒昞帵偱偼丄昤夋偑丄偒偮偒偮偵側傝偦偆偱偡丅

丂丂丂廲抲偒昞帵偲偄偆偙偲傕峫偊傜傟傑偡偑丄儔僀僽儔儕傪偄偠傞昁梫偑偁傝傑偡丅

丂丂丂傑偨弌棃傟偽丄廂榐儊儌儕僄儕傾傪憹傗偟丄墶僗僋儘乕儖偱儊儌儕慡懱傪尒傟傞傛偆偵傕

丂丂丂偟偨偄偲巚偭偰偄傑偡丅

丂丂丂乮崱偺偲偙傠丄弌棃傞偐偳偆偐帺怣偑偁傝傑偣傫偑丒丒丒偁偔傑偱壽戣偱偡丅乯

亙嵟廔夞楬恾亜

丂丒偙偪傜偐傜丄偳偆偧仺丂乽PIC32MX_娙堈4CH儘僕傾僫幚尡 夞楬恾乿

亙嵟廔僜乕僗媦傃丄僿僢僟乕僼傽僀儖亜

丂丒偙偪傜偐傜丄偳偆偧仺丂Easy_4CH_LogAna_TEST.c

丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂 colorlcd_libdsPICVH.c

丂丂丂丂丂丂丂丂丂丂丂丂丂丂 colorlcd_libdsPICVH.h

丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂 ASCII12dot.h丂乮12*12_僼僅儞僩僨乕僞丗丂屻娬巵偑嶌惉偝傟偨丄傾僗僉乕暥帤僨乕僞偵丄僆僔儘梡摿庩僉儍儔僋僞傪捛壛乯