● 実験テーマ51

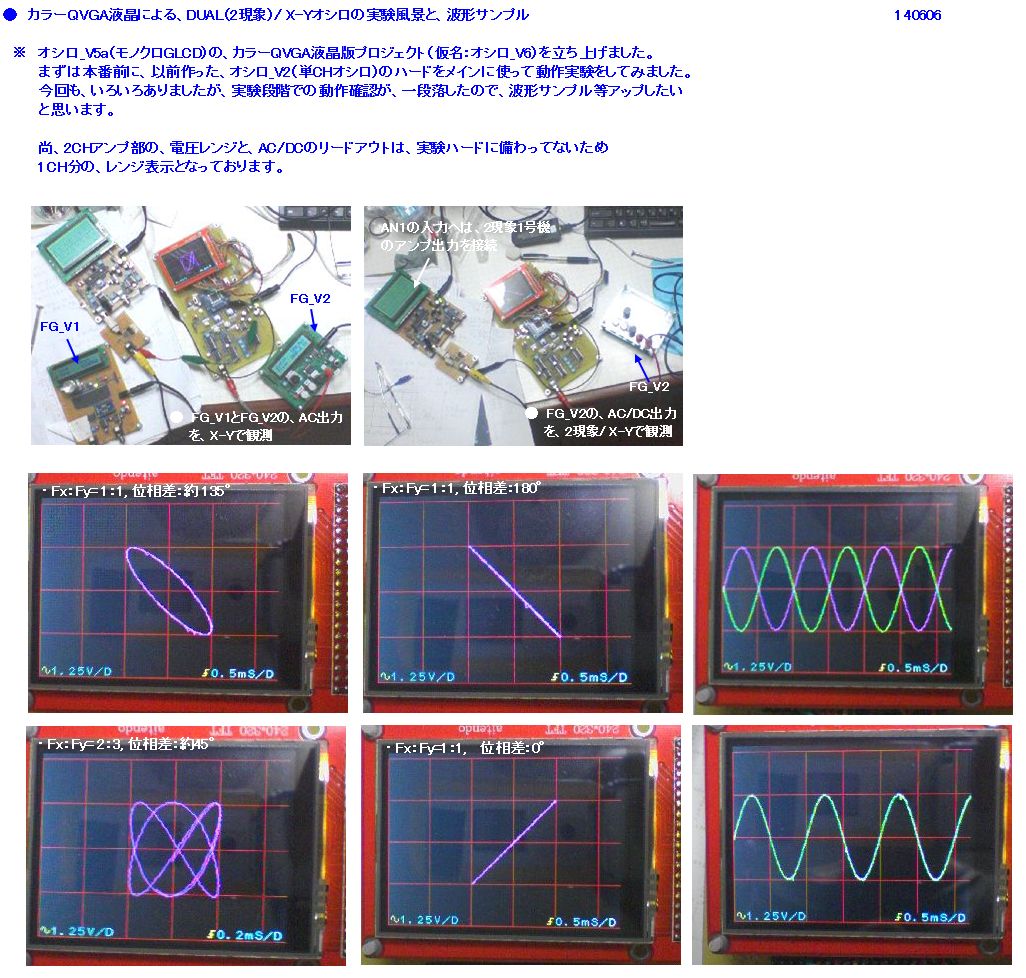

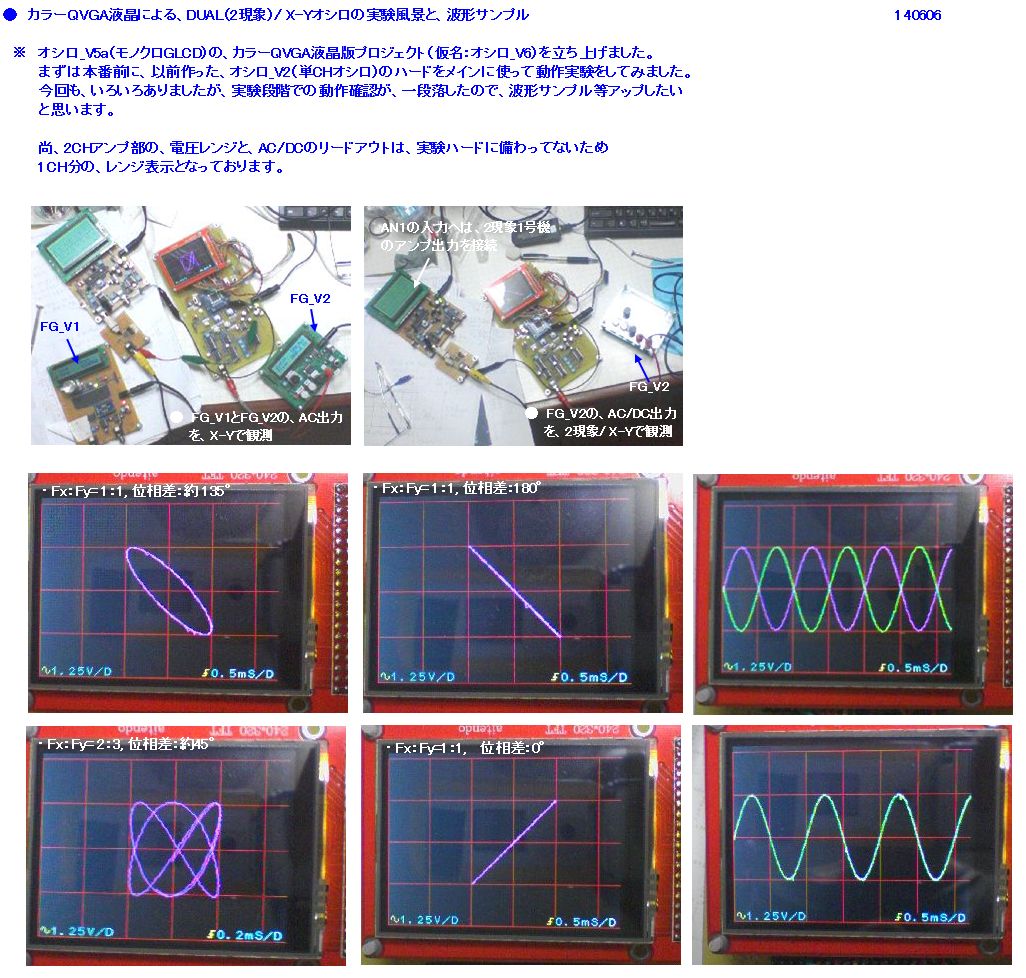

「カラーQVGA液晶による、DUAL(2現象)/ X-Yオシロの実験」

■ 2014.5.25

・リサージュ図形表示が、モノクロGLCDでうまく行ったので、これをカラーQVGA液晶に表示させたい

という思いがある。

最終目標を、オシロ_V6として、それに向けての、いくつかの実験をしてみたい。

・カラーQVGA液晶は、使い慣れている、

aitendoの、2.8インチQVGA(320x240dot TFT)キャリーボード:M028C9325TPを使うことにし

さっそく手配した。

・実験機としては、PIC24HJ64GP206を使った、オシロ_V2(単CH・モノクロGLCD)が、扱い易い

ので、これを使うことにする。

2CHの実験をするには、AN1が空きピンになっているので、2現象初号機のアナログアンプから

そこに、入力すれば何とかなる。

■ 2014.5.26

・実験を進めるためには、モノクロGLCDのインターフェースを、カラーQVGAインターフェースに

接続変換するための治具基板が必要になる。

8bitのデータバスは、同じポートで接続的にはどちらも使えるが、他のコントロール信号は当然仕様

が異なるのでそうはいかない。

手書きラフで解りにくいかもしれないが、その治具の、オシロ_V2との接続図と、治具の

外観写真を、ここにアップしました。(JPEG)→ モノクロGLCD-カラーQVGA液晶接続変換治具の接続図

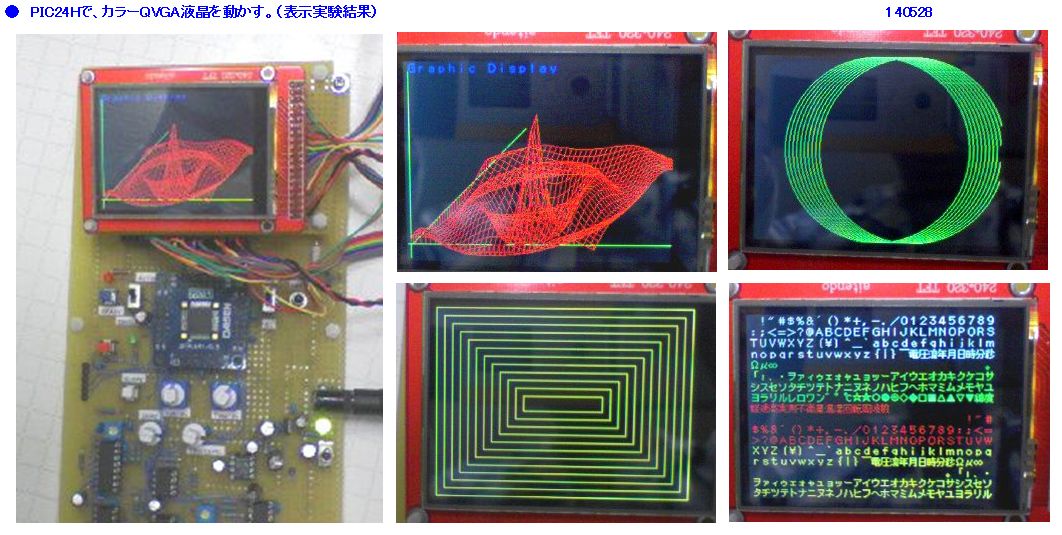

・PIC24Hで、カラーQVGA液晶を動かしたことはないので、最初のステップとして、

「PIC24Hによる、カラーQVGA液晶表示テスト」のソフトを作成して、表示動作の確認をしてみることにした。

作成に際しての、基本方針を考えてみた。

① 大元は、後閑氏作成の、dsPIC33F用の、グラフィック・ライブラリを利用する。

② チェックプログラムのベースは、実験テーマ31で作成した、PIC32MX用のを利用する。

→ たぶんPIC24Hと、dsPIC33Fは、DSP機能の有無だけの違いで、殆ど同じ内部アーキテクチャ(クロック等)

なので、ライブラリ自体は、後閑氏作成のものが使えると思うが、QVGA信号ピンの割付は、現在の

ハードに合わせ変えてやる必要がある。

またチェックプログラムも、32bitと、16bitの違いがあるものの、基本殆ど同じでよいはずである。

■ 2014.5.27

・チェック・ソフト(PIC24H_QVGA_TEST.c)の作成~ コンパイルまで終了。

・aitendoより、カラーQVGA液晶が届いた。

■ 2014.5.28

・昨日届いた、カラーQVGA液晶を試す。

最初は、ブレイクアウト基板裏側の、J1ショートのみで、8bitモード(WEB当該製品ページの説明通り)

にして、オシロ_V3(PIC32MX使用)に以前作成した、TESTプログラムをロードしてチェック。

やはりダメ!!

例の、R1を外して、R2ランド間ショートの改造(実験テーマ31の改造資料参照のこと)を行う。

これで問題なく動いた。

・いよいよオシロV2のハード+QVGA治具にて、PIC24H_QVGA_TESTプロジェクトが動くか確認。

問題なく、すんなり一発OK!!

以下に表示結果の一部を示す。

・これで、オシロV2のハードを使い、PIC24H+カラーQVGA液晶による

2現象オシロの実験が出来るようになった。

■ 2014.5.29

・次の段階として、昨日出来た、表示テストプログラムに、今回の、2現象オシロの、

デモ画面表示(波形なし)を追加して、画面デザインを確認しようと思う。

この前のテーマでやったモノクロGLCDの表示をそのままに、ロケーションを変えるだけに

してみる。

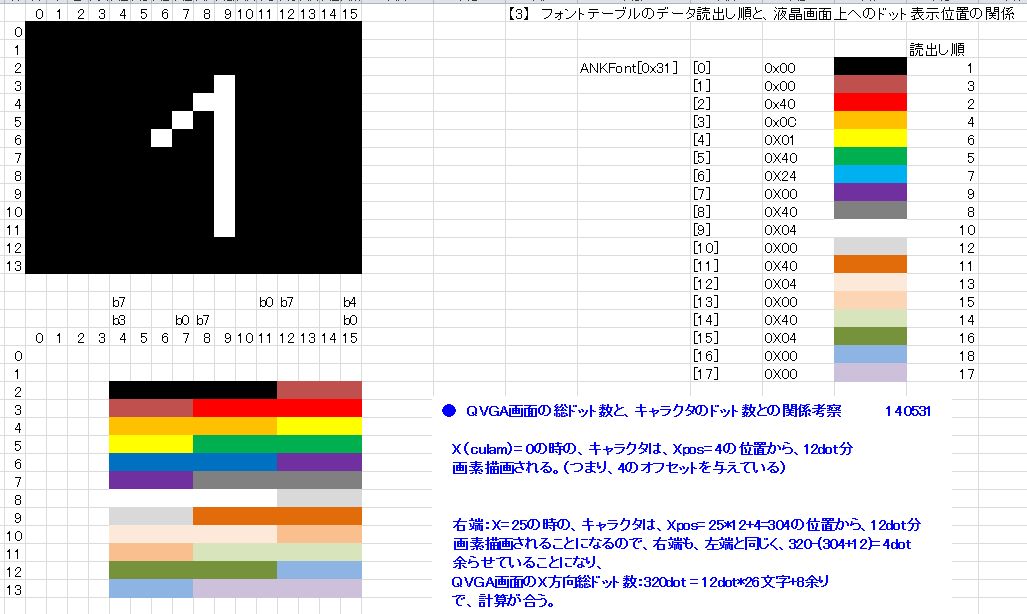

QVGA画面では、M+Bitmap Fontを変換して後閑氏が作成された、

ANK文字12x12dotキャラクタを、X方向(0~25)に、26キャラクタ並べられる。

前は、字数制限の関係で、レンジの、'/D'は省略したが、今回は余裕で並べられる。

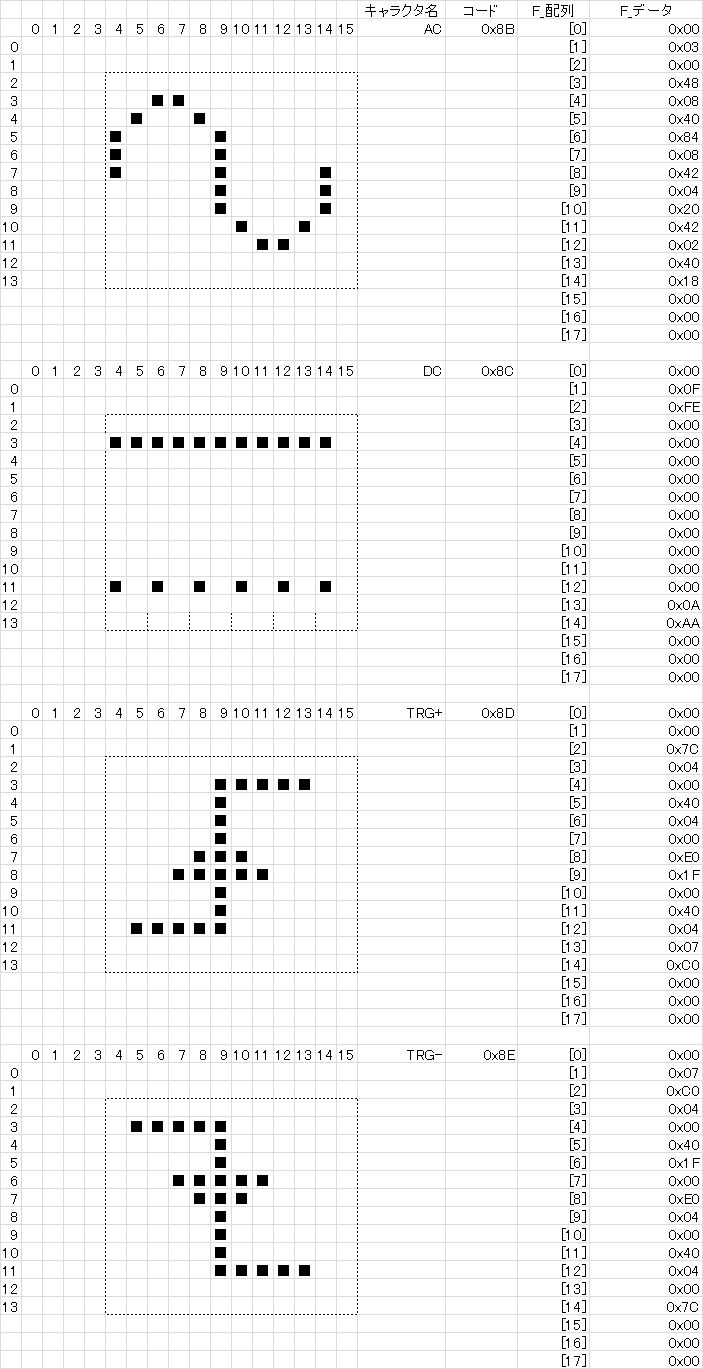

ただ、ちょっと面倒なのは、12x12dotのフォントを、4つ(AC,

DC, TRG+, TRG-の各マーク)

作成しなければならないことである。

これからやってみることにした。

■ 2014.5.30~ 2014.5.31

・ANK文字12x12dotの、フォントデータの構成がどうなっているかを調べないと先に

進めないので、後閑氏が作成された、ANK文字表示関数:lcd_Char()の動きを考察してみる

ことにした。

後閑氏のプログラムには、適時コメントがされているが、コメントだけでは、

明解に解るところまでとても行きつけなかったので、考察(プログラム解析)を始めた。

最初は、画面の左端 (0,0)の位置に、'1'を表示した例で、フローチャートを作成し

考えていったが、なかなか、フォントデータの読出し順と、液晶へのドット表示の関係

が、イメージ出来なかったので、Excelシート上で、プログラムの流れ(各変数の変化等)

を追ってみたら、自分なりの図式が出来、その関係が明解になった。

その時のメモを、以下にアップしました。

要点だけの部分ですが、参考になると思います。

■ 2014.6.1

・ANK文字12x12dotフォントテーブルに、前記の、新規キャラクタを、4つ登録してみた。

・これらのキャラクタを使ったオシロのデモ画面(波形表示なし)もうまく行った。

■ 2014.6.2

・PIC24Hによる、カラーQVGA液晶の表示実験と、新規キャラクタの表示実験まで

うまく行ったので、次は、オシロV2のハードを使っての、カラーQVGA2現象オシロとしての

動作確認を行いたいと思う。

大元の実験ソフトは、「Scope_V5_TEST2.c」を使用。

QVGAライブラリと、ピン定義変更したヘッダーファイル+ANK文字テーブルを、

プロジェクトに登録し、作成したテストプログラムをコンパイルした。

特に問題なしに、HEX焼きまでOKとなる。

動作確認をしてみた。

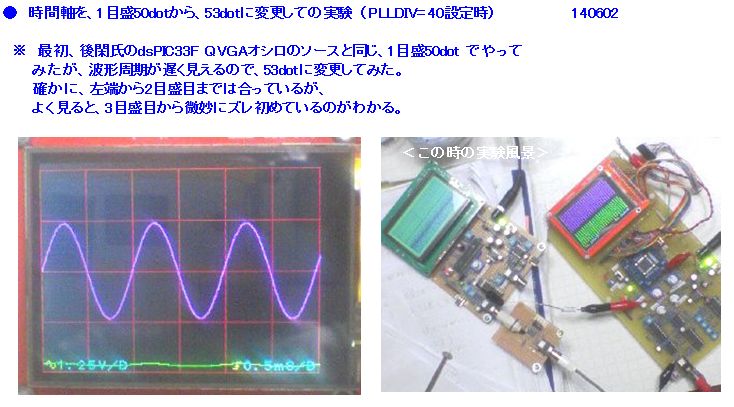

動いてはいるようだが、何故か、時間軸が合わない。

0.5mS/D、1kHz入力で、波形の1周期が、2目盛より少し長く見える。

この時間軸が合わない問題、思い当たる点あり。(HPには未公開だったが・・・)

※ PIC24Hのクロック設定は、注意を要する!!

PLLDIV設定に注意!!

PLLDIVビット(PLLFBDレジスタ)は、マニュアルをよく見ると解るのだが、

設定値そのものが 逓倍値ではない!!

例えば、

PLLDIV<8:0>→ 0b000000000(9bit)設定で、0ではなく、周波数比で、x2(2倍)になる。

現状の、後閑氏のオリジナルソース(PIC24H+モノクロGLCDオシロ)では、

PLLFBDbits.PLLDIV = 40;

となっているので、他のクロック設定パラメータ

(CLKDIVbits.PLLPRE = 0; CLKDIVbits.PLLPOST = 0; )からして

最終的にシステムクロック:Fcy= 42Mzとなるはず。

Fcy=40MHzとするためには、PLLFBDbits.PLLDIV =

38;(38+2で40MHz)

にしないといけないはず。

この辺は後で実証しようと思っている。

後閑氏のオリジナルソース(PIC24H+モノクロGLCDオシロ)では、

PLLFBDbits.PLLDIV = 40; となっているものの、

X座標軸(時間軸)の、1目盛ステップを、53dotとしているので波形表示との辻褄は合っていて

実際の波形周期と時間軸のズレは無く実用上問題なく使えているので、オリジナルのままに

してある。

※ <追記: 140610>

この件に関して、JA1WBYさんより、メールフォーム経由で、貴重な情報を頂きました。

これに関して(Config)の問合せを、「1:PICオシロスコープの製作」(2008年公開)の時に、

後閑氏のBBSを通してしたことがあるようで、その記事(2008.6.23付)によると、

次のような回答だったようです。

「まず修正箇所があります。」

(1)クロック設定の修正 PLLFBDbits.PLLDIV = 38; (40で記述されている)

(2)座標変更

表示位置がわずかにずれていると思います。

dotyline(54); → (50)

dotyline(107); → (100)

やはり後閑さん承知の上のことだったんですね。

失礼しました。

また、dsPIC33F(後閑氏作の、QVGA 2現象オシロ)と、PIC32MX(自作単CH

QVGAオシロ)と、

PIC24Hでは、それぞれクロック設定の方法が異なる。

現状、dsPIC33Fと、PIC32MXでは、時間軸の、1目盛=50dotステップで

時間軸のレンジ(time/div)とサンプル周期との関係が合っているが、

(例えば、0.5mS/Dは、10uSサンプル→ 1kHz(1000uS)入力時、10uSサンプルで

1周期が、1000uS/10uS= 100dot分取れるので、1目盛のdot数=100/2=

50dotで計算が合う。)

PIC24Hを使った現状のオシロでは、システムクロックがやや高く設定されているため

1目盛53dotにしないと、その関係が合わない。

この考察から見ると、今やっている、QVGAオシロも、1目盛50dotから、53dotにすれば、この問題は

一応解決すると思われるが・・・

実際にこの変更をやってみた。

確かに、左端から2目盛目までは合っているが、よく見ると、3目盛目から微妙にズレ初めているのがわかる。

奇数のドット数設定では、最初合ってていても、累積したしわ寄せが後の方に現れる感じがする。

モノクロGLCDでの、PIC24Hオシロでは、液晶の解像度が低いので、時間軸ラインが2本(2目盛)しか

なかったので、その辺が見えてなかっただけかもしれない。(実用上は問題になっていない。)

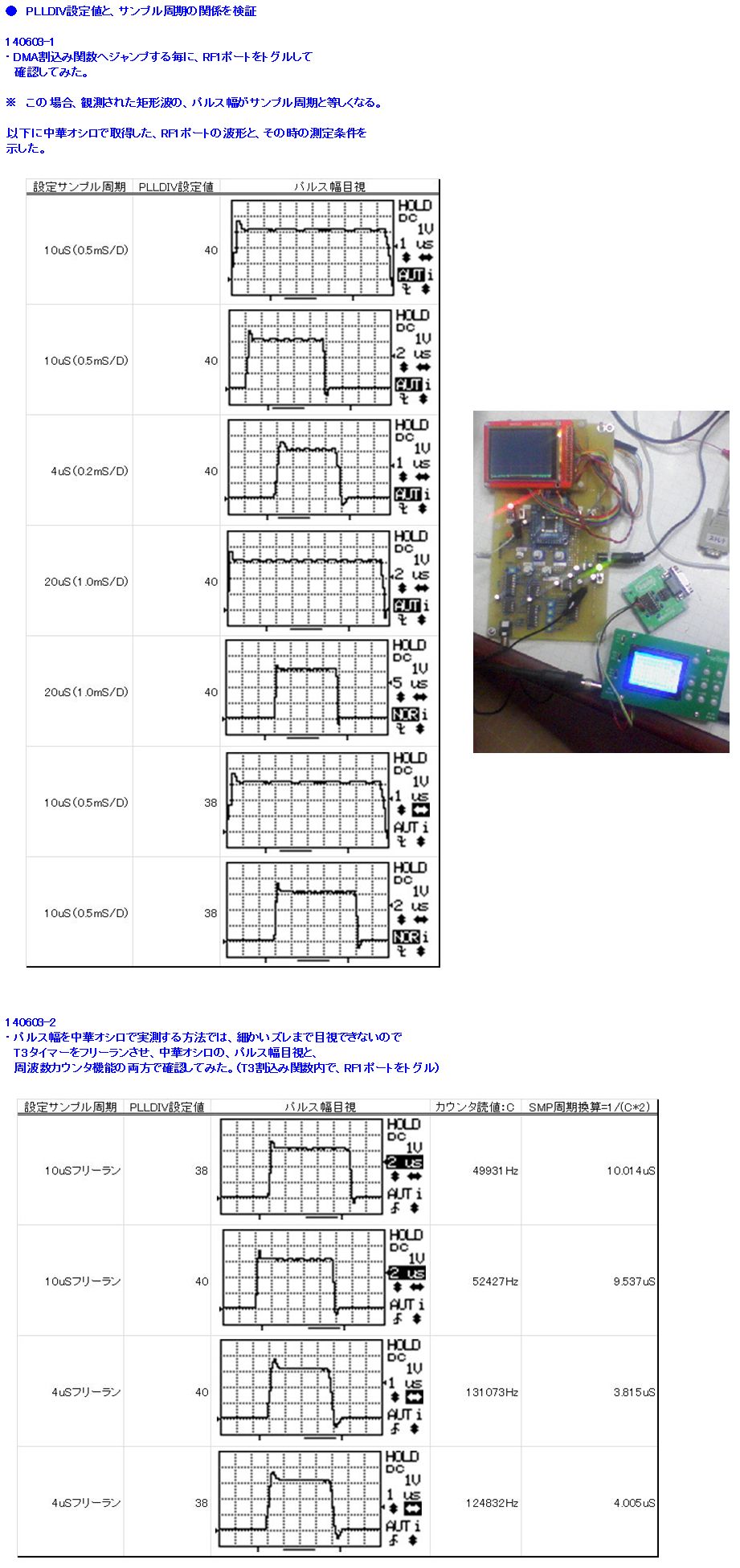

■ 2014.6.3

・昨日までの実験で、どうも、PLLFBDbits.PLLDIV

= 38;/ 時間軸1目盛= 50dotの設定にしないと

合いそうもないことが解った。

しかしまだ、PLLFBDbits.PLLDIV = 38;にすれば、Fcy=40MHzになり、例えば0.5mS/Dの時の

サンプル周期が、10uSになることは、データシートと机上では解っているが、実証できてない。

今日はその実証実験をやってみた。

実証が確認された後に、設定の修正をして波形取りをしてみたい。

Fcyを原発として作っているサンプル周期は、T3タイマーで作られているので、

T3タイマーをフリーランで動かす簡単なプログラムを組んで、その割込みの中で、ポートをトグルさせ

れば、そのパルス幅が、サンプル周期と等しくなる。

オシロで、その幅を測ってもよいが、細かいところまでは解らないので、周波数カウンタで、測定し

後で換算すれば、サンプル周期が求まる。

つまり、サンプル周期= 1/( Fカウンタ読値 x 2)

と計算すればよい。

以下に、その実証実験の結果を示した。

中華オシロでパルス幅を目視した結果と、周波数カウンタで実測し、後でサンプル周期に換算した結果

を、PLLFBDbits.PLLDIV = 40;設定と、PLLFBDbits.PLLDIV = 38;設定の両方でやってみた。

また、DMA割込みの周期とサンプル周期は等しいので、T3タイマーフリーランとは別に

実条件である、DMA割込み上でも同じポートトグルでやってみた。

ただこの場合、フリーランではないので、Fカウンタによる確認はできない。

中華オシロでのパルス幅目視確認のみとした。

※ 上表の結果を見ていただきたい。

PLLDIV設定値=38の時の、SMP周期換算値は、

殆どピタリと合っている(10.014uS, 4.005uS)のに対し、

PLLDIV設定値=40の時は、やや速め(9.537uS, 3.815uS)になっているのが解ると思う。

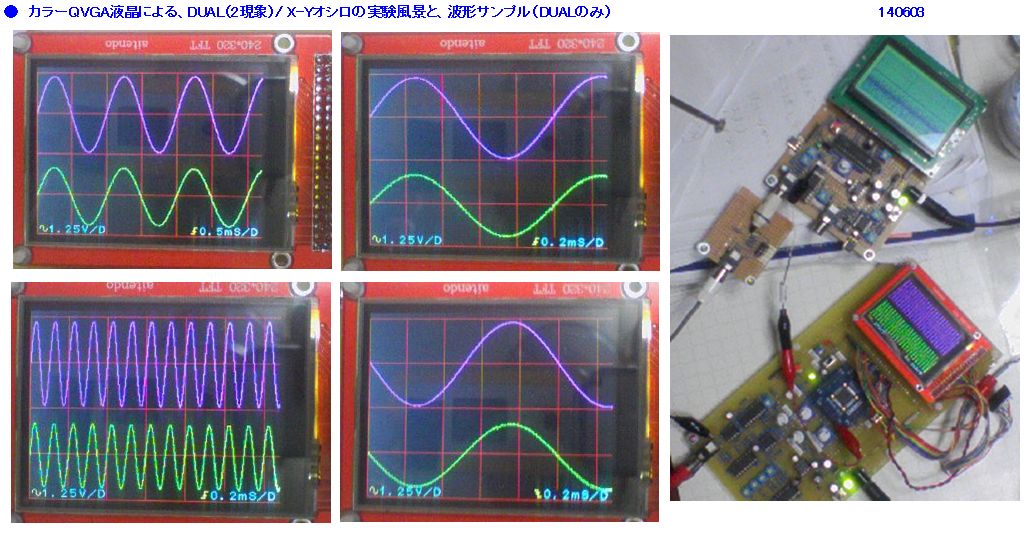

・これで、実証できたので、実際にプログラムを修正して、いくつかの波形サンプルを取ってみた。

今度は、画面全体に渡ってズレることなく合っていることが確認できた。

■ 2014.6.4

・オシロ_V2を使っての、カラーQVGA 2CH(DUAL)モードの実験は、大方OKになった。

ここで、X-Yの実験を、別プロジェクトで行ってみる。

ソフト上の変更は、Oscillo関数と、AxisDraw関数のみでよい。

X-Yモードでの、X軸は、電圧軸になるので、Y軸と同じ、1目盛58dotに変更。

すると、X軸は、5本引けるので(約5目盛半)、右から3本目をセンターにして、4目盛

フルスケールで、X-Y(リサージュ)描画できるようにした。

■ 2014.6.6

・今日は、X-Yモードでの波形サンプル取りを行った。

本ページトップの見出し写真を参照してください。

※ これで、本テーマの実験目的は、一応達せられたので、次期テーマ52で

これを使える形に、まとめていきたいと考えている。

ソースと回路図の公開は、次期テーマで、まとめて公開することにします。

← 実験テーマ1に戻る TOP PAGEに戻る 実験テーマ52へ →