● 実験テーマ47

「PIC32MX_多機能信号発生器_EAGLEによる基板化編」

(ボード名は、「FG

V2 BOARD」としました。約1年ぶりに、EAGLE CADをいじりました。)

■ 2014.1.6~ 2014.1.20(この間の内、4日をこの作業に当てた。)

・まずは、新規部品登録から開始した。

5種類の新規パーツ登録(部品マクロ作成)作業を行う。

(DAC, OPTICAL_ENCODER, RCA_JACK__STRAIGHT等)

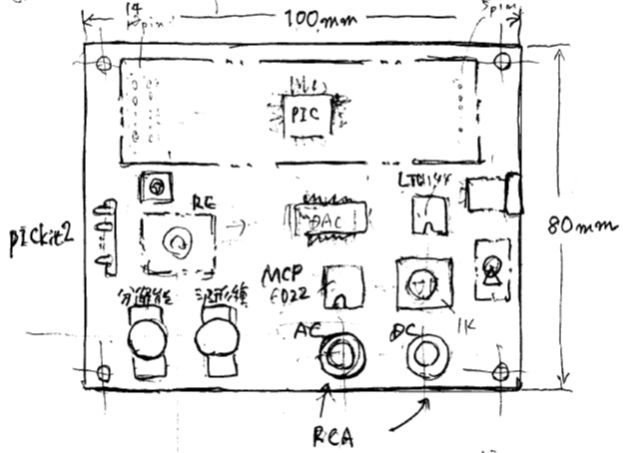

■ 2014.2.4

・ラフ書きにて、EAGLE無償サイズ:100 x 80mmに、全ての部品が収まるか、

ざっと確認してみた。

何とか入りそうである。

■ 2014.2.5~ 2014.2.7

・いよいよ回路図入力作業

■ 2014.2.8

・回路図入力終了後、NET LEST生成→ 特に問題なし。

・次に、ERCチェックを行う。

NET LESTチェックで問題が出てないので、ERCでエラーが出たとしてもパターン(NET)には

影響ないので、無視してもよいと思うが、ここは一応、ひとつひとつエラー・ワーニング内容を

追ってみた。

以下にその代表的なエラー内容と、対処を示した。

<エラー内容>

① OUTPUT and SUPPLY pins mixed on net +5V(SUP)

これは、3端子レギュレータ・シンボルの、Voutピンの、電気的属性'OUT'に対し、

+5Vシンボルのピン属性が、'Sup'(サプライの意)になっているために出るエラーだが、

EAGLEが馬鹿正直に出しているエラーなので無視しても問題ない。

これを出したくなければ、3端子レギュレータ・シンボルの、Voutピンの電気的属性を、

'Pas'(受動端子)に設定すればよいが、今回はやらず、承認(Approved)した。

② SUPPLY

pin +3.3V overwritten with more than one signal (+3.3V, AVCC)

+3.3Vシンボルを流用して、AVCCシンボルとし、ネット生成した為出たエラー

これは承認できるので、特に何もしない。

③ Unconnected

INPUT pin ・・・・・・・

シンボル・ピン属性を、'INPU'としているところに、何も接続されてないとこのエラーが出るが、

意図的なので承認できる。

<ワーニング内容>

① Close but unconnected wire ・・・・・・

これもネットはOKなので無視してもよいが、気持ち悪いので直すことにした。

このワーニングは、シンボル・ピン先端に重ねてワイヤ(ネット)を引くと出るので、1グリッド空けて、

ワイヤを引けば出なくなる。

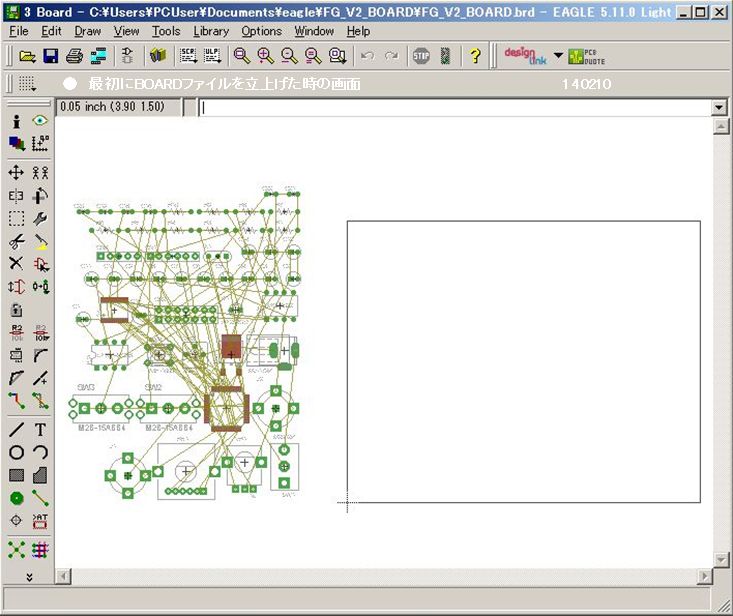

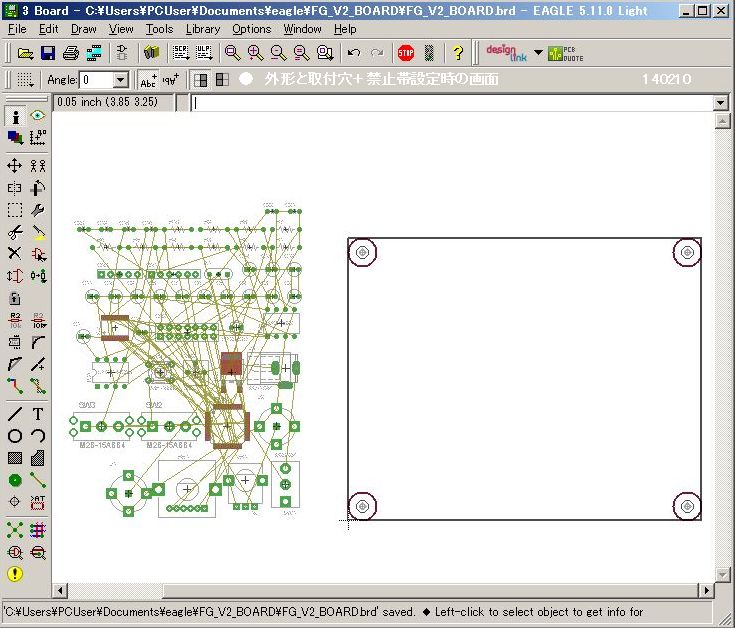

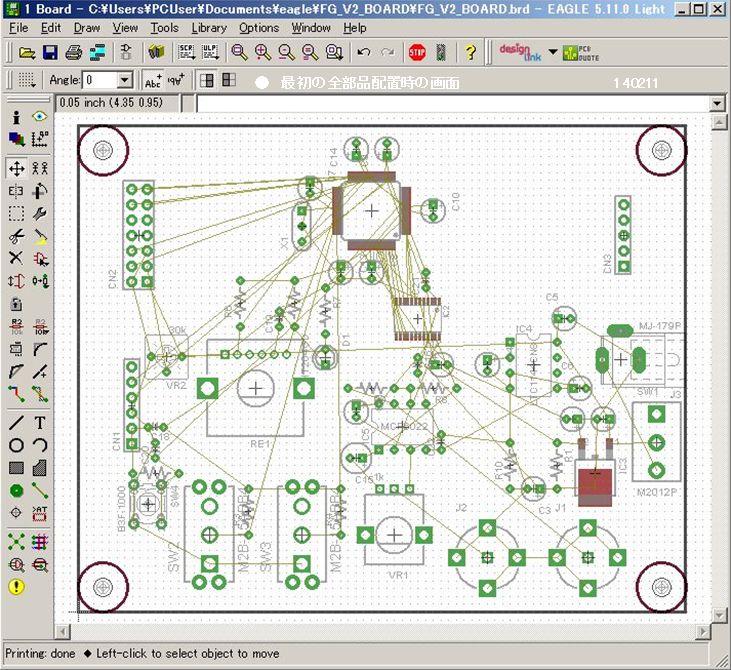

■ 2014.2.10

・次に、Lyoutエディタにて、外形→取付穴→禁止帯設定を行った。

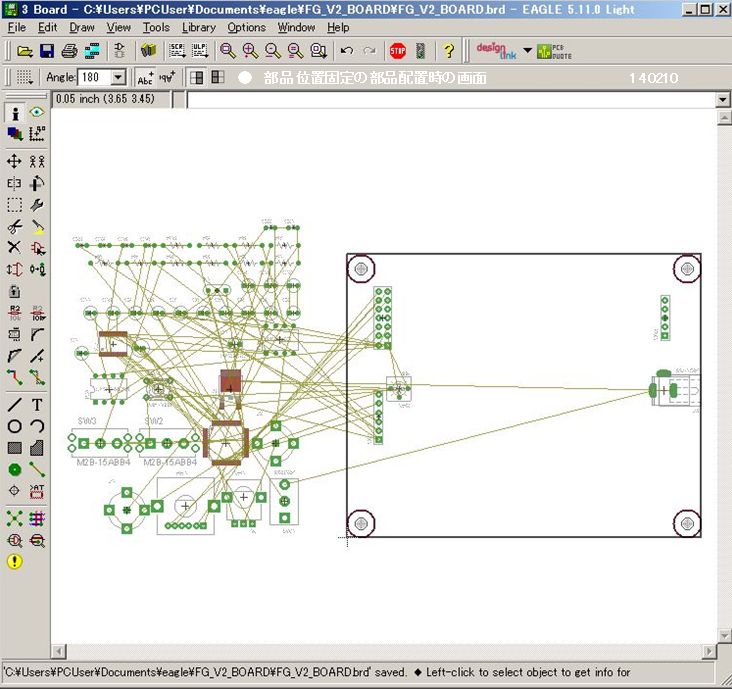

■ 2014.2.11

・部品配置全て完了(一部暫定)

ここまでの配置画面を基板原寸でプリントアウトし、実際の液晶、PIKkit2を、そこに置き、

相互の位置関係を確認した。

配線に移る。

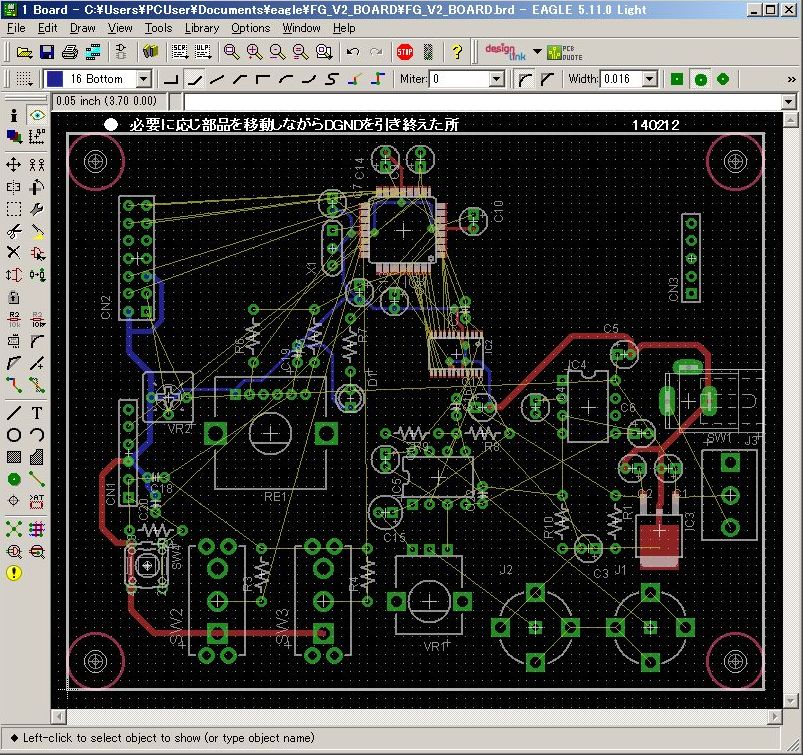

■ 2014.2.12

・DGNDを引き終える。

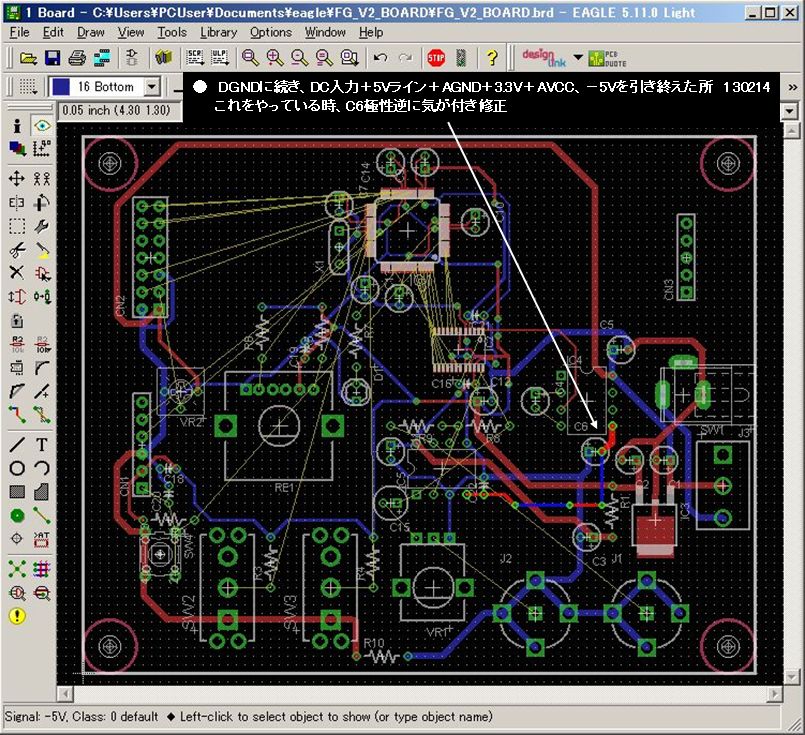

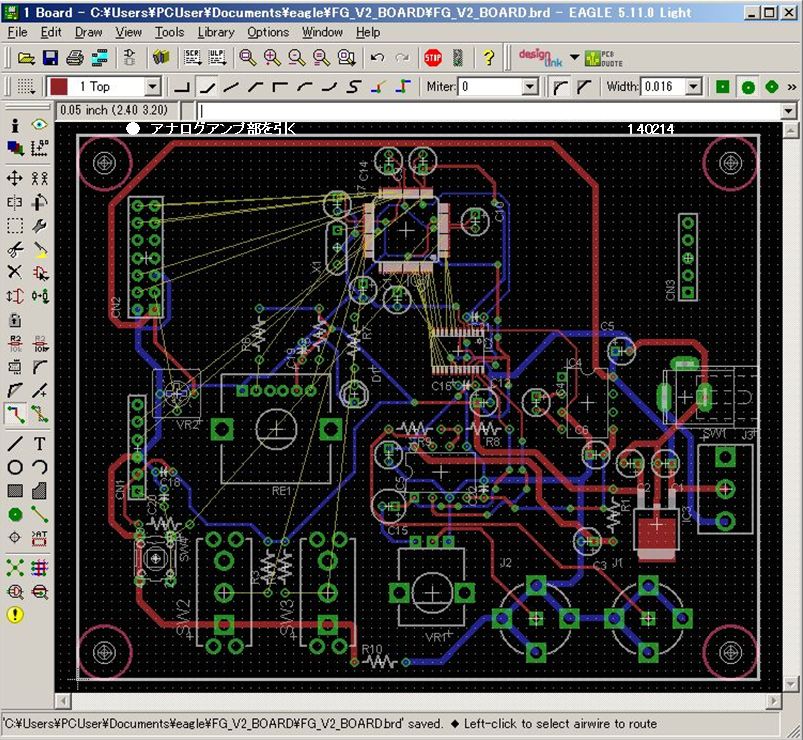

■ 2014.2.14

・電源パターン引き終わりに近ずいたところで、回路図入力時のミスに気が付く。

なんと、負電圧発生ICのパスコン:C6の極性が逆ではないか!!

→ ボード上の関係ネットを削除した後、回路図修正しセーブ

これで、自動的にボードのネットも修正されていることを確認した。

・この後、アナログ部を引き終えた。

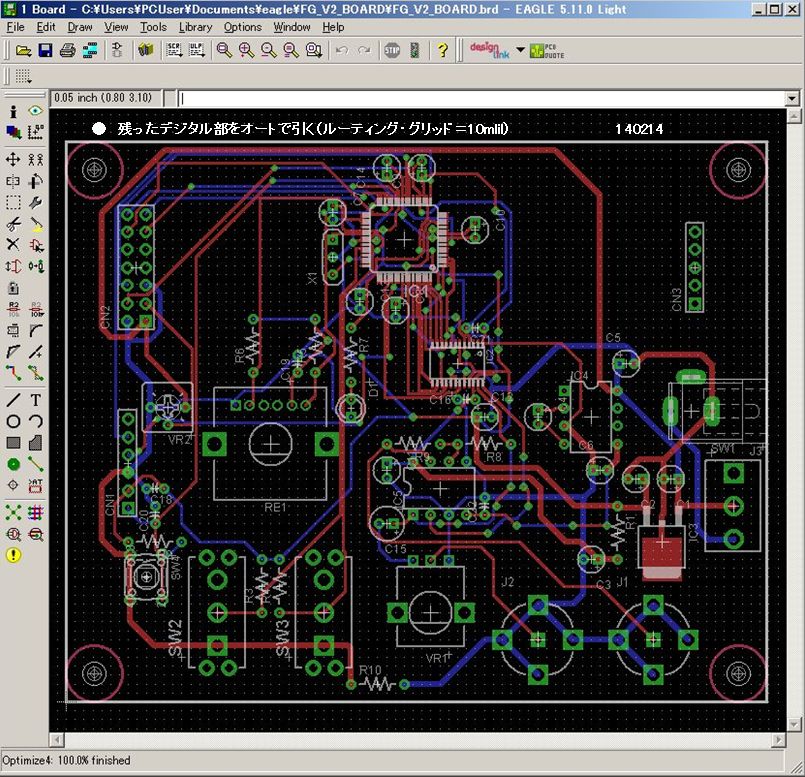

・残ったデジタル部を、ルーティング・グリッド=

10mill設定にしてオート・ルータで引かせてみた。

結果、部品配置が良かったのか、一発で、100% fineshedとなった。

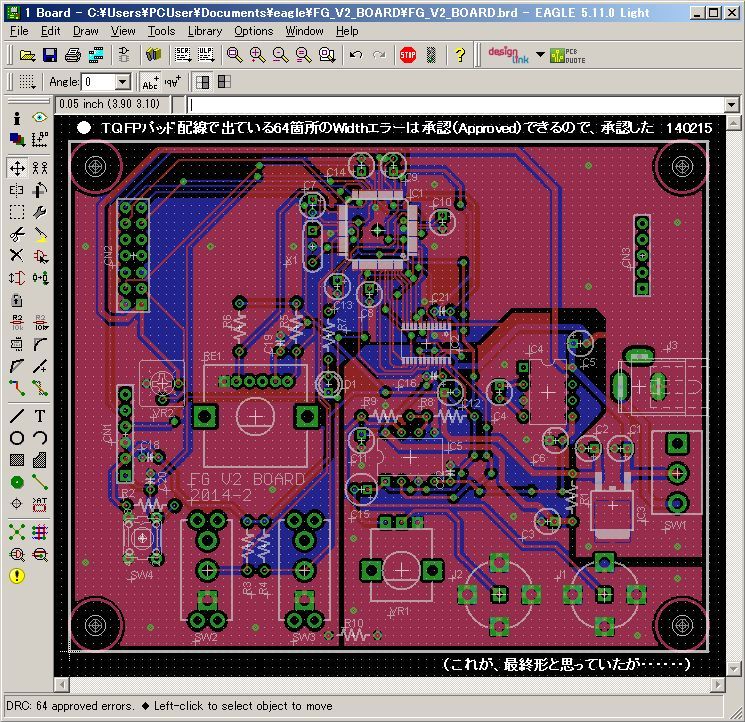

■ 2014.2.15

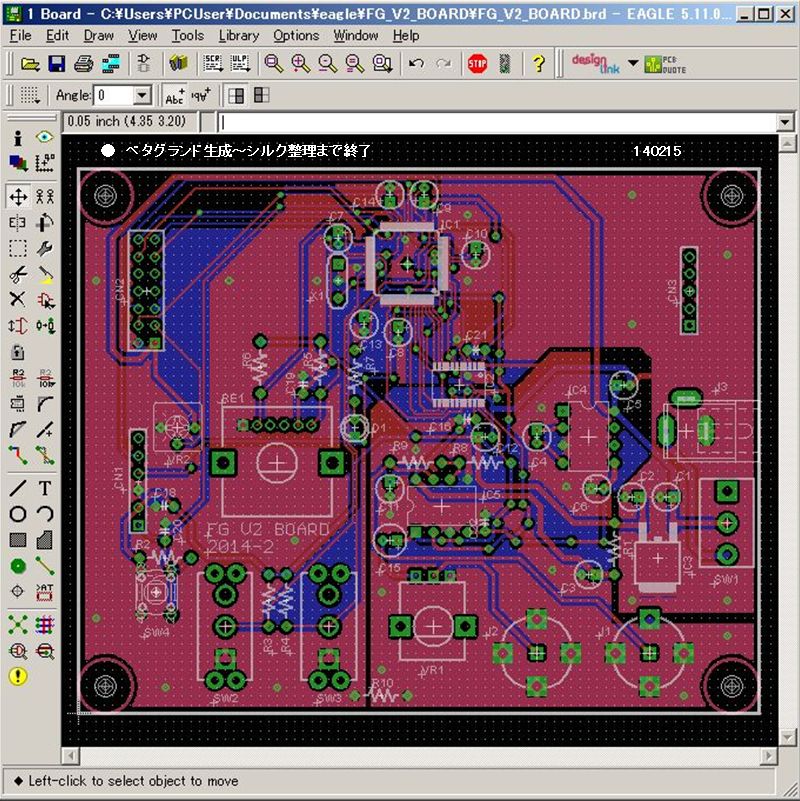

・ただこのままでは、不自然な流れになっている所もあるので、手直し後、ベタグランド生成~

シルク整理まで済ませた。

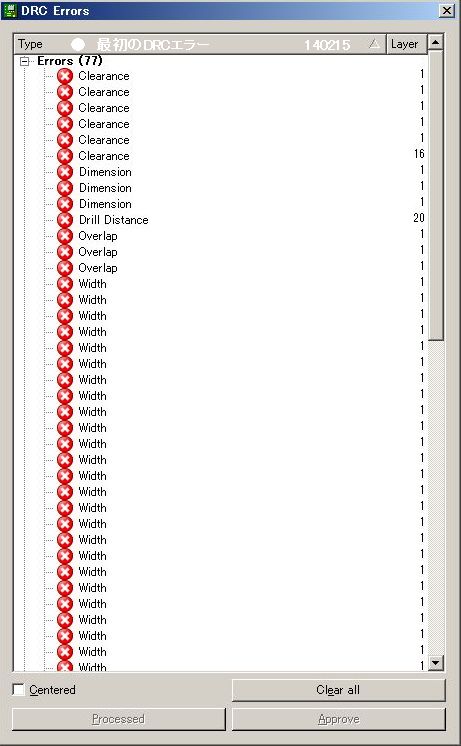

・DRCチェックの結果、最初に出たエラーは、計77エラー

その内、64エラーは、Widthエラー

これは全て、TQFP64パッケージの、パッドの巾に対し僅かながらそこに引いたパターンの巾が広く、

はみ出ている為に出ているエラーであるが、承認できるので承認した。

残りのエラーに対する対処は、次のようにした。

① Dimensionエラー

基板エッジからパターンまでのクリアランス規定(30mill=0.76mm)に引っかかっている所が1箇所あり。

→ 若干パターンを移動して対処

② Drill

Distance+Overlapエラー(この2つは関連エラーと思われる)

CN1のDGNDピンのところに出たエラー

これは見た目に何故エラーなのかと最初は思ったが、(この英語の意味も解りにくいし・・・)

よく見ると、パーツのランドのところに中継ビアが重なっていて、それによるエラーであった。

(どうもパターンを引く時に、無意識に[Shift]キーを一緒に押していたため終点で離した時、

自動でビアが挿入されてしまったようです・・・)

→ これを直すのは、少し厄介であった。

一度その余分なビアをパターンごと移動して引出し、その状態でリップアップをかけネットを切断し、

再度その部分のパターンを引き直した。

③ Clearanceエラー

クリアランス規定(5mill=0.127mm)に引っかかっている所が数か所あり(ビアと、ビアの間隔違反等)

→ ビアとパターンを移動したり、エラー箇所のビア径を、24mill→ 16mill

に変更することにより対処した。

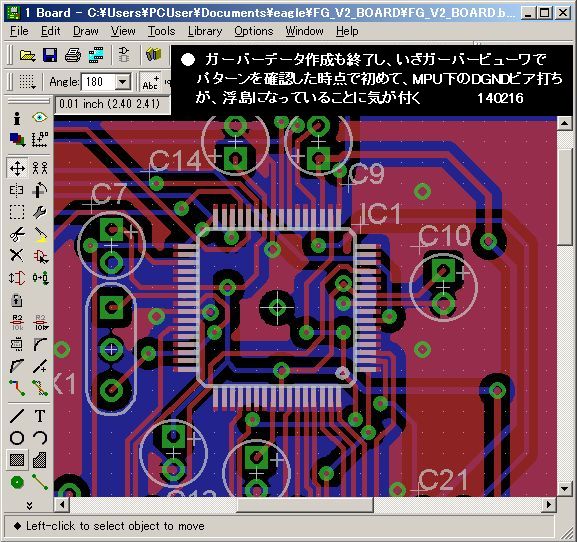

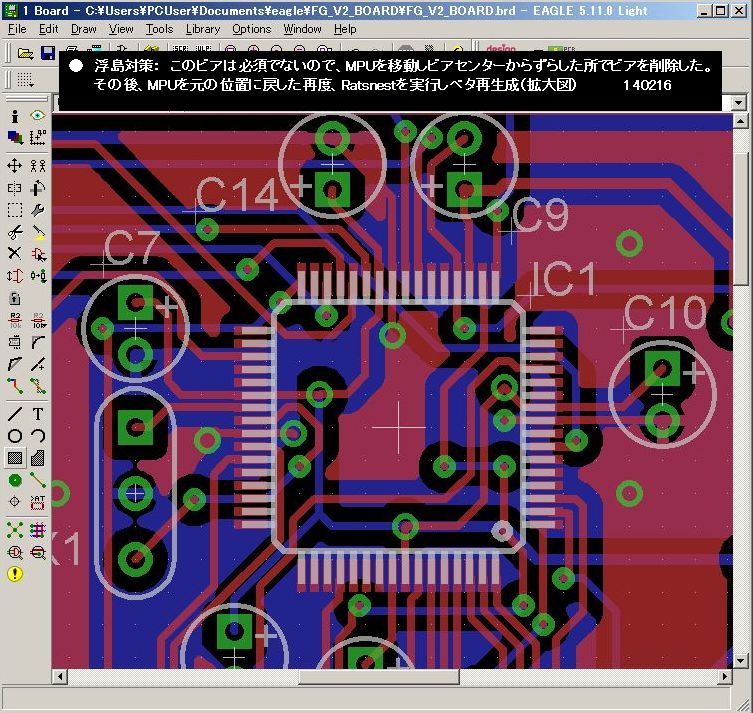

■ 2014.2.16

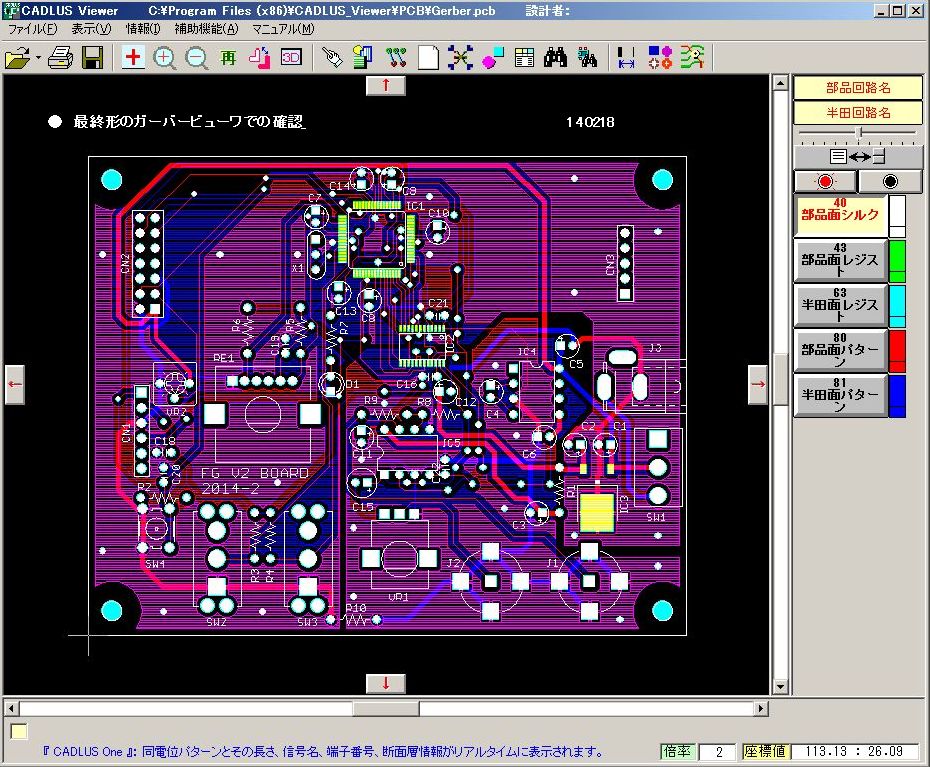

・DRCもOKになったので、ガーバー出力まで済ませた。

ところが、ガーバービューワでの確認のところで初めて、MPUセンターに打ったビアがDGANDベタから分離して、

浮島になっていることに気付いた。

このビアは、MPUのセンターと重なっているので、このビアのNET名を、DGND

に変更しようとビアをクリックしても、

MPUが選ばれてしまい変更できない。

まあ、このビア打ちは必須でないので削除することにした。

削除後、再び、ベタ生成し、ガーバー出力をやり直した。

(これで終わりかと思ったが・・・ 後日またアクシデントが・・・)

■ 2014.2.17

・ここでちょっと問題発生

RSコンポーネンツに手配予定の、RK09Lタイプの、VRの、VALUEラインアップに、1kΩは無いことが発覚。

あるのは、オーディオ用として一般的な、5k, 10k, 20k,

50k, 100kの計5種類

→ 今回は、この中から最小値の、5kΩを使うことにした。

1kから、5kに変更することによって、カップリングC=22uとで構成されるHPFの、カットオフ周波数が、

7.2Hzから、1.45Hzと低い方にずれるので低域レベルについては有利な方向で好都合

→ この変更に伴い、回路図の、VR1の、VALUEを、1k→ 5kに変更

ちょっとボードへの影響が心配だったが、問題なくエラー無しでセーブできた。

BOMも再生成した。

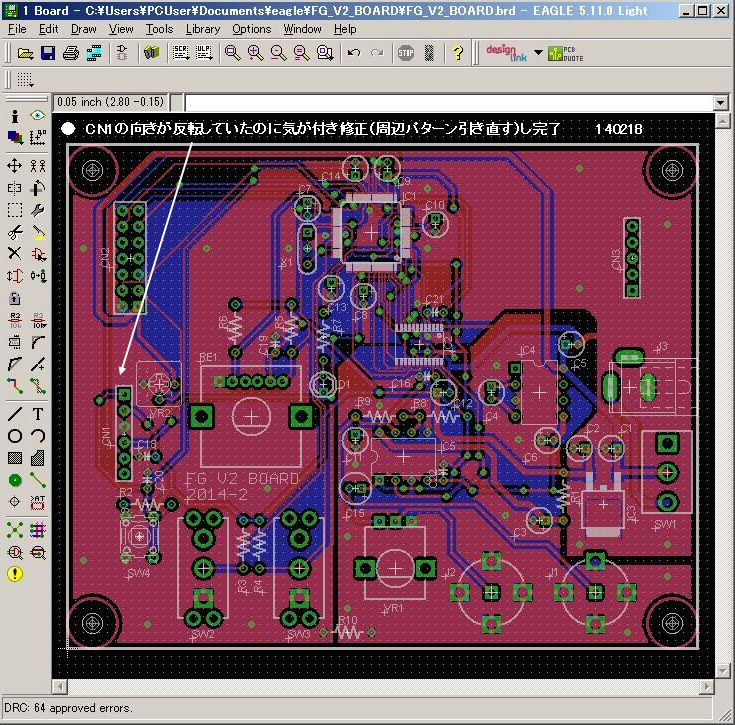

■ 2014.2.18

・今回の回路図の修正は、NET(BOARD)には無関係なのでガーバーも修正の必要はない。

(VR1のボード上のVALUEシルクはしない)

しかし、またもやここで問題発覚!!(今回は後で気付く問題が多過ぎ・・・)

CN1(ここにはライトアングルタイプのピンヘッダーを実装: PICkit2用)の向きが、180度反転していたのだ!!

1ピン側を、CN2に近い方にしないと、PIKkit2を挿入した時にPICkit2表面の、LEDが操作面から見えない位置に

なってしまうし、そもそも上手く嵌合しない。

この修正は、ちょっと面倒であった。

CN1を反転するため、一度CN1のピンのワイヤを、リップアップしてエアーワイヤにし、反転後パターンを引き直し

修正作業は終了した。

・ガーバー出力をやり直し、ガーバービューワでの確認も済んだので

今度こそは、基板屋に手配できるぞ!!

→ 今回もマルツ・エレックに依頼を掛けた。

またマルツ分の部品も手配した。.

■ 2014.2.21

・マルツからのP板上がり待ち状態です。

希望納期: 2014.3.3

■ 2014.2.22

・マルツに依頼した、P板2枚製作の内、1枚にTQFP64パッケージ(PIC32MX)の実装依頼かける。

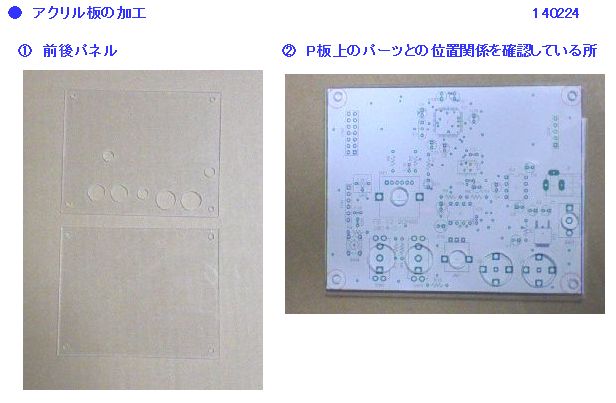

・P板が到着するまで時間があるので、前後アクリル板の加工寸法図をラフ書き検討した。

■ 2014.2.23

・パターン図を見ていて、ちょっと気になるところ有り。

RCAジャック(ストレート)の構造上、部品面に信号ラインが引いてあると、これを実装した時に

信号ラインが、RCAジャックの金属部(シールド)と接触する恐れがある。

また前パネルとのクリアランスを極力少なくするための高さ調整も兼ね、1.6tガラエポ板で

絶縁台座を手作りすることにした。

■ 2014.2.24

・前後アクリル板の加工と、絶縁台座の加工を済ませる。

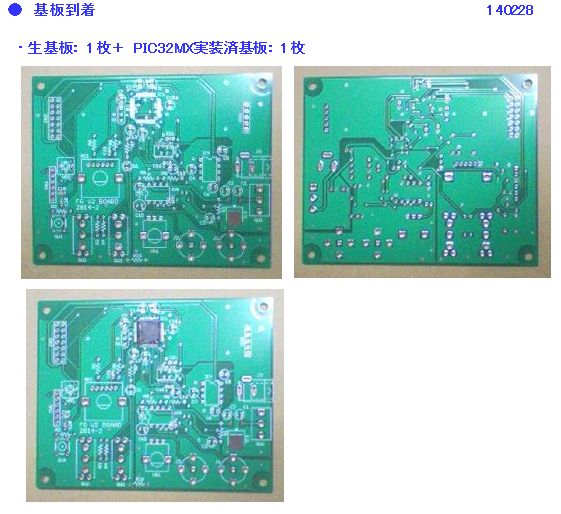

■ 2014.2.28

・希望納期より早めに、P板到着!!

・実装前に電源パターンのショートチェックを行う。

→ +5V⇔DGND/ +3.3V⇔DGND/ AVCC⇔AGND/ -5V⇔AGND/

AGND⇔DGND(一点アースポイント:実装時ここをショート)

各信号間ショートしていないことをテスターにて確認した。

・全ての部品実装完了(新規登録部品:RCAジャック・DAC・REの実装問題なし)

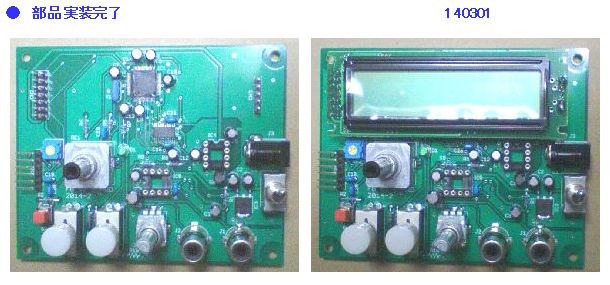

■ 2014.3.1

<実装後のチェック>

① 電源ショートチェック

+3.3V⇔DGND, AVCC⇔AGND→ OK

+5.0V⇔DGND, -5V⇔AGND→ OK

② 電源電圧チェック(全て液晶実装時の電圧を示す)

+3.3V→ 3.29V

+5.0V→ 5.09V

AVCC→ 3.04V

-5V → -4.86V

③ HEX書込み

問題なく書込めた。

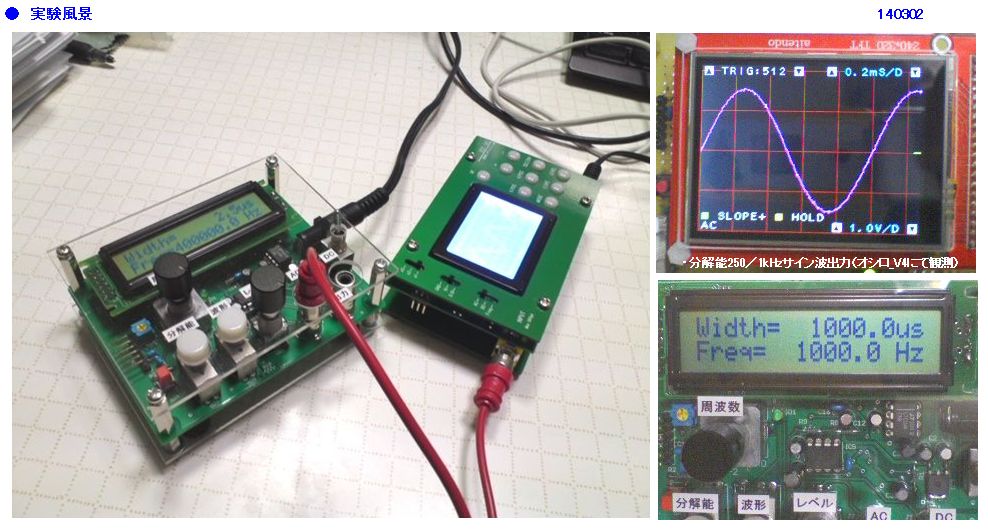

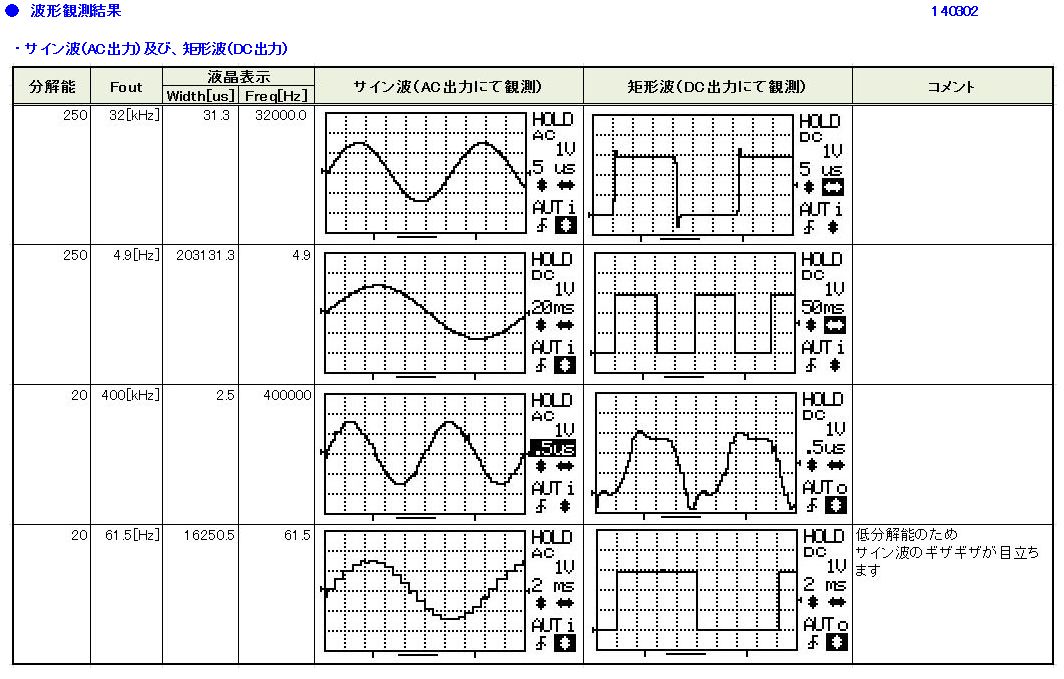

■ 2014.3.2

・機能も問題ないので、サンプル波形取りを行った。→ 特に問題なし。

前回のテーマで、全ての条件での波形取得公開をしてあるので、今回は最大分解能:250

及び、最小分解能:20設定時の波形のみ取得しました。

<最終回路図(EAGLE)>

・こちらから、どうぞ→ 「FG_V2_BOARD」

※ 尚、ソフトは前回(実験テーマ46)の試作実験の時と全く同じです。

← 実験テーマ1に戻る TOP PAGEに戻る 実験テーマ48へ →