● 実験テーマ26

「PIC32MX_MP3プレーヤ(FreeRTOSの応用)_EAGLEによる基板化編」

■ 2013.1.8

・思いつくまま、本案件の要求案等を以下に列記してみた。

<要求案等>

※ ディスクトップに置いて常時使えるようにする。

1枚基板で作りたい。

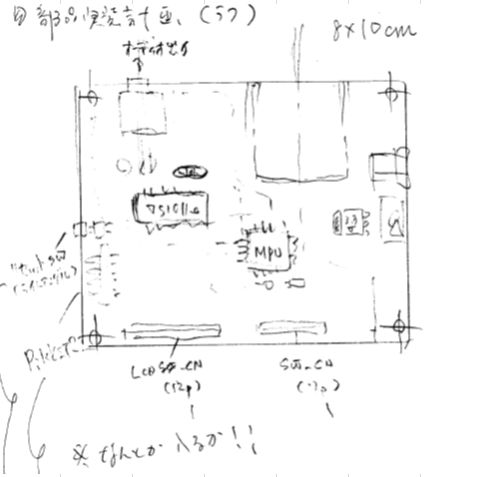

① EAGLEフリー版の、MAXサイズ: 10×8cm内に全て収まるかが問題

(VS1011eは、デュアルラインIC(SMD)を使用予定(実績有))

② とりあえず、64QFPパッケージ登録が必要なのでそれから取り掛かるか?

またEAGLEライブラリを検索して、使えそうなのがあるか検討を始めよう。

③ 操作SWを別の物にしたい思いあり。

MAINボード直付タイプで小型でしかも背が低いタイプがあればよいが・・・

④ ケーシングを考慮した全体構造検討

LCDは、PCB側でなくパネル側に実装した方が、PCB実装効率はよくなる。

(部品を余計に配置できる)

⑤ +3.3Vレギュレータは、PCBに寝かせて実装し放熱電極をハンダ付して使いたい。

⑥ ③については、そういう部品は無さそうなのでスイッチ基板をユニバーサルで作って、コネクタで

メイン基板と接続するようにする。

→ 秋月の、小型ボタン付タクトスイッチ(緑ボタン付)を使うとよいかも・・・ 1個30円で格安

■ 2013.1.9

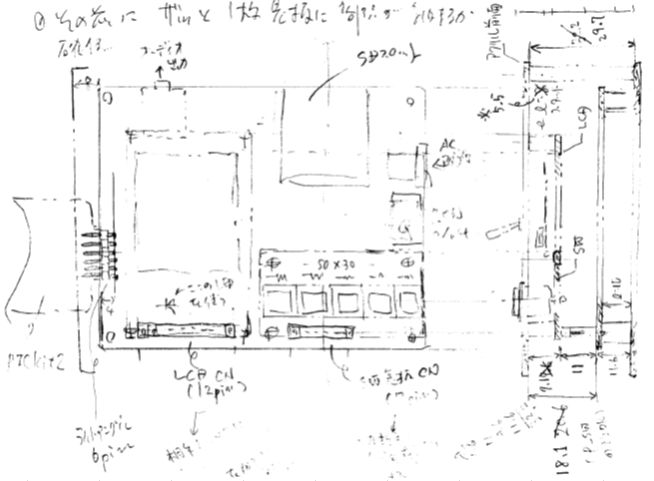

・ざっと、ケーシングも考慮し10×8cmの1枚基板に部品が収まるかラフ書きして確認してみた。

今回は、2t アクリル板を、前面・背面パネルとして2枚加工し、それぞれを、スタッドにて結合しようと

考えている。

→ ラフであるが、何とか入りそうである。

■ 2013.1.10~ 2013.1.12

・9種類の新規パーツ登録(部品マクロ作成)作業を行う。

(MPU, NJM2845DL1-XX, CRYSTAL, 電解コンデンサ等)

■ 2013.1.13

・いよいよ回路図入力開始

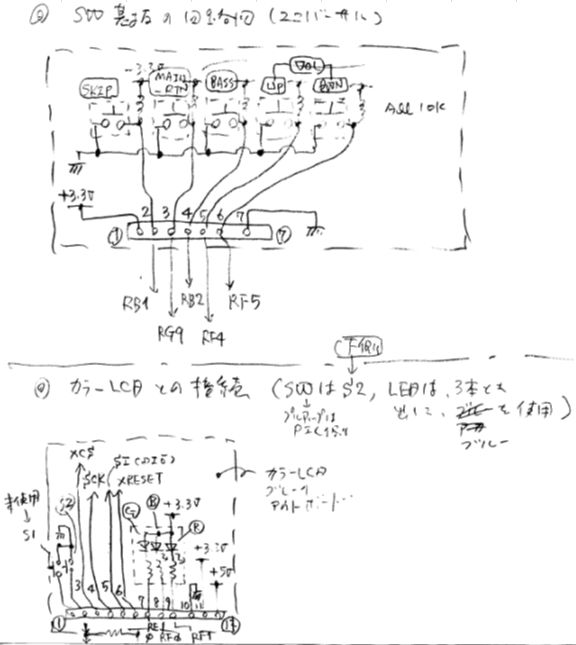

SW基板との接続と、カラーLCDブレイクアウトボードとの接続を考えながら、入力を行う。

下に、手書きの小物の接続図を示す。

<失敗談コメント控え------>

基板(ガーバー)発注後発覚>

※ この、カラーLCDの手書き接続図は、ピン番 対 信号名の対応に間違いないが、実物の、1番ピンの位置は、

表示面を上にして見た時、右側になるので注意が必要である。(この図とは逆になる)

この認識は、ユニバーサル基板での実験の時からあったが、いざメイン基板にコネクタを配置する時、

通常の左から1番の配置にしてしまい、EAGLEでのワイヤリングをしてしまった。

痛恨のミスである。とほほ・・・・

しかも、基板(ガーバー)発注後の、アクリル加工作業の時まで気が付かなかったとは・・・・

この件は、基板側でリワク修正をするには、カット・ストラップの箇所が多過ぎて基板がズタズタになるので

今回は、スマートにケーブル無のスタック接続の構想が実現できなくなるが、ケーブル接続にして、ケーブル

にてテレコ修正することにした。

■ 2013.1.14

・回路図作成完了後、NET/BOMリスト生成

※ EAGLE回路図は、こちらからどうぞ → MP3_PLAYER_BOARD_回路図

(回路図にミスがあり、2点ばかし朱書き修正しました。→ 回路図を置換えました。 2013.2.9)

・NETリストのチェックを行う。

→ 1つだけ異なるNETに繋がっている箇所あり。

それは、IC2-15(TESTピン)が、+3.3Vになっている?

DVDDのはずだが・・・

→ 確かに、そのラインを、infoコマンドで確認するとNET名が、+3.3Vになっている?

→ NAMEコマンドで、NET名をDVDDに修正し、OKになる。

・BOMリストも確認OK(特にシェープ)

■ 2013.1.15

・秋月分のみ部品先行手配済

SW基板製作のため

・ピンソケットコネクタのパッケージのセンターが、ズレテいたのに気が付き修正した。

回路図にもリプレース済

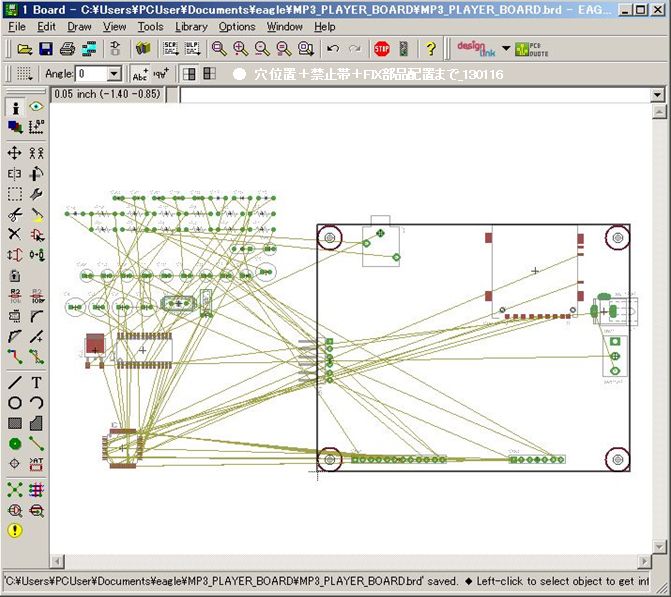

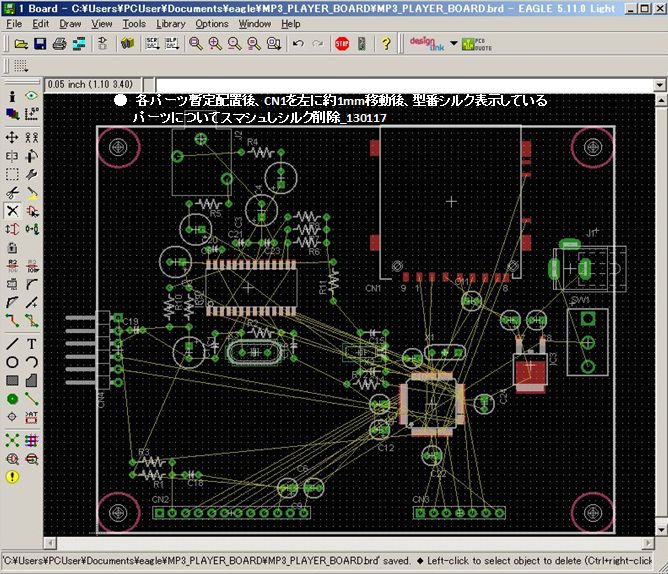

■ 2013.1.16~ 2013.1.17

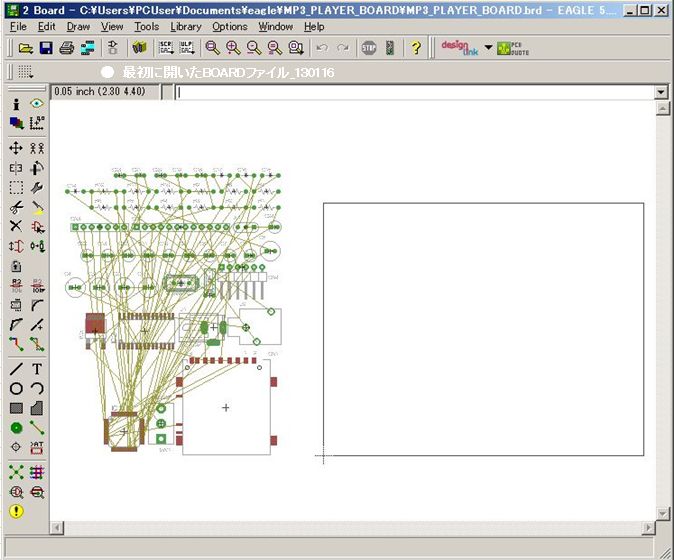

・レイアウトエディタによるパターン配線作業に移った。

まずは、取付け穴と禁止帯の設定~ 主要部品の配置を行った。

2つのソケットコネクタは、前面パネルのカラーLCDボードと、SW基板とのスタック接続になるので正確な

位置決めが必要である。

(・・・と最初は予定していたが、カラーLCDの方はピン番の方向ミスが、ガーバー発注後に発覚してしまったため、こちらだけは

ケーブル接続に、やむなく変更になりましたが・・・)

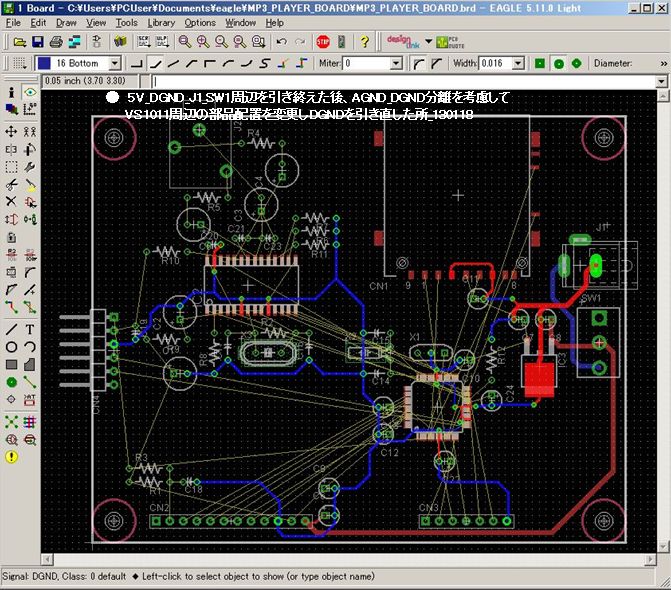

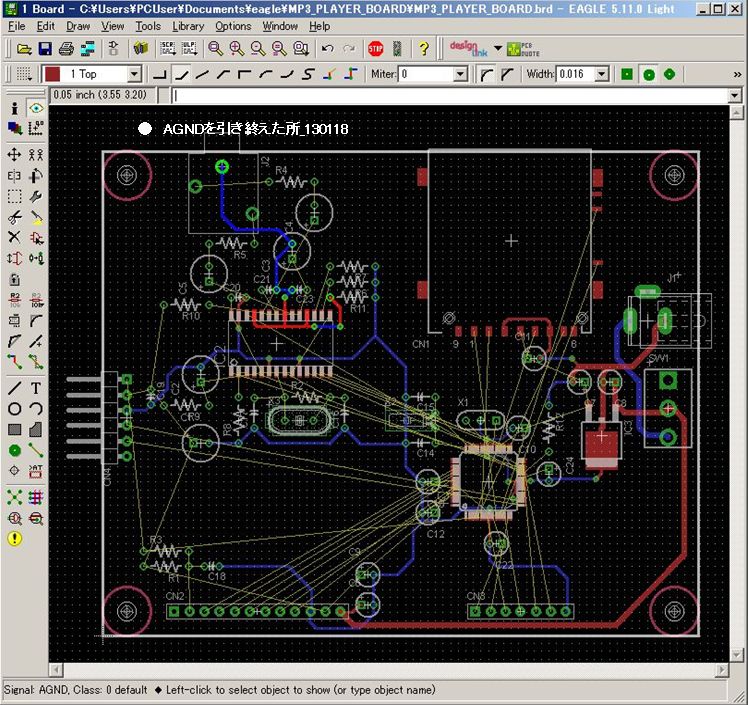

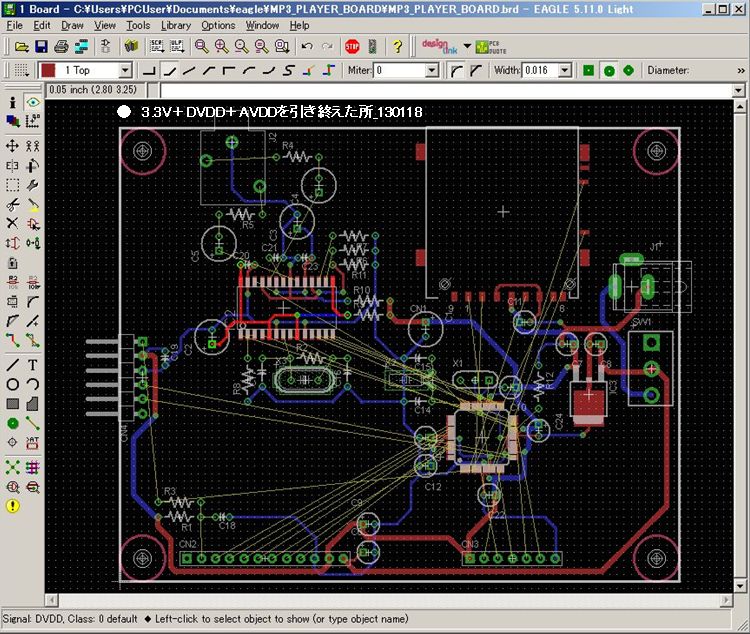

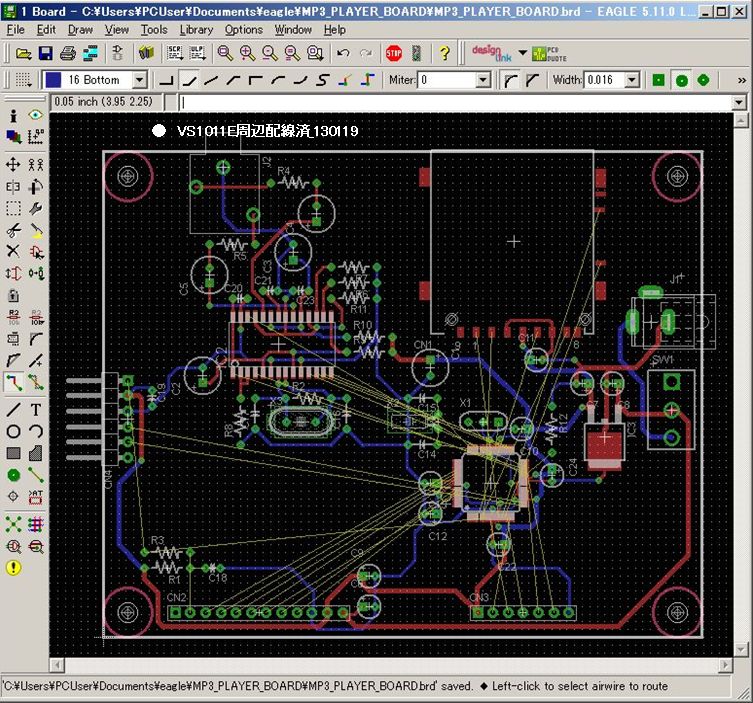

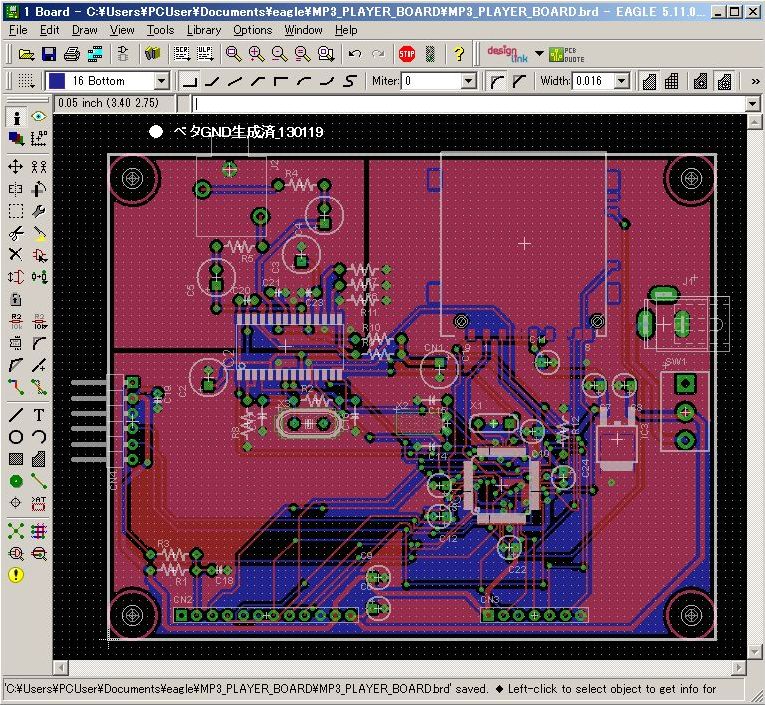

■ 2013.1.18~ 2013.1.19

・電源パターンと、アナログ部のパターンを手引きした。

以下に、その各ステップのスナップショットを示した。

・パターン引きの途中で、不可解な事象発生

ボード上の、カラーLCD用コネクタ:CN2-11pinに供給されている+3.3Vのエアーワイヤが何故か出てこない。

回路上で、ネットをハイライトにしてチェックすると、+3.3Vに繋がっているのに、何故か、当時ネットリストをチェックした時の

ネットリストにもこのネットは出てこない。

(しかし、当初は気が付かなかった・・・ 今頃きずく)

→ 回路上で一度このネットをカットし繋ぎ直したらボード上にもエアーワイヤが現れた。(EAGLEのバグか?)

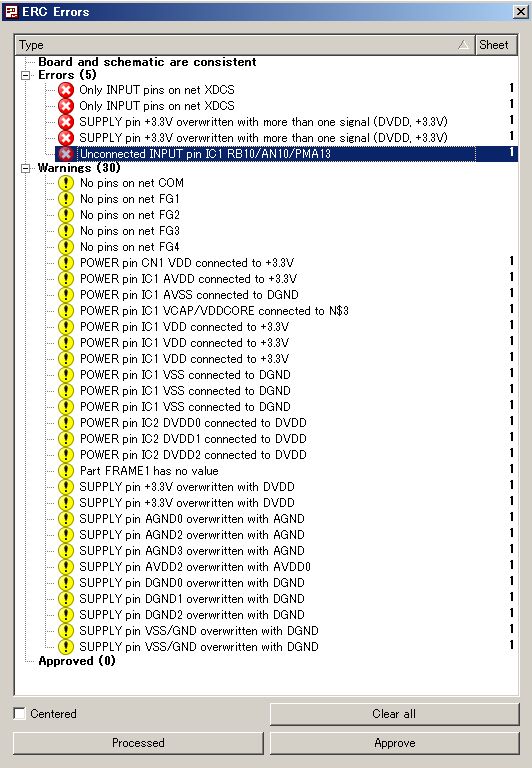

・オートルータを掛ける手前で回路図ネットリストチェック後、ERCをやってないことに気付く。

前回も、そうだったような・・・・

→ 5個のエラーと、30個のワーニングが出たがNETは正常なので、無視しても問題ないと思われるが承認できるか

調べてみることにした。

→ 5個のエラーの内、3個は承認できるエラー

(+3.3Vシンボルを流用してDVDDシンボルとしてネット生成した2点と、MPU-23pinの電気的特性指定を入力としているために

無接続エラーと解釈されている1点。ネットに影響ないので承認できる。)

あと2個は、XDCSの接続で、双方のデバイスの入力ピン同士が接続されている旨のエラーだが、これもMPU側のピンの

電気的特性を入力にしているために起きているだけで、NETには影響ない。

→ 30個のワーニングも全て承認できるので問題ない。

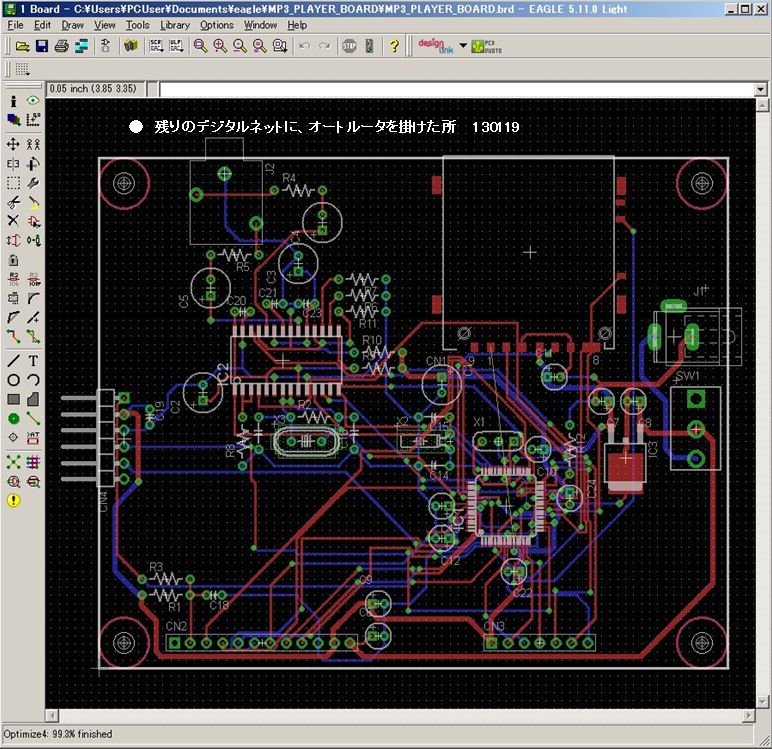

・残ったデジタルネットに、オートルータを掛ける。

1本だけ、未配線が残る。

よくルータ状態を見ると、不自然に引き回している箇所が何箇所もあり、これを手作業で整理することにした。

一部パーツの位置を微調しつつ整理したら、100%ルーティングになる。

・ベタGND設定後、生成済

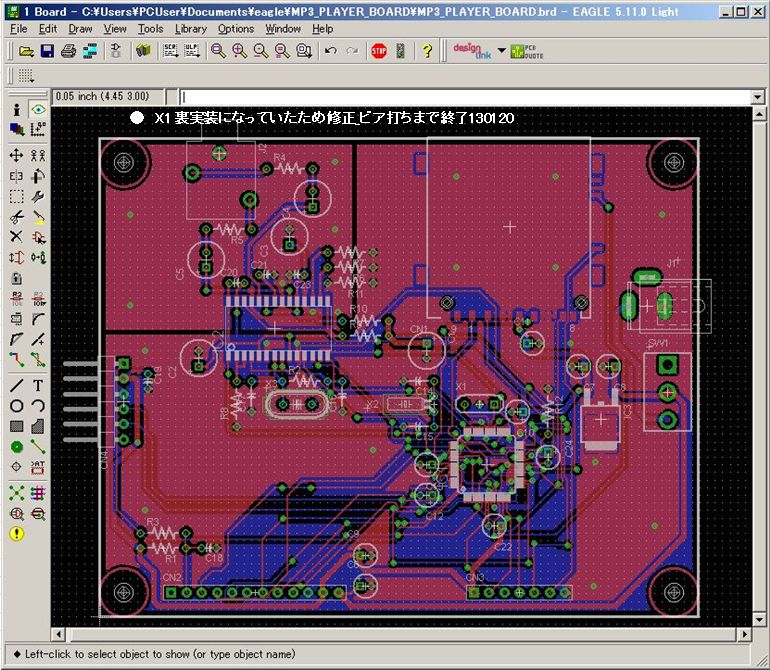

■ 2013.1.20

・ここで、32.768kHzクリスタルの外形シルクが部品面に表示されてないことに気が付く。

→ 部品面シルクレイヤ: 21 tPlaceを表示させないようにしても、当該外形シルクは表示している??

ということは、21t Place以外のレイヤでパッケージが登録されているのでは・・・

→ 何故か、ボード上のinfoコマンドで、この部品の外形シルクを見ると、22

bPlace(ハンダ面シルク)になっていた。

→ ここで、パッケージ登録はどうなっているか確認した。

VT-200-F.pacのシルクデータを見るとボディ部は、ちゃんと、21

tPlaceになっているではないか!!

※ どうも、ボード上でこのパーツを置いた時に、ハンダ面実装として置かれてしまっているようである。

パーツのプロパティを見ると、何故か、Mirrorのチェックボックスにチェックマークが入っていた。

→ チェックマークを外してみた。

→ 部品が180°反転し、部品面シルクの認識になった。

※ ボード上のMirrorは、回路図上のそれとは異なるようでハンダ面実装と解釈されてしまうようである。

そう言えばこの部品を置くとき、向きを配線が素直になる方向に回転させようと思ったが、

この時はMirrorをつかったような・・・・

ボード上でパーツの向きを変える時は、ハンダ面実装でなければローテートで変えないとまずいことが分かった。

→ よって、一度ミラーを外し、ローテートして位置合わせしその部分のパターンを引き直さないといけない。

ローテートに伴い、C14, C15も逆にしないとラインがクロスしてしまうので、結局、C14,

C15のネットも

ディスコネクトするはめになったが、何とか引き直し修復した。

・DGND, AGNDのビア打ちを行う。

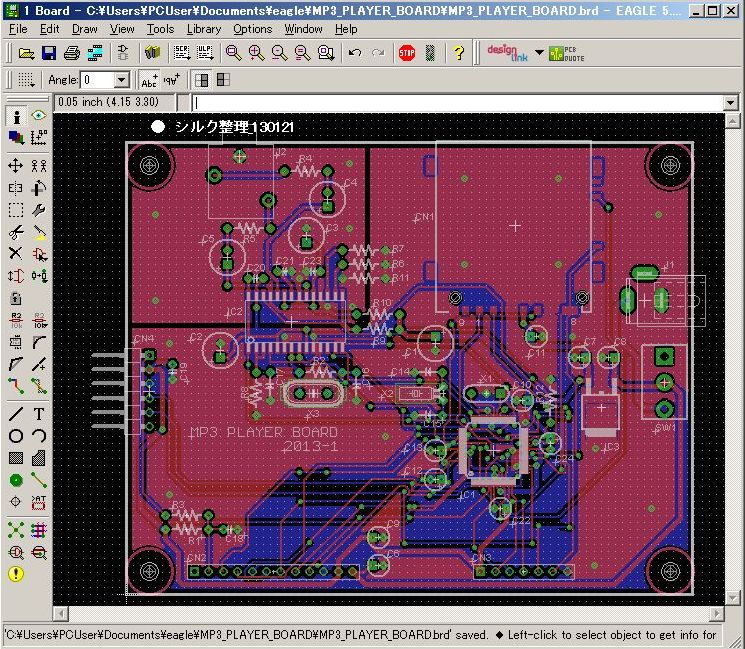

■ 2013.1.21

・シルク整理実施

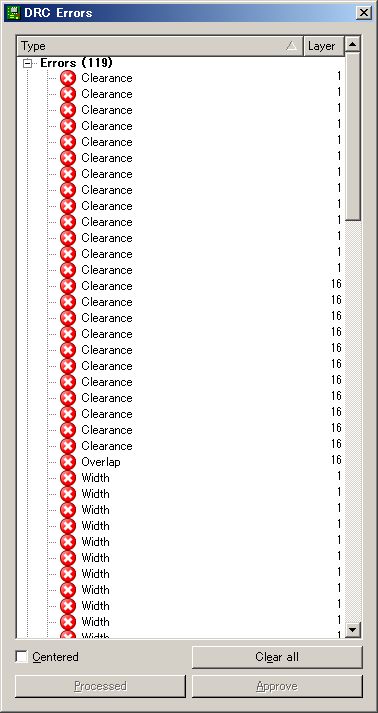

・ボードDRC実施

<主要なDRC条件>

① パターン幅= 0.012inch

② ビア径= 0.016inch

③ クリアランス= 0.005inch

→ DRC結果_1回目

119エラー発生

殆どが、TQFPのpin付近にクリアランスエラーが発生している。

MPUの裏のランドとパッドからのパターン間のクリアランス不足が原因

→ 電源ビア径は、こだわって24mil(0.024inch)でやってきたがクリアランスで引っかかるところを、パターンで引き直すのは

危険なので出来るだけ避け、今回は、パッド径をエラー箇所のみ、16milに変更することにした。

またTQFP64のパッド幅(約0.011inch)に対し、0.012inch幅のパターンで引いている箇所は全て、Withエラーとなっているが

これは許容できるエラーなので、Aopproved(承認)することにした。

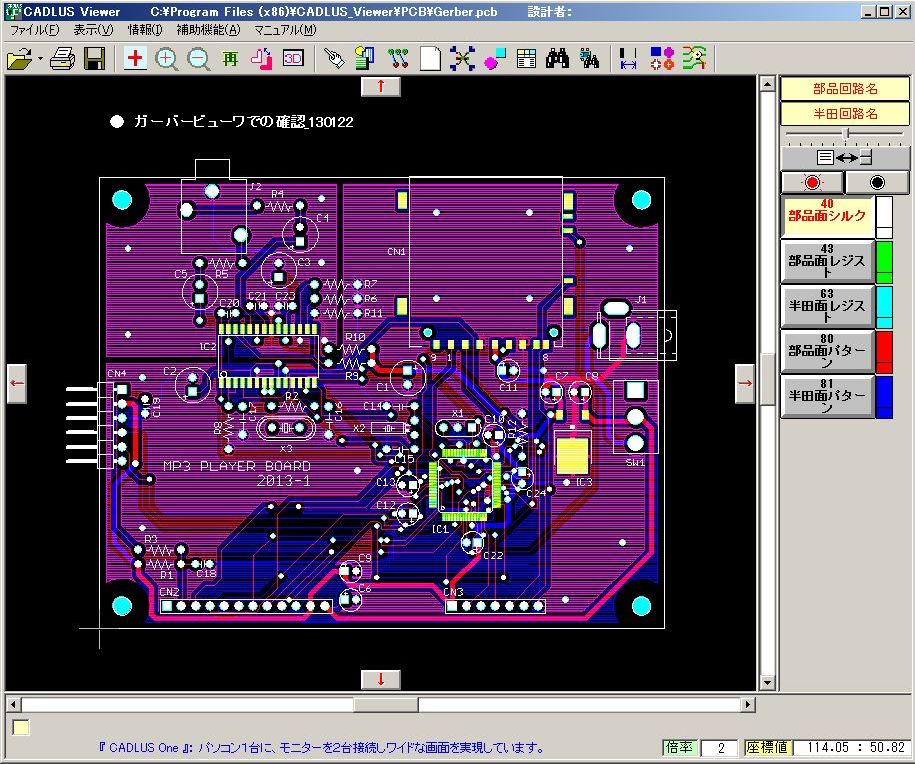

■ 2013.1.22

・ガーバー出力まで済ます。

・ガーバービューワでの確認

良さそうなので、マルツに、ガーバーデータ一式を送付した。

■ 2013.1.23

・マルツ分の部品も手配した。

■ 2013.1.24

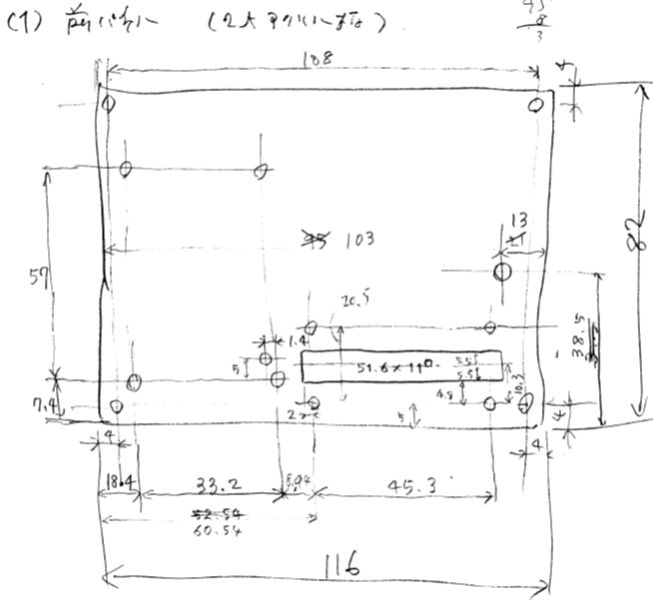

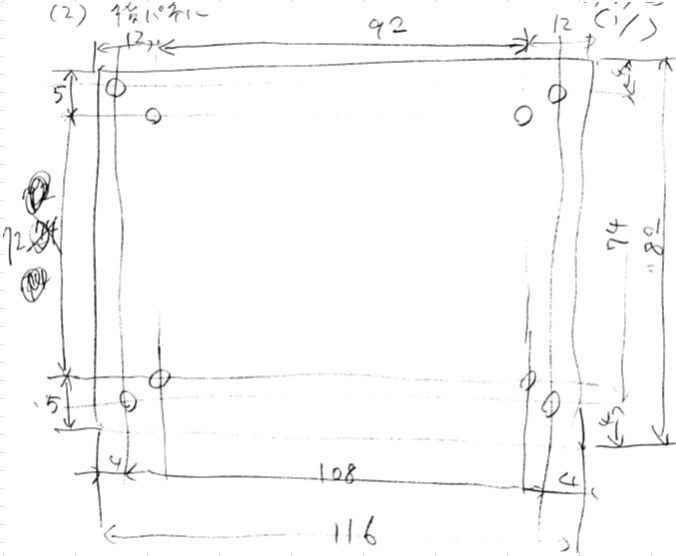

・基板上がりまで約2Wかかるので、その間アクリル板の加工等、進めることにした。

下に、手書きでの、ラフ加工寸法図を示す。

■ 2013.1.25

・アクリル板の加工を行う。

116×82に、2枚カット

寸法線を罫書き、穴加工を始める。

アクリル板の穴加工は注意が必要

普通の金属用のドリルでは、食いつきが問題になり、明けぬく寸前でアクリルにヒビが入ることがある。

現に今回も、コーナー付近の取付け穴を加工時、失敗して角を割ってやり直すはめになった。

グラインダーなどで、刃先を整形する旨の説明がWEB上にあったが、設備がない

(電動ドリルさえなくハンドドリルでやってる位なので・・・)

ので、私は普通の金属用のドリルで慎重に

加工するのみである。

・この作業の途中で、前に書いた、「カラーLCDコネクタのピン番ミス」が発覚し、急遽、ケーブルでのテレコ修正に

変更することになる。

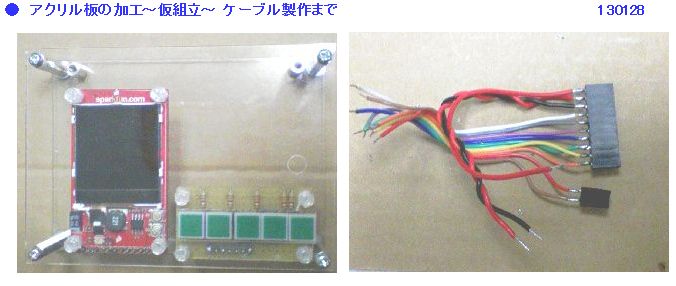

■ 2013.1.28

・アクリル板の加工~ スタッド加工~ 仮組立~ ケーブル作成まで終了

・マルツに、TQFP64パッケージICの実装依頼を出す。

実装上がりは、2月上旬予定

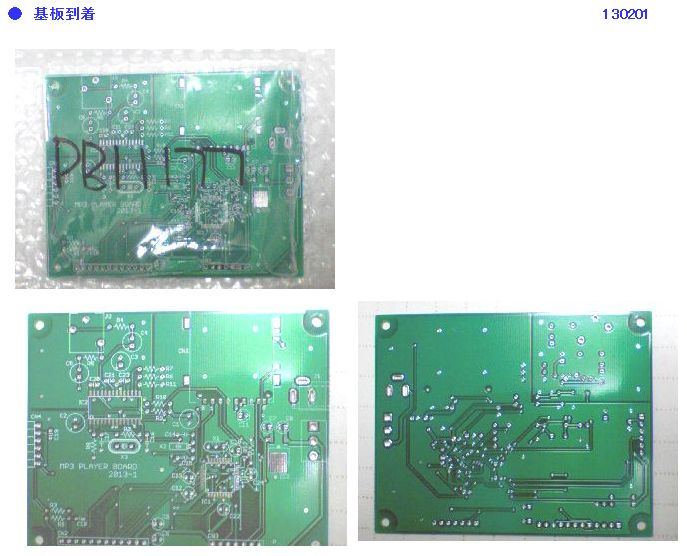

■ 2013.2.1

・予定より1日遅れでようやく基板が到着!!

2枚発注したが、内1枚は、TQFP64パケージICの実装を、お願いしているので今日届いたのは1枚のみ

■ 2013.2.6

・やっとマルツに依頼していたTQFP64_IC(PIC32MX)の実装が上がり、実装済みの基板が到着しました。

こらからゆっくりと他部品の実装に入ります。

・実装前に電源パターンのショートチェックを行う。

→ +5V⇔DGND/ +3.3V⇔DGND/ AGND⇔DGND(一点アースポイント:実装時ここをショート)

各信号間ショートしていないことをテスターにて確認した。

→ これをやろうとした時、次のことに気が付く。

+5Vネットに繋がっているパスコンで、回路上は、C6(IC3-1pin)とC8(CN2-12pin)だが、

シルクを見ると、IC3-1pin側のパスコンがC8になっていて、CN2-12pin側のパスコンが

C6になっていた。

→ ネットに問題ないので動作には影響ないが、部品を置く時に逆にして置いてしまったようで・・・

このようなこともあるので、今後注意が必要である。

(シルクから見ると回路上のミスのように見えますが、実際はボード上で部品を置く時のミスです。他のシルクはOK)

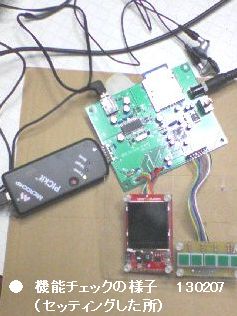

■ 2013.2.7

・部品実装が全て完了した。

<実装後のチェック>

① 電源ショートチェック

+3.3V⇔DGND, AGND→ OK

+5.0V⇔DGND→ OK

② 電源電圧チェック(全てカラー液晶実装時の電圧を示す)

+3.3V→ 3.28V

+5.0V→ 5.08V

VS1011e-AVDD→ 3.28V

VS1011e-DVDD→ 3.28V

③ HEX書込み

問題なく書込めた。

④ 機能チェック

→ 電源ONで、オープニングBMP表示した。

とりあえずは、プログラムRUNしている。

→ しかし、LEDがイニシャルで点灯している。?

→ これは当然

トレーニング基板のLEDはカソードコモンだったが、今回のハードはのLEDはアノードコモン

ここだけプログラムの変更が必要あり

→ プロジェクトを新たに作るまでもないので、トレーニング基板使用のMP3プロジェクトのソース

コメントアウトにて対応することにした。

→ ソフト変更後、HEX書き直し動作確認

① 電源ONで、LED全て消灯した。

② また、オープニングイメージ表示の途中で、カラー液晶内蔵のS2(リセット)SWを押すと

リセット効いている。

③ カード未挿入時のメッセージ表示もOK

→ だが、ここでおかしい・・・

カードを入れて電源ON

最初の曲をサーチして、曲名/アーティスト名表示するが、再生始まらず、直ぐにカード挿入待ち

に戻ってしまう??

<調査>

① トレーニング基板で動いていたHEXのまま書込んでやっても同じ症状

プログラム修正時のミスではないことがはっきりした。

② SDカードの挿入検知が、あやしいのでカードスロットのメカ接点部の配線を疑った。

何気なく回路図を見ていたら気が付いた!!

→ 回路図にミスあり!!

挿入検知接点のコモンが、DGNDに接続されてなかった。

→ パターン修正を行う。

目立たないように、COMピン近くのベタGNDレジストを削りそこに、短いリード線で

ストラップ修正した。

→ これで大方、機能はOKになる。

(再生時間表示もLEDの点滅表示も問題なし)

・一応動いてはいるが、

SDカードのメカ接点入力(CD/とWE/)のMPU側での内部プルアップ設定が、後閑さんのオリジナル

プログラムからして、されてないことに気が付いた。

そのため例えば、カード未挿入時のレベルがテスターで見ると、0V付近になっている。(フローティング)

それでもなんとか挿入判別はしているようであるが・・・

→ 後閑さんのオリジナルソースを見ると、CNピンでプルアップ設定しているのは、CN2(ロータリーSW)

だけで、他はしていない。

→ CN5(CD/)とCN6(WE/)は、プルアップ有の設定に修正した。

→ 修正によって、メカ接点オープン時、Hiレベルを確認した。

・再生中の電圧確認

+3.3V→ 3.28V/ +5V→ 5.03V(電圧は落ちていない。)

・低音ブーストレベル調整も効いている。

・オーディオ出力の左右位相も正しいことを、オーディオテクニカのチェック用音源にて確認した。

・ちょっと気になる点が1点だけある。

→ トレーニング基板による実験の時はヘッドフォンでモニタしなかったせいか気が付かなかったが

電源を入れて最初の曲を再生する直前で、ブツ音(ノイズ)が一瞬入る。

ただこれは曲間では入らない。最初だけである。

ちなみに、今まで製作した2台のプレーヤは、このようなことは起こらない。

ソフト上の問題なのか?

明日に続く。

■ 2013.2.8

・まず、トレーニング基板で実験時の環境でやっても

電源ON後の最初の再生直前にブツ音が発生することを確認した。

またSKIP_SWの送りによる再生でも、何もSWを押さない通常の曲間のブツ音は発生しない。

・テスターでブツ音が発生した瞬間にVCCがダウンしてないか確認

→ 全くダウンしてない。

念のため自作オシロでも確認したが、一瞬のディップも見られなかった。

→ どうもソフトが悪い可能性が大きくなった。

・そこで、現状のハード環境に戻し調査を続行した。

プログラムのどこを実行した瞬間に、ブツ音が発生しているのかを確認するため

可能性のある所で、プログラムを止めそこでブツ音が発生するか否かを確かめることにした。

→ 一番くさいのは、VS1011eの初期化ルーチンである。

この中で最初に、SPIの初期設定をしている所である。

→ VS1011eにソフト・リセットを掛けその間に

次に示す5行(コメント行除く)で、SPIの初期設定をしているのだが、設定が終了して、

次にソフト・リセットを解除する手前でブレイクしてみてもそこでは未だブツ音は発生しない。

/***** SPI2の初期設定 ***/

MP3_SPICON1 = 0x8120; // 8ビットモード,CKP = 0,CLK=Fosc/4 (4MHz)

// 中央でサンプル(SMP=0) 立上りエッジで送信(CKE=1)

// フレームモードなし

SPI1BRG = 0x000F; // 約2.5Mbps

MP3_SPI_IF = 0; // 割り込みフラグクリア

/* RESET解除、VS1011スタート */

delay_ms(50); // 50msec delay

MP3_XRESET_IO = 1; // RESET解除

※ 結局、ソフト・リセット解除直後にブレイクしてみると、そこでブツ音が発生していることが解った。

未だVS1011e側のバッファには何のデータも送っていないはずであるが

SPIのハード仕様/ボーレートクロックの設定が有効になった直後にDAC入力にゴミデータ

が出力されてしまうのか・・と勝手に想像してしまうが、現にここでブツ音が発生している。

→ 今迄製作してきた2台のプレーヤと、今回製作したプレーヤの大きな違いは、前作はRTOSを使用

しない通常のプログラム、今回のはRTOSでプログラムを記述している点である。

→ 両者の、VS1011e初期化関数を実行している場所を比較してみると以下の違いがある。

① 前作はメインループの前でいち早くVS1011e初期化関数を実行している。

② 今回のは、RTOSで記述しているせいか、完全タスク分けを意識してか、VS1011eに関する

初期化処理は、task3.cの中の、whileループの前で行っている。

→ VS1011eのDACアンプの特性なのか、電源ON瞬間のブツ音発生はオーディオ出力回路に

ミューティング回路を追加するなどしないと避けられないようだが(現にこれは両者共に起こる)

今回のプレーヤはその電源ON直後に発生するブツ音と、SDからの最初の曲データをカラー液晶に表示後

タスク3に処理が移り、その頭でVS1011e初期化を実行しているために、ここでも最初の曲再生直前に

ブツ音が発生するため気になると思われる。

一方、前作のはメインループ前でいち早くVS1011eの初期化を実行しているため、電源ON直後の

ブツ音と重なって目立たなくなっているものと考える。

→ 結局、タスク3の頭で実行している、VS1011eの初期化と、音量+低音ブースト等の初期設定を

メイン関数内のメインループの前で実行するようにしたら見事、最初の曲再生直前のブツ音は発生しなくなった。

■ 2013.2.9

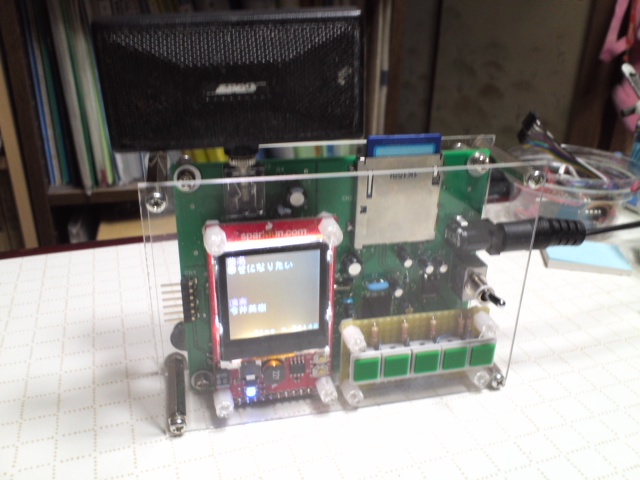

・バラックで機能を含め、細かい問題まで何とか解決したので、全体を組立ててこのプロジェクトは終了である。

これをデスクトップの片隅に縦置きして暫く使ってみることにします。

← 実験テーマ1に戻る TOP PAGEに戻る 実験テーマ27へ →