(追加機能(Soft Ver1.02) デバッグ記)

● 実験テーマ15

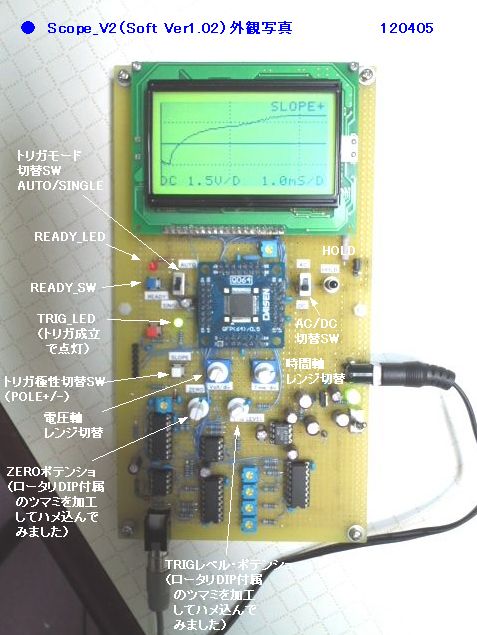

「自作オシロのバージョン・アップ:第3章」

※ 131126

一部修正更新

(追加機能(Soft

Ver1.02) デバッグ記)

■ 2012.03.23

・今日から、「Soft Ver1.02」のデバッグを開始した。

・2つの追加機能があるが、最初は1つに絞って進める。

・HOLD機能のフローイメージを考える。

(HOLD_SWが押されたら、"HOLD"表示し、その時の波形表示を保持する機能がHOLD機能)

・最初は、HOLD_SW(モーメンタリ)の立下りエッジセンスを、CN割込みを使わず、メインループの頭でエッジセンス

シーケンスを作り、そこでリードすることにした。(DMA割込みとの干渉が心配だったため。)

・とりあえず、思いつくまま、HOLD機能のみ盛り込んだソースを書き終えた。

・コンパイルは一発でOK。

一応、HOLD→RUNするが、時間軸が途中でおかしくなる。

(2mS/Dの次が、5mS/Dでなく50mS/Dになってしまう。またこの時2mS/Dに戻しても50mS/Dのままになる。)

■ 2012.03.24

・原因判明

何と今回もボンミスであった。

GLCDライブラリ・ソースが最新版でなかった。

(例の、lcd_Readルーチンのバス方向切替部の修正をしてないファイルを使っていた。)

・この修正を施し一応動くようになったが、SWの読込みが予想はしていたものの鈍い→ 改善しないと・・・

メインループでSWを読込む方式には無理がありそう。

・メインでSWを読込む方式はやめ、CN割込みでやってみることにした。

→ これをやるには、CNEN1レジスタを設定し、CNで使う入力ポートビットを有効化する必要がある。

■ 2012.03.25

・CN割込みを使った方式に変更

① CNEN1,2レジスタの設定

② 割込みプライオリティレジスタの設定

③ CN割込みルーチンの記述

基本的には、これだけでよいはず。

(CN割込みとは、エッジセンスをPIC内のハードウエア(FFとXOR構成)で実現するものと考えられる。)

→ 一応ソフトを変更しコンパイルOK

・しかし上手く行かない。CN割込みの動きが変??

→ 割込み優先順位設定等、設定を再確認してみることにする。

・HOLD機能まとまる

① HOLD ON→ OFFのオルタネート記述が適当でなかった。

→ SWを押した回数を判断してオルタネート動作としていたが、これでは、CN割込みが無条件で入ってしまう

のでNG

→ 1度HOLDループに入ったら、hold_statusフラグをセットして、CN割込みルーチンの中で、そのフラグを見

てセットされていたら、HOLD_ON_flagを、0にリセットすることにした。

② 割込み優先順位の設定がまずかった。(直接動作には関係ないようだが・・)

→ DMA5: 4(デフォルト)------------> 優先順位:高い

CN: 3に変更(6から3に変更)----> 優先順位:低い

③ HOLD_SWに、手持ちのジャンク品を使ったせいか、メカ接点のチャタリングが多いようで、リードまでの安全

時間を、1mSから、10mSに変更したらよくなった。

■ 2012.03.26

・今日から、SINGLE TRIGGER機能を検討

<SINGLE TRIGGER機能仕様案>

① トリガ・モード切替SWが、SINGLEになっている時、次のシングル・トリガ動作となる。

② 現在の波形表示をクリア

③ READY SWを押すと、画面上部に、"WAITING FOR TRIG"を表示しトリガ成立待ちにする。

④ 信号を入力しトリガが成立すれば、"WAITING FOR TRIG"の表示を消し1画面分の波形を表示する。

⑤ もう1度、READY SWを押すと、②に戻り繰り返す。

⑥ 操作の途中で、トリガ・モード切替SWを、AUTOにすると、AUTOトリガに戻る。

・以上の仕様に基ずきフローを検討

AUTOモードのケースと、SINGLEモードのケースに分けて考えることにした。

■ 2012.03.27

・SINGLE TRIGGER機能部のコーディングが終了した。

・コンパイルは一発でOK

<動作確認>

① AUTOトリガモード時は、HOLDも含めOK

② SINGLEモードに切替えておいて、電源をONすると、初期メッセージ後のXY軸表示が出てこなく止まってしまう。

→ この原因は何てこと無かった。

AUTOモードの場合は、1画面分のデータ取得後にオシロ画面(XY軸とレンジ表示と波形表示)を行っているが、

SINGLEモードの場合は、READY SWが押されるまでは、ループ待ちになるので、その前で表示を行わないと

止まっているように見えていただけで、修正でOKになる。

・修正でらしくはなってきたがまだまだ・・・・

① オシロに入力を入れないでREADY SW ON→ WAITメッセージ表示。ここまではOK

② ここで信号入力して、トリガが成立し、WAITメッセージ消えるが、波形も、一瞬表示して消えてしまう。

→ 再READY待ちの前に、XY軸表示を入れたが、ここでも画面クリアをしていたので当然の話

(あまり考えずフローを書いたのがアダになってる・・)

・そこで、次のように仕様を1部変更して対処しようと考えた。

→ SINGLEモードに切替えたら、画面上部に、SINGLEモードだと明示するメッセージを出し、READT SW ON待ちに

する。(ここではまだ、XY軸は表示しない。)

① READY SWが押されたらサンプルを開始

② 192データサンプルが終了したらEOCを立てる。

③ この後でXY軸表示する。

④ そして波形表示する。

⑤ 再READY待ちになると、再び、SINGLEモードメッセージを表示する。

・信号入力無しだと、トリガ成立しないので、WAIT表示のまま待つつもりだったが、フローの関係で、WAIT表示と、画面

クリアを繰り返すことになりディレイをはさまないと、WAIT表示が消えて見えるので、WAIT表示の後に、0.5秒のディレイ

を挿入した。

これにより、メインループの終りにも、0.5秒の表示インターバルを入れてあるので、期せずして、WAITのブリンク表示に

なり都合がよい。

→ このまま仕様にすることにした。

(このようにこの時点では、思っていたが、今考えれば、このような行き当たり的な対処の方法では後で破綻を

きたすことになる・・・・)

・だが、ここで別の問題が発生

1度シングルトリガが成立し表示がホールドした時に、AUTOに切替えても、止まったままになってしまう。

→ これの原因と対処は、以下の通リである。

トリガ成立条件で、波形表示した後、再びREADY待ちループで待ちになっているため、このループ脱出の条件として、

シングルトリガ時の、トリガ成立フラグを追加する必要がある。

・修正し、一応、形的にはよくなったが、よくチェックしてみると連続した波形に対しては、連続した波形のどこか最初のトリガ

点でトリガが掛かるが、単発で変化する波形に対してはトリガが掛からない。

(基本的にシングルトリガになっていない。)

→ 入力を入れるタイミングが、T3_ON(ADC開始)と非同期なのが、問題と思われる。

■ 2012.03.28

・READY SWを押した時の、WAIT表示のさせ方が問題になっていると思われる。

→ 現在、WAIT表示後に0.5秒の遅延を入れその後、ADCスタートを掛けているため、数10mS~100mS程度のトランジェント

は見られないことになる。

<対処法案>

① ADCスタート前の0.5秒の遅延はやめる。

WAITのブリンク表示もやめる。

そもそも最初の予定では、トリガ成立まではWAIT表示のままであった。

② XY軸+レンジ表示関数の中で一括表示させるようにする。

・①の対処をやっても、単発信号に対してトリガが成立しない。

(ターゲットは以前製作したMP3プレーヤを使い、3.3V電源の立ち上がりを確認)

■ 2012.03.29

・どうにも判らないが、シングルトリガ調査続行

・シングルトリガ時は、1回のトリガ成立で1画面分表示しSTOPするので、1画面表示毎の、0.5秒遅延もやめることにした。

そうすれば、非同期でもトリガが掛かりやすくなると思った。(確率が上がる。)

<結果>

① なかなかトリガが掛からない。

② 遅延を無くしたせいか、READY待ちの時に、レンジ表示などの文字が薄くなる。

③ ただ次の写真に示す条件の時、ターゲットの3.3V電源の立上がりがシングルトリガで確認できた。

・さてトリガが、かなり掛かりにくい問題をどうするか?

明日に続く。

■ 2012.03.30

・READY待ちの時に、WAIT表示が薄くなるのは、シングルモード時は、出来るだけ頻繁に、ADCサンプルを実行して入力

信号の立上がりに、トリガを掛けやすくするため、再波形描画後の、0.5秒インターバルをやめているので、WAIT表示→

画面クリアが頻繁に起き薄くなると考えられる。

→ これの対策としては、波形描画エリアとテキスト描画エリアを全く別にすることだが、今は画面デザインの関係で

このレイアウトにしているし、画面一杯に波形を表示することも前提としているので変更したくない。

→ それでは、どうするか?

READY状態の表示は、GLCD上でなく、単純にLEDに置き換えてみる。

そうすれば、画面クリアとの関係が無くなる。

またこれの別効果として、シングルトリガ待ち処理ループ中に、GLCD

へのメッセージ出力が無くなるので、より頻繁

にADCサンプルの繰返しが可能になり、トリガが掛かる確率が増えると思われる。

<結果>

① WAIT表示は無関係になるが、レンジ表示も同じく薄くなる。(これは、現状のやり方では仕方が無い。)

② トリガの掛かりやすさは、さほど差が無い。(殆ど効果なし。)

■ 2012.03.31

・さてかなり行き詰まってきた。

シングルトリガのアルゴリズムを変えるしかないか??

現状、判っていることは、トリガ不成立の場合、余分な処理をやめ、出来る限り、高速にADCサンプルを繰返すようにすれば、

トリガ成立の確率が上がる傾向にあるという点である。

■ 2012.04.01

・ADCサンプル繰返しの、高速化のため、シングルトリガの仕様を次のように変更してみたらどうか??・・と思いついた。

① シングルトリガ時は、レンジ切替SW(VSWと、TSW)の読込みは、行わない。

→ シングルモード時のレンジ切替は無効という仕様にする。

(AUTOモードのレンジでシングルトリガを実行と考える。)

② シングルトリガ不成立の場合、レンジ表示等の再表示及び、波形のクリアは行わない。

→ 再トリガ待ちの時、前の波形が残ってしまうが、トリガが成立した時点で、再描画するので良しとする。

またこうすれば、レンジ表示が薄くなる現象もなくなる。

・このようにソースを変更した結果、だいぶトリガ成立の確率が上がったので、これで一応OKとした。(ちょっと、甘いかな・・)

■ 2012.04.02

・そろそろまとめとは、思ったものの、ここで欲が出た。

やはり、スロープ切替SWを追加して、立下りトリガも取れるようにしようと・・・

(SWも何とか、手持ちがあるし)

<スロープ切替機能仕様概要>

① プッシュSWで、押す度に、POS/NEGトリガ切り替えを繰返す。

② GLCDに、切替に応じ、"SLOPE+"または、"SLOPE-"と表示する。

<ハード上の変更点>

① RB1(CN3)ポート(15pin)に、SLOPE_SWを追加する。

→ これに伴う、TRISBの設定は、0x00FFのまま変更なし。

これに伴い、CNPU1の設定を、0x0FE3→ 0x0FEBに変更

<ソフト上の変更点>

① デファインの追加

#define SLOPE_SW PORTBbits.RB1

② 変数追加とイニシャル

char POS_flag = 1; // Defult Trigger Slope is positive

③ CN割込みルーチンの中に、SLOPE_SWの処理を追加

if (!SLOPE_SW) {

if (POS_flag) POS_flag = 0;

else POS_flag = 1;

}

④ Oscillo()及び、Oscillo_single_trigger()関数内のトリガ成立条件を、POSとNEGで切替えるように変更

/* Check Trigger */

if (POS_flag) {

while((x < 128) && !((Buffer1[x]<POT) && (Buffer1[x+1]>=POT))){

x++;

}

}

else { // Trigger Slope is negative

while((x < 128) && !((Buffer1[x+1]<POT) && (Buffer1[x]>=POT))){

x++;

}

}

⑤ GLCD上に、スロープステータスの表示を追加

/* Disp.SLOPE */

if (POS_flag == 1) lcd_Str(0,11,"SLOPE+");

else lcd_Str(0,11,"SLOPE-");

・SLOPE_SW 追加のデバッグ開始

・まず、次の不具合発生

① AUTOモードにて、"SLOPE+"表示しているが、SLOPE_SWを押しても表示が、"SLOPE-"にならず。

→ RB1ポートは、H→ Lの変化になっている。しかし、CN割込みに入らず。

(CN割込みルーチンの頭で、ブレークして確認)

② 何故か、何もSWをONしてないのに、電源ONしただけで、CN割込みに入ってしまうことがある。

<原因判明>

あせってコーディングしたせいか、次の設定が抜けていた。

① AN0(RB0), AN1(RB1), AN2(RB2)までアナログ入力設定のままになっていた。

つまり以下の変更が必要

AD1PCFGL = 0xFFF8;→ AD1PCFGL = 0xFFFA;に変更(RB1はデジタル入力)

② CNEN1の設定変更が必要である。

CNEN1 = 0x0001;→ CNEN1 = 0x0009;

・しかし、これらを修正変更しても駄目で、電源ONしただけで、RB1(CN3)の割込みが入ってしまう??

(ノイズの疑いがある。)

・アナログ兼用のデジタル入力は、ノイズに弱いのか??

そこで、純粋なデジタル入力ポート(CN*)に変更してみることにした。

<検討>

① CNポートとして使える純粋なデジタル入力ポートの残空きポートは以下の、2つしかない。

→ RD6(CN15), RD7(CN16)

→ SLOPE_SWと、PIC_ポート間の配線長が短い、RD7を使うことにした。

<これに伴うプログラム変更要点>

① #define SLOPE_SW PORTDbits.RD7

② AD1PCFGL = 0xFFF8; // AN0-2 are Analog

③ CNEN1 = 0x0001; // Valid CN0: READY_SW

④ CNEN2 = 0x0003; // Valid CN17: HOLD_RUN_SW, CN16: SLOPE_SW

⑤ CNPU1 = 0x0FE3; // RB3-5, RC13,14, RG6-9 is pull up

⑥ CNPU2 = 0x0007; // RF4,5, RD7 is pull up

・これらの修正変更で、SLOPE_SWによるトリガ極性切替機能は、OKになる。

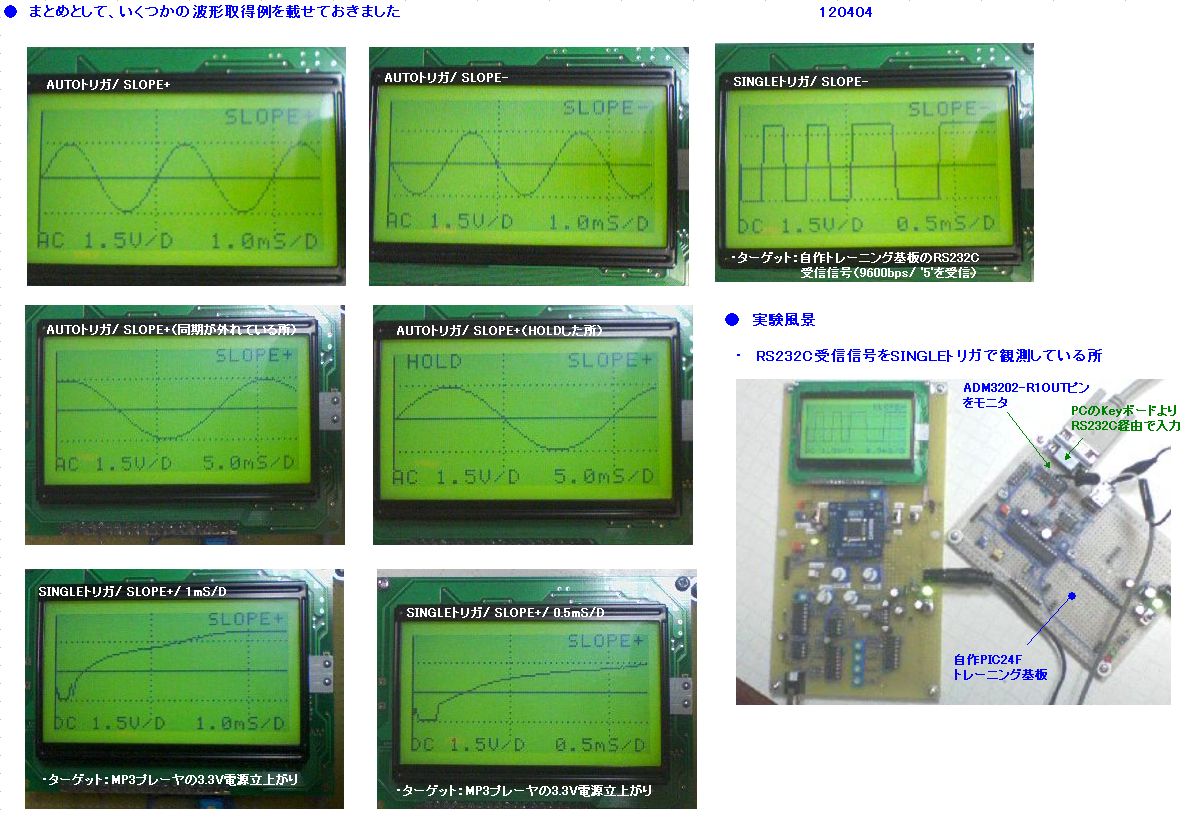

■ 2012.04.03

・これで妥協した点もあるが、何とか考えていた機能追加が実現できたので、今日は、まとめとして、いくつかのモードで波形

取りをしてみた。

<最終回路図>

・こちらから、どうぞ→ 「PIC_オシロスコープ_V2(Soft

Ver1.02) 回路図」

・131126

修正更新→ 「PIC_オシロスコープ_V2(Soft Ver1.02)_回路図」の一部を修正し、置換えました。

その背景・理由については、実験テーマ36の、冒頭(2013.7.30)の朱書きコメント

を、参照してください。

<最終ソース>

・こちらから、どうぞ→ Scope_V2_Soft_Ver102.c

← 実験テーマ1に戻る TOP PAGEに戻る 実験テーマ16へ →