|

PSM1(開発終了)

初めて作ったCPUです。RISC風の命令セットを1命令あたり4サイクルで実行する設計でした。この頃は、とにかく動くCPUを作ってみたい一心で、難易度の高いパイプライン化は避けています。 このPSM1に関しては、RTLシミュレーションで簡単な動作確認した所までで開発を終了しています。ちなみに、Processor

Study M odel

の頭文字をとってPSM

です。”習作”的なニュアンスで名付けています。(英語的に正しいかどうかは不明) |

|

PSM2(開発終了)

1作目(PSM1)をパイプライン化することを目標に開発を開始しました。 ただ当時は、パイプラインをどう制御すればよいか(特に割込みやデバッガからのRUN/STOP/STEP実行制御時など)なかなか良いアイデアが思いつかず、結局パイプライン1ステージあたり2サイクルで処理する3段パイプラインという、へんてこな仕様で作りこんでいます。下図のような感じです。我ながら”とほほ”な感じです。とりあえずSpartan3スターターキットで簡単な動作確認をしたところまでやって、PSM3へ移行。

|

|

PSM3D(開発終了)

PSM2での経験を生かしつつ、

な感じのパイプラインプロセッサを作りました。

あまり意味なくDualコアだったりします。

Spartan3Eスターターキットにてキャッシュ込みで70MHz動作。

C#で作った超手抜きデバッガあり。

自作Cコンパイラに初挑戦! ど素人が無謀にもyacc/lex使わずにフルスクラッチしたあげく、ぐだぐだな物になってしまいましたが、

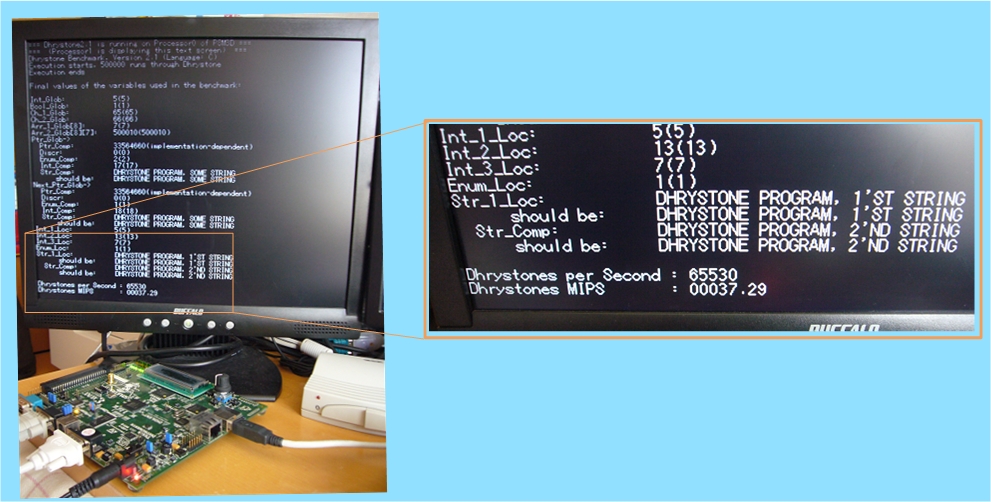

Dhrystone2.1ベンチマークで現状37.05DMIPS(0.529DMIPS/MHz)です。

PSM3D関連のソースやドキュメントなどはこちら

コンパイラ開発に関する別室をオープンしました

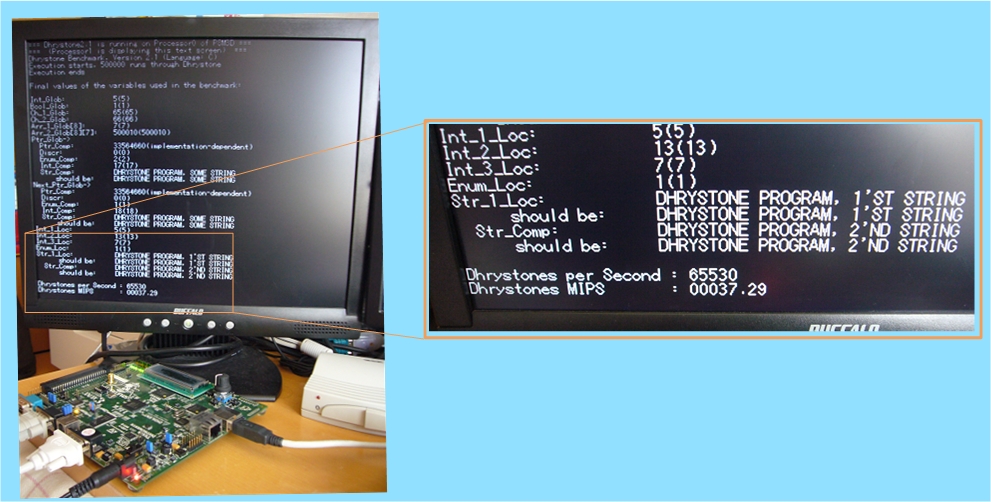

この写真は自作のCコンパイラでコンパイルしたDhrystone2.1をプロセッサ0で実行し、結果をテキスト化してデータバッファへ書き込み、

プロセッサ1で、上記のテキストデータバッファの内容をビットマップフォントに展開してフレームメモリへ書き込んで、ディスプレイに表示させてる所です。 |

|

PSM4(開発着手)

稚拙ながらPSM3向けにCコンパイラを作ってみて、いろいろ勉強できました。というか、PSM3のダメな所がいろいろ見えてきて、最初から作り直したい欲求が溜まってます。 また、コンパイラも初心者の1発めということで、こちらは最初から捨てるつもりで作っており、もう少し"まし"なものにしたい気持ちが強いです。 というわけで、PSM4では、今までの経験を生かして、ハード(命令セットやパイプライン構成)、ソフト(コンパイラ&デバッガなど)共に、ゼロから設計しなおす計画です。

|