�g�c�����������@�t�������@�������@�r�s�`�w�@�d���������������������@���@�r���������@����@���̂R�h�@�͂�����

�g�c�����������@�t�������@�������@�r�s�`�w�@�d���������������������@���@�r���������@����@���̂S�h�@�͂�����

| �E�O��̂r���������Ő��삵��C�Ăɂ��䂪�c�����������@�t�������@�������@�r�s�`�w�@�d���������������������͂��̌�������ɓ��삵�A�ǂ��������Ă���Ă���B �E���̌�A�_�C�i�~�b�N�^�w�b�h�t�H���p�̃w�b�h�t�H���A���v�������������Ƃ�����A������A�i�L����Ёj�r�s�`�w�����L���������Ă�������C���[�X�s�[�J�[�p�̐ڑ��R�l�N�^�r�q�b�|�T�o�̎c��P�����݂Ȃ��ɓ]�����Ă���̂�ڂɂ��āA���낻���c�����������@�t�������@�������@�r�s�`�w�@�d�������������������������������Ă݂悤���Ȃ��B�Ƃ����C�ɂȂ����̂������B �E�ŁA���낢��l�������̉�H�͂����B �E�I�i�̃v�b�V���v���G�~�b�^�t�H���A���肪��₲���Ⴒ���Ⴕ�������ł��邪�A�I�i�f�q���̕ی�̂��߂̓d��������H���t���Ă��邾���ŁA�`�Ă��̂��̂��B �E�ƌ����킯�ō���͂`�Ăł���B |

|

|

|

| �E�����ł̂p�P�C�p�Q�C�p�R���Q�r�b�P�V�V�T�`�y�тp�S�C�p�T���Q�r�`�W�V�Q�`�́A���ꂼ���Q�r�b�Q�V�T�Q���Q�r�`�V�X�W�f�̂k�s�r����������̃_�~�[�ł���B���A���͂��̂��̂ł���B �E�`�Ă͏I�i�Ƀv�b�V���v���G�~�b�^�t�H���A��������̂ŁA�Q�i�ڂ̓���_�͂b�Ă̂悤�ɂ����K�v�͂Ȃ��B�̂łQ�i�ڂ̓���_�͕��M��v���Ȃ��悤�ɂP�D�W���`�ɐݒ肷��B��������ƂQ�i�ڃJ�X�R�[�h�A���v�ɂh���imax�j���P�O���`���Q�r�`�P�X�U�W���g����̂ŁA����͂b�Ăɂ�鐻���Ƃ͋t�ɁA���i�m�`�����l���A�Q�i�ڂo�`�����l���̍\���Ƃ��邱�Ƃɂ��A���i�Ƀf���A���e�d�s���Q�r�j�R�W�X�f�q�A�Q�i�ڂɃf���A���s�q���Q�r�`�V�X�W�f�Ƃ����A���Ƀf�B�X�R���̑f�q���W�����N�{�b�N�X���猻���Ɉ����グ�ċN�p����B�܂��A���i�̓���_�͓��ɕύX���闝�R���Ȃ��̂ŁA�O�삵���b�ĂƓ��l�ɂP�D�T���`�Ƃ���B �E�I�i�G�~�b�^�t�H���A�ɂ́A���s�i�ł���m�d�b�G���N�g���j�N�X���Q�r�b�R�W�S�O���Q�r�`�P�S�W�U���̗p����B�̂́A����炪�����ɍ̗p�ł���B��̑f�q�Ǝv���邩��ł���B�������ψ��U�O�O�u�A�h���imax�j���P�`�i�p���X�Ȃ�Q�`�j�A�S�����P�T�v�ŁA�����T��������ł͂����ɑ��蓾��R���v�������^���i�͂��̐��Ɍ�������Ȃ��B�m�d�b�G���N�g���j�N�X�Ƀp�b�P�[�W�Ⴂ�Ǝv�����Q�r�`�P�S�P�R�A�Q�r�b�R�U�R�Q�͂��邪�A�j���ł��[���Ƃ��Ďg��ꂽ���Ƃ������Q�r�`�P�S�O�O�Ɠ����p�b�P�[�W�ł���A�����͕��M�ւ̎��t��������B �E���āA�����łQ�i�ڂ��Q�r�b�T�S�U�U�����Q�r�`�P�X�U�W���̓��f���p�����[�^��K���ɂł����グ�����̂ł���B�̂ŁAmodoki�̂����t���Ă���B(���j�@�܂��A�Q�r�b�R�W�S�O���ƂQ�r�`1�S�W�U���ɂ��Ă����̃��f���p�����[�^�͂��ǂ��ł���B���A�Q�r�`�P�S�W�U���̃��f���p�����[�^�͂m�d�b�G���N�g���j�N�X�����Ă���Q�r�`�P�S�P�R�̃��f���p�����[�^���̂��̂Ƃ��Ă���B�Ƃ����̂́A�Q�r�`�P�S�P�R�ƂQ�r�`�P�S�W�U�͓����`�b�v�̃p�b�P�[�W�Ⴂ�ł͂Ȃ����Ɛ�������邽�߁B�����A�{���ɂ������ǂ����͕ۏ̌���ł͂Ȃ��̂ł���t��modoki�Ƃ����B�Q�r�b�R�W�S�O�ɂ��Ă͎c�O�Ȃ��烂�f���p�����[�^������Ă��Ȃ��̂ŁA�Q�r�`�P�S�P�R�̃��f���p�����[�^���Q�l�ɂ��ēK���ɂł����グ���B �E�Ƃ���ŁA�Q�r�`�P�S�P�R�̃��f���p�����[�^�œ����I�Ȃ̂́A�b�i�d=�P�D�R�R�P�U�d�|�X�i�P�R�R�P�D�U��F�j�ATR=�R�O�D�X�Q�WE�|�X�i�R�O�D�X�Q�W���r�j�ƁA�Ⴆ�o�b���P�T�O�v���Q�r�`�P�X�S�R�̂b�i�d=�T�O�O�O���e�A�s�q���T�O���r�Ɣ�r���Ă����炩�Ȃ悤�ɁA��������Ɋ֗^����Ǝv���邱���̃p�����[�^���p���[�g�����W�X�^���ɑ傫���Ƃ������Ƃł���B�����ƌ����Ȃ�������ψ����̂����Ȃ炴��Ȃ��̂��낤���B���邢�͊O�ς����U��Ȃ����ł��Ƃ��ƃp���[�g�����W�X�^�ł���Ƃ������ƂȂ̂��BC�i�b�̕���=�P�S�O.�U�TE-�P�Q�i�P�S�O�D�U�T���e�j�Ə��Ȃ��Ƃ͌����Ȃ����̂̂܂�����Ȃ�Ȃ̂ő����~����̂����AC�i�b�̂P�S�O�D�U�T���e���b�i�d�̂P�R�R�P�D�U���e�Ƃ͎����쎞�Q�i�ڂ��猩���I�i�̓��͗e���Ƃ��Ă���Ȃ�Ɍ����Ă���̂ł͂Ȃ����ƗJ�������Ƃ��낾�B �Q�r�b�R�W�S�O���ɂ��Ă����傤���Ȃ��̂ňꉞ���̓_�܂��ă��f���p�����[�^���ł����グ�Ă���B�͂����ĂQ�i�ڂ̓���_�P�D�W���`�ł������\���Ƀh���C�u�o���邾�낤���B �E�Ƃ����ꖕ�̕s�����������A�܂��͂��̂`�ẴQ�C�����ʑ��|���g���������k�s�r���������Ŋς�B �E����C�V���������̂O�D�O�P��F�Ƃr�q�|�R�O�R���������̂P�Q�O��F�Ƃ����ꍇ�̃p�����g���b�N��́B |

|

| �E���ʂ͂����B �E�I�[�v���Q�C���i�ԁj�A�N���[�Y�h�Q�C���i�j�A���[�v�Q�C���i�j�Ƃ��A��荂��ɐL�тĂ���������ׂO�D�O�P��F�i�����ב����j�̏ꍇ�ŁA������������ׂP�Q�O��F�̏ꍇ�B �E���ŃI�[�v���Q�C���͂P�P�W�D�T��B�A�N���[�Y�h�Q�C���͂T�S��B�A�]���ă��[�v�Q�C���͂U�S�D�T��B�ƂȂ��Ă���B �E���[�v�Q�C���i�j�̂PMH���ȏ�ł̋��������������悤�Ȋ��������邪�A�����d���A�ҕ����̏ꍇ���̉��Z�ݒ�ł͉��X�ɂ��Ă����Ȃ�B���A���̌�ς鐳���g��������`�g�����ɖ��͂Ȃ��̂ŋC�ɂ��Ȃ��B���������Ӗ��ł͂����������Z���̐ݒ肪�Ó��łȂ��̂�������Ȃ��B�i�O�O�G |

|

|

|

| �E�Ȃ��A�A���v�o�͂ɂ͂P�����̗e�ʕ��ב���R��}�����Ă���B��͂�G�~�b�^�t�H���A�͗e�ʕ��ׂɎア�B���̏ꍇ�����ׂ��P�Q�O���e���炢�܂ł͉��Ƃ��Ȃ邪�A����ȏ�̗e�ʕ��ׂɂȂ�ƁA���̒�R���Ȃ��ꍇ�N���[�Y�h�Q�C���̂P�l�g���t�߂Ƀs�[�N��������B�̂ŁA���̒�R��}�����邱�Ƃɂ���B �E���̓������C�V���O�D�O�P��F�i�����ב����j�A�P�Q�O��F�A�P�C�Q�O�O���e�Ƃ��A�܂����ꂼ��ɂ����āA�o�͂ɃV���[�Y�̒�R�q�S�Q�y�тq�S�R���O�D�P���i�Ȃ��ɑ����j�A�P�����Ƃ����ꍇ�̃_�u���p�����g���b�N��͂Ŋς�B |

|

|

|

| �E���̌��ʂ����ꂾ���A�v�̓N���[�Y�h�Q�C���i�j�̂P�O�O���g���ȏ�̗̈���ς�Ηǂ��B �E�N���[�Y�h�Q�C���i�j�̃��C�����T�{���邪�A�O���a�Ƃ̌�_������ɐL�тĂ��鏇�ɁA�b�V���O�D�P���e�łq�S�Q�C�q�S�R���O�D�P���̏ꍇ�ƂP�����̏ꍇ�i�Q�{�d�Ȃ��Ă���j�A�b�V���P�Q�O���e�A�q�S�Q���q�S�R���O�D�P���̏ꍇ�A�b�V���P�Q�O���e�A�q�S�Q���q�S�R���P�����̏ꍇ�A�b�V���P�C�Q�O�O���e�A�q�S�Q���q�S�R���O�D�P���̏ꍇ�A�����Ăb�V���P�C�Q�O�O���e�A�q�S�Q���q�S�R���P�����̏ꍇ�ł���B �E�o�͂ɃV���[�Y���q�S�Q���q�S�R�̂P�������Ȃ��ꍇ�A�e�ʕ��ׂ��傫���Ȃ�ƃN���[�Y�h�Q�C���̂P�l�g���ߕӂɃs�[�N�������A���Ȃ킿���U�̉\���������Ȃ邱�Ƃ�������B�܂��A�P�Q�O���e�܂łȂ���v�ƌ����Ȃ����Ƃ��Ȃ����A���������]��]�T�̂Ȃ��œ��삳����A���v�Ŕ��U�Ȃǂ��N�����̂͑S���g�ł͂Ȃ��̂ŁA�P�����̒�R���V���[�Y�ɑ}�����邱�Ƃɂ��悤�B�P�������Ȃ��ł����A���̂Ƃ���S������A���S�B �E�P�����ł͑傫�����Ȃ����H�Ƃ��������Ȃ��킯�ł͂Ȃ����A�������r�q�l�|�R�Q�R�`�ɂ́A���l�̎�|�Ǝv�����R�T�D�P�������}������Ă���悤�����A���ۖ�肱�̏ꍇ�͕��ׂɂȂ���̂��C���[�X�s�[�J�[�̂P�Q�O���e���x�̗e�ʕ��ׂȂ̂őS�����͂Ȃ��B�Ǝv���B |

|

|

|

| �E���̍ہA�Q�l�Ƃ��āA�O�삵���b�ẴQ�C�����ʑ��|���g���������ς�B�����ł��p�P�A�p�Q�A�p�R���Q�r�`�X�V�O�Ƃp�U�A�p�V���Q�r�b�P�V�V�T�`�͂��ꂼ���Q�r�`�P�P�T�U���Q�r�b�P�T�W�R�f�̂k�s�r����������̃_�~�[�ł���B �E���l�ɕ���C�R���������̂O�D�O�P��F�Ƃr�q�|�R�O�R���������̂P�Q�O��F�Ƃ����ꍇ�̃p�����g���b�N��́B |

|

|

|

| �E�I�[�v���Q�C���i�ԁj�A�N���[�Y�h�Q�C���i�j�A���[�v�Q�C���i�j�Ƃ��A��荂��ɐL�тĂ���������ׂO�D�O�P��F�i�����ב����j�̏ꍇ�ŁA������������ׂP�Q�O��F�̏ꍇ�ł���B �E���ŃI�[�v���Q�C���͂P�P�X�D�T��B�A�N���[�Y�h�Q�C���͂T�S��B�A�]���ă��[�v�Q�C���͂U�T�D�T��B�ƂȂ��Ă���B �E���̂��I�[�v���Q�C���������ב������U�`�VMH���ȏ�ň�x���������₩�ɂȂ�B���̂��߃N���[�Y�h�Q�C�������X���ɂȂ�B���̗��R�͗ǂ�������Ȃ����A���̌�ς鐳���g��������`�g�����ɓ��i�̖��͂Ȃ��̂ł�����C�ɂ��Ȃ��B���A�����̉e���͏o��悤���B |

|

|

|

| �E���̂b�Ă��Q�C�����ʑ��|���g�������Ə�̂`�Ă��Q�C�����ʑ��|���g�������ɂ����Ė��m�ɈႤ�̂́A���ׂb���P�Q�O���e�̏ꍇ�̃I�[�v���Q�C���i�ԁj�i���������ă��[�v�Q�C���i�j�������j���J�b�g�I�t���g���ł���B�`�Ă͂��ꂪ�������ƕς��Ȃ��̂ɑ��Ăb�Ăł͂��ꂪ���ɉ������Ă��܂��B�͓̂��R�ŁA�b�Ăł̓I�[�v���Q�C���̃J�b�g�I�t���g���͕��ׂ̂b�̗e�ʂ̑傫���ɔ����ƂȂ�̂��������B�`�Ăł͂����͂Ȃ�Ȃ��_���G�~�b�^�t�H���A��lj������`�Ă̑��ݗ��R�̈�ł����낤�B���A�܂������ɂ���Ă͑債���Ⴂ�ł͂Ȃ����B(���j���ꂪ�̂ɃG�~�b�^�t�H���A��lj������ꍇ�e�ʕ��ׂŔ��U���₷���Ȃ�Ƃ������Ƃł����邵�B |

|

| �@ | |

| �E���ɂ`�Ăɖ߂��āA�I�i�̓���_�ɂ��Ăł���B �E���̓���_�A���Ȃ킿�A�C�h�����O�d���͂P�O���`�Ƃ��A�ی��H�ɂ��d�������l�͂Q�O���`�ɐݒ肷��B��������ƁA���̂`�Ẳ�H�Ȃ畉�ׂɂ͂S�O���`�i�}�Q�O���`�j���|���̓d�����s���A�`������ŋ����o���邱�ƂɂȂ�B���������āA���̐ݒ�Ȃ�A���ׂP�Q�O��F�̏ꍇ�A�����g�T�O��Hz���A���̓d���d���ł̂قڍő�o�͓d���ƂȂ��R�T�O�ur.m.s.�i�X�X�OV���|���j�̏o�͂��\�ł���B�Ƃ����̂������ł���B �E�̂ŁA�k�s�r���������ŕ��ׂb�V���P�Q�O���e�A�Q�u�i�}�P�u�j���|���̂T�O���g�������g���́A�]���Đ����g�T�O���g���̂P�C�O�O�O�u�i���m�ɂ͂X�U�V�D�V�S�u�j���|���o�͂��o���邩�ǂ������ς�B |

|

|

|

| �E�ŁA���̌��ʂ͂����B �E���o�͓d���ł���A���o�͓d���ł���B�Y��ɂT�O���g���łP�C�O�O�O�u�i���m�ɂ͂X�U�V�D�V�S�u�j���|���̐����g���o�͂���Ă���B �E���킹�ďI�i�e�g�����W�X�^�̃R���N�^�d�����\�����Ă��邪�A���ꂼ��`���͈̔͂œ��삵�A�o�͓d����n���Ă���Ƃ������Ƃ�������B �E�o�͓d�����I�i�g�����W�X�^�̕ی��H�Őݒ肵�������d���̔{�i���͈̔͂ł̓�����`���ɐݒ肵���ꍇ�̓A�C�h�����O�d���̂S�{�j�ɂȂ�̂́A�v�b�V���v�������̂��肪���������b�g�ł���B���ꂪ�I�i���d����H�t���V���O���G�~�b�^�t�H���A�ɂ����a�āA�����Ăb�Ăł́A�A�C�h�����O�d���i����d����H�Őݒ肵���d���j�̂Q�{�����̂܂o�͓d���̌��E�ɂȂ�B���̓_�����ł��`�Ă̗̍p�ɂ͈Ӗ�������ƌ�����B�Ǝv���B |

|

|

|

| �E���̕ӁA��r�ΏۂƂ��Ăb�Ă̏ꍇ���ς�B �E�b�Ă̏I�i�i�v����ɂQ�i�ځj�̓���_�͂S�D�T���`�ɐݒ肵�Ă���̂ŁA�����d���i���ő�d���j�͂X���`�ł���B�`�Ă̂P�^�S�D�S�S���B�]���āA��������ׂP�Q�O��F�ɂ������A���̓d���d���ł̂قڍő�o�͓d���ƂȂ��R�T�O�ur.m.s.�i�X�X�OV���|���j�̏o�͂��\�Ȏ��g���́A�`�Ă̂P�^�S�D�S�S�̂P�P�D�Q�T��Hz�܂��ƂȂ�B�Ƃ����̂������ł���B �E�̂ŁA�k�s�r���������ŕ��ׂb�V���P�Q�O���e�A�Q�u�i�}�P�u�j���|���̂P�P�D�Q�T���g�������g���́A�]���Đ����g�P�P�D�Q�T���g���̂P�C�O�O�O�u�i���m�ɂ͂X�U�V�D�V�S�u�j���|���̏o�͏��ς�B |

|

|

|

| �E�ŁA���̌��ʂ͂����B �E�Ԃ��o�͓d���ł���A���o�͓d���ł���B�Y��ɂP�P�D�Q�T���g���łP�C�O�O�O�u�i���m�ɂ͂X�U�V�D�V�S�u�j���|���̐����g���o�͂���Ă���B �E���킹�ďI�i�i���Q�i�ځj�e�g�����W�X�^�̃R���N�^�d�����\�����Ă���B���̏ꍇ�͓��R�������ꂼ��`���͈̔͂œ��삵�A�����A���v�̐����g�o�͂ƒ�d����H�̋z�����ݓd���Ƃŏo�͓d�����n����Ă���Ƃ������Ƃ�������B���A���̓d���ω��悪�O���`����X���`�̌��E�ɋ߂��ɂ��邱�Ƃ�A�o�͓d���̕ω��͈͂��X���`�i�}�S�D�T���`�j���|���ƂQ�i�ڍ����A���v�i�p�U���p�V�j�̕ω��\�͈͂Ɠ����ł��邱�Ƃ�������B |

|

|

|

| �E�Ƃ���ŁA�a�āA�b�Ăł͕s�\�Ȃ`�Ă̂�����̃����b�g�́A�I�i���a���œ��삳���邱�Ƃ��\�Ȃ��Ƃł���B �E�I�i�A�C�h�����O�d�����o�C�A�X������H�Œ������ĂP���`�Ƃ���Ƃ����Ȃ�B�ی��H�ɂ��d�������l�͂Q�O���`�Ɠ����ɐݒ肵�Ă���B �E���̏ꍇ�A���ׂb�V���P�Q�O���e�A�Q�u�i�}�P�u�j���|���̂T�O���g�������g���́A�]���ďo�͐����g�T�O���g���̂P�C�O�O�O�u�i���m�ɂ͂X�U�V�D�V�S�u�j���|�����o�͂����ꍇ�ǂ��Ȃ�̂����ς�B |

|

|

|

| �E���̌��ʂ͂����B �E���o�͓d���ł���A���o�͓d���ł���B�a������ł��Y��ɂT�O���g���łP�C�O�O�O�u�i���m�ɂ͂X�U�V�D�V�S�u�j���|���̐����g���o�͂���Ă���B �E���킹�ďI�i�e�g�����W�X�^�̃R���N�^�d�����\�����Ă��邪�A���ꂼ��a���ŃX�C�b�`���O���삵�A�o�͓d����n���Ă��邱�Ƃ�������B �E���̏ꍇ�ł��A�o�͓d���͏I�i�g�����W�X�^�̕ی��H�Őݒ肵�������d���Q�O���`�̔{�̂S�O���`�i�}�Q�O���`�j���|���ƂȂ��Ă���B �E���̏ꍇ�͏I�i�̑����͔��ɏ������Ȃ邪�A������I�i�v�b�V���v�������̂��肪���������b�g�ł���B�G�R�̎��ゾ����A�`�Ă��I�i�a���œ��삳����͍̂��I�ɗL�͂ȑI������������Ȃ��B |

|

|

|

| �@�@ | |

| �E���ɕ��`�g�������ς�B �E�ŏ��ɂb�Ă��ς�B �E���͂͂Q�u���|���̂P�O���g�����`�g�ƂP�O�O���g�����`�g�ŁA�o�͂P�C�O�O�O�u�i���m�ɂ͂X�U�V�D�V�S�u�j���|���ƁA�v����ɂ��̓d���d���ł͂قڍő�o�͂̏ꍇ�ƁA���͂��̂P�u���|���̂P�O���g�����`�g�ƂP�O�O���g�����`�g�Ƃ����ꍇ�ɂ��āA���ꂼ�ꕉ�ׂ��ב����̂O�D�O�P���e�ƂP�Q�O���e�Ƃ���p�����g���b�N��͂ŁA�����ׂ̏ꍇ�ƕ��ׂP�Q�O���e�̏ꍇ���ꋓ�Ɋς�B |

|

|

|

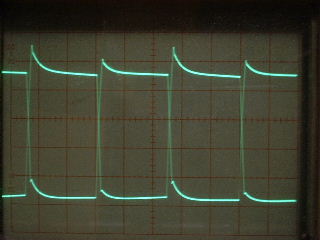

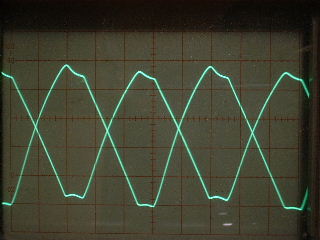

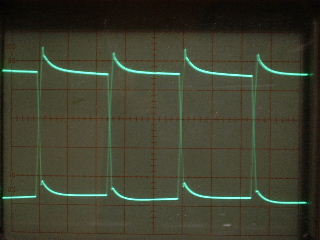

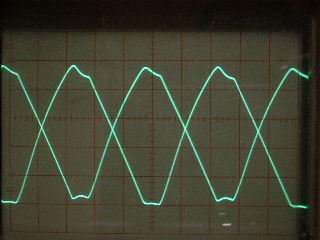

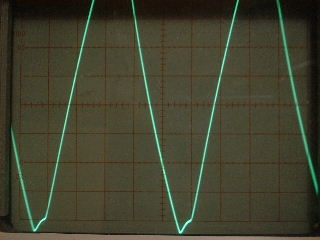

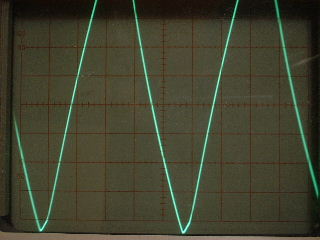

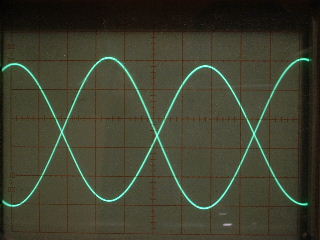

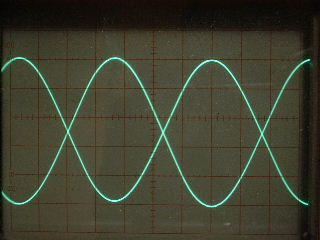

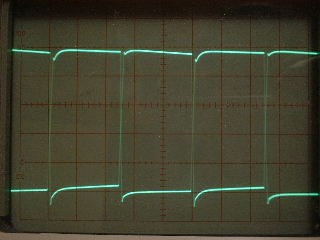

| �E���ʂ͂����B �E�����ׂO�D�O�P���e�i�����ב����j�̏ꍇ�ł���A�Ԃ����ׂP�Q�O���e�̏ꍇ�ł���B �E�����ב����̏ꍇ�͂P�C�O�O�O�u���|���̂P�O���g�����`�g���Y��ɏo�͂���Ă���B�P�O�O���g�����`�g�����������ׂ̏ꍇ���ɗǍD���B���̗����オ��g�`����ςăX���[�E���[�g�͂P�C�O�O�O�u�^���r��D�ɒ����Ă���B �E���ׂP�Q�O���e�̏ꍇ�́A�I�i�i���̏ꍇ�́��Q�i�ځj�̕��ׂP�Q�O���e�ւ̍ő募���d������d����H�Őݒ肵���S�D�T���`�ł���̂ŁA����ɂ�肱���ŃX���[�E���[�g���S�D�T���`�^�P�Q�O���e���R�V�D�T�u�^���r�ɐ��������B���̌��ʂ��Ԃ̕��`�g�����g�`�ł���B |

|

| 10kHz�@���͂Q�u���|�� | 100kHz�@���͂Q�u���|�� |

|

|

| 10kHz�@���͂P�u���|�� | 100kHz�@���͂P�u���|�� |

|

|

| �E��E���̂P�O�O���g�����͂Q�u���|���̏ꍇ�̐Ԃ̉����g�`�̌X���ł��̃X���[�E���[�g���v�Z����ƁA�S���r�łQ�T�O�u���x�̗����オ��A���Ȃ킿�Q�T�O�u�^�S���r���U�Q�D�T�u�^���r�ƁA�����ȏ�̃X���[�E���[�g�ƂȂ��Ă���B�̂����A����̓V�~�����[�V�����Ŋς�ƕ��`�g�̗����オ��A����������̏u�Ԃɉ��̂���d����H�Őݒ肵���S�D�T���`�̔{�߂��d��������邽�߂̂悤���B�����ɂ������Ȃ�̂��ǂ����͕s���B�i�O�O�G�@�����A���ׂP�Q�O��F�̏ꍇ�͂��̃X���[�E���[�g�ɋK�肳��ĕ��`�g�������Ԃ̂��̂ɂȂ��Ă���Ƃ������Ƃł���B �E�Ȃ��A�P�C�O�O�O�u���|���o�͂ł͂��܂�ڗ����Ȃ����A�����ב������̕��`�g�����ɋ͂��Ȃ���v���V���[�g�������Ă���B���ꂪ���͂��P�u���|���Ƃ��ďo�͂T�O�O�u���|���̕��`�g�����ł����m�ɂȂ��Ă���B����͑�����Ŋς��Q�C�����ʑ��|���g�������ɂ����āA�b�ẴI�[�v���Q�C���������ב����łU�`�VMH���ȏ�ň�x���������₩�ɂȂ��Ă��邱�Ƃɂ����̂Ǝv����B �E���A�����Ĕ��ɗǍD�ȉߓn�����ł���B |

|

| �E���ɂ`�Ăł���B �E������A���͂͂Q�u���|���̂P�O���g�����`�g�ƂP�O�O���g�����`�g�ŁA�o�͂P�C�O�O�O�u�i���m�ɂ͂X�U�V�D�V�S�u�j���|���Ƃ���������̓d���d���ł͂قڍő�o�͂̏ꍇ�ƁA���͂��̂P�u���|���̂P�O���g�����`�g�ƂP�O�O���g�����`�g�Ƃ����ꍇ�ɂ��āA���ꂼ�ꕉ�ׂ��ב����̂O�D�O�P���e�ƂP�Q�O���e�Ƃ���p�����g���b�N��͂ŁA�����ׂ̏ꍇ�ƕ��ׂP�Q�O���e�̏ꍇ���ꋓ�Ɋς�B |

|

|

|

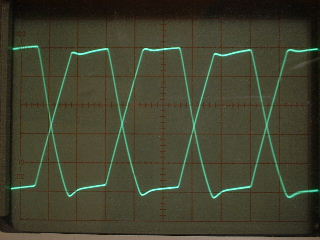

| �E������������ב����̏ꍇ�A�Ԃ����ׂP�Q�O���e�̏ꍇ�ł��邪�AC�ĂƂ̔�r�Ŗ��炩�Ȃ̂́A �@�����ב����̏ꍇ�̗����オ��A����������̑����A�v����ɃX���[�E���[�g��C�Ă�菬�������ƁB �A���ׂP�Q�O��F�̏ꍇ�̃X���[�E���[�g�͋t��C�Ă��傫�����ƁB �ł���B �E�A�́A�I�i�ɃG�~�b�^�t�H���A��t�����Ă��̐����d�����Q�O��A��C�āi�S�D�T��A�j�̂S�D�S�S�{�ɐݒ肵�Ă���̂����炱��͓��R�ł���A�t�ɂ����Ȃ�Ȃ����A�Ă̈Ӗ����Ȃ��B���̏ꍇ�Q�O��A�^�P�Q�O��F���P�U�VV�^���r�̃X���[�E���[�g�ƂȂ�Ƃ����̂������ł���B���A��E���̂P�O�O���g�����͂Q�u���|���̏ꍇ�̐Ԃ̉����g�`�̌X���ł��̃X���[�E���[�g���v�Z����ƁA�S���r�łV�O�O�u���x�̗����オ��A���Ȃ킿�V�O�O�u�^�S���r���P�V�T�u�^���r�ƁA�����ȏ�̃X���[�E���[�g�ƂȂ��Ă���B�̂́A�����d�������m�ɂQ�O���`�ł͂Ȃ��A�������⒴�������l�ɂȂ��Ă��邽�߂��낤�B �E�������̃X���[�E���[�g�́A��E���̂P�O�O���g�����͂Q�u���|���̏ꍇ�̗̉����g�`�̌X���Ōv�Z����ƁA�ŏ������ŏ��X�ɒᑬ�ɂȂ�g�`�Ȃ̂����A���ς���P�O�O�O�u�^�S���r�Ƃ��ĂQ�T�O�u�^���r�Ƃ������Ƃ��낾�B |

|

| 10kHz�@���͂Q�u���|�� | 100kHz�@���͂Q�u���|�� |

|

|

| 10kHz�@���͂P�u���|�� | 10�OkHz�@���͂P�u���|�� |

|

|

| �E�`�ĂƂb�Ă̂��̂悤�ȈႢ�́A�`�ĂƂb�Ăł͖������̃X���[�E���[�g���K�肵�Ă��鏊�Ȃ̂��̂��قȂ��Ă��邽�߂��B�b�Ă̏ꍇ����͏��i�̓d���ƂQ�i�ڂ̂s�q�̓��o�͊Ԃ̈ʑ���e�ʂO�D�T���e�ł���B�̂ɑ��āA�`�Ăł͂Q�i�ڂ̓d���ƏI�i�s�q�̂b�������̗e�ʂƂȂ�B�̂́A�`�Ă͂Q�i�ڂ̓���_���d����H�łP�D�W���`�Ƃ��Ă���̂ōő募���d�����P�D�W���`�ł���Ƃ���A�I�i�s�q�̂b�������̗e�ʂ̓f�o�C�X���f���̃p�����[�^�Ō����Ƃ���p���[�g�����W�X�^���̑傫��������̂ŁA�����ł̃X���[�E���[�g�̕����������Ȃ��Ă��ꂪ�������̃X���[�E���[�g���K�肷�邱�ƂƂȂ�B �E�Ƃ������Ƃ��z�肳�ꂽ�̂ŁA�����A�����ł̃X���[�E���[�g���I�i�̓���d���ƕ��ׂP�Q�O���e�ŋK�肳���X���[�E���[�g�����������Ȃ�����`�Ă̈Ӗ����Ȃ��Ȃ��Ă��܂��Ȃ��B�B�B�ƗJ�������̂ł���B �E���A���ʂƂ��ẮA�I�i�̓���d���ƕ��ׂP�Q�O���e�ŋK�肳���X���[�E���[�g��菬�����Ȃ邱�Ƃ͂Ȃ��A�Q�T�O�u�^���r���x�̃X���[�E���[�g��������Ƃ����肢�ł���B�ł�������ɑI���ł���f�q���Ȃ��̂����炱��͏\���������ׂ����ʂ��B �E���Ȃ킿�A����Ȃ�`�Ă삷��Ӗ�������Ƃ������́B�Ƃ������ƂɂȂ�B�ǂ������B�ǂ������B�i�O�O�j �E�Ȃ��A�`�Ăł͂b�Ă̂悤�ȃv���V���[�g�͐����Ă��Ȃ��B |

|

| �E�Ƃ���ŁA�����A���̏�����ɉ��P�������ƂȂ�Ε���͓�B��͂Q�i�ڂ̓���d���𑝂₷���ƁB��͏I�i�G�~�b�^�t�H���A���_�[�����g���ڑ��ɂ��Ă��̑O�i�ɂ͂b�������̏������g�����W�X�^���N�p���邱�ƁB���B �E�Q�i�ڂ̓���d���𑝂₷���A�h�����T���`�ȉ��Ŏg���ׂ��J�X�R�[�h��H�̂Q�r�`�P�X�U�W���������Ȃ�ق��A������������̂łQ�i�ڃJ�X�R�[�h��H�ƒ�d����H�̃g�����W�X�^�ɕ��M��w���킹���肵�Ȃ���Ȃ�Ȃ��Ȃ�B�̂ŁA���܂��肽���Ȃ��B�̂ŁA�I�i���_�[�����g���ڑ��ɂ�����@���ς�B�_�[�����g���O�i�g�����W�X�^�͒�b�������Q�r�b�Q�V�O�T���Q�r�`�P�P�S�T�ł���B |

|

|

|

| �E���ʂ͂����B �E�������A�����ׂO�D�O�P���e�i�����ב����j�̏ꍇ�ł���A�Ԃ����ׂP�Q�O���e�̏ꍇ�ł���B �E��E�����P�O�O���g�����͂Q�u���|���̏ꍇ�̉����g�`�Ŗ��炩�����A�����ב������i�j�̃X���[�E���[�g���W�O�O�u�^���r���x�ɉ��P����A����ɔ����ĂP�Q�O���e�����̃X���[�E���[�g�܂łW�O�O�u�^�S���r���Q�O�O�u�^���r���x�Ɨ��_�l�ȏ�̂��̂ɂȂ��Ă��܂��Ă��邪�A������b�ē��l�V�~�����[�V�����Ŋς�ƕ��`�g�̗����オ��A����������̏u�Ԃɉ��̂������d���l�ȏ�̓d��������邽�߂̂悤���B �E�ŁA���ꂪ�I�i���_�[�����g���ڑ��Ƃ������ʂƂ������ƂɂȂ�B �E���A�Q�r�`�P�P�S�T�A�Q�r�b�Q�V�O�T�͑ψ��̊W�Ŏ��ۂɂ����ɍ̗p���邱�Ƃ͕s�\�ł���B |

|

| 10kHz�@���͂Q�u���|�� | 100kHz�@���͂Q�u���|�� |

|

|

| 10kHz�@���͂P�u���|�� | 10�OkHz�@���͂P�u���|�� |

|

|

| �E���̏ꍇ�ψ��I�ɂ͂U�O�O�u���K�v�ł���̂ŁA�_�[�����g���ڑ��Ƃ��悤�Ƃ��Ă������ɑO�i�ɍ̗p�ł���̂́A��i�Ɠ����Q�r�`�P�S�W�U�ƂQSC�R�W�S�O�ȊO�ɂȂ��B�̂ŁA�����Ȃ��Ă��܂��B �E����ł͂Q�i�ڂɑ��鍂��ł̕����ʂ������Ȃ̂őS���Ӗ����Ȃ����낤���Ƃ͗e�Ղɑz�肳���B�̂����A�O�̂��ߓ��l�ɕ��`�g�������ςĂ����B |

|

|

|

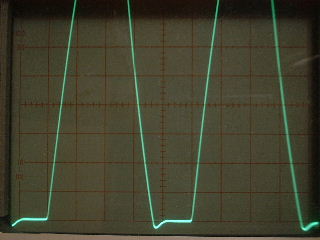

| �E���ʂ̓_�[�����g���ڑ��łȂ��ꍇ�Ɛ����ς��Ȃ��B�z��ʂ�ł���B �E�̂ŁA�����I�ɂ͏I�i�����̂悤�Ƀ_�[�����g���ڑ��Ƃ���I�����͂Ȃ��B |

|

| 10kHz�@���͂Q�u���|�� | 100kHz�@���͂Q�u���|�� |

|

|

| 10kHz�@���͂P�u���|�� | 10�OkHz�@���͂P�u���|�� |

|

|

| �@�@�@ | |

| �E���ɁA�P���g�������g���͂̏ꍇ�̂e�e�s��͂Řc�݂̗l�q���ς�B �E�ŏ��͓��͂Q�u���|���A���Ȃ킿�o�͂͂P�C�O�O�O�u�i���m�ɂ͂X�U�X�D�V�S�u�j���|���ƁA�قڍő�o�͂̏ꍇ�B |

|

|

|

| �E���̌��ʂ͂����B �E�܂��̓o�����X�o�͂̈���i�n�t�s�{�j�̂e�e�s�B���Ȃ荂���g�̃I���p���[�h�ł���A�ő�̍����g���Q���ł��̃��x���͊�{�g�́|�T�O���a��ƂȂ��Ă���A�k�s�r���������̐肤�c���́A �E�sotal Harmonic Distortion: 0.222101%�B |

|

|

|

| �E������͓������o���P�C�O�O�O�u�i���m�ɂ͂X�U�X�D�V�S�u�j���|�������o�����X�o�͂̂e�e�s�B�v����Ƀh���C�u�A���v�{���̏o�͂̂e�e�s�B �E�o�����X�o�͂ł͋����������g���ł�������đ啝�Ɍ������A���̘c���� �ETotal Harmonic Distortion: 0.019272%�@�ƂP�^�P�O�ȉ��ɂȂ����B�ő�o�͎��ɂ��̃��x���́A���Ȃ��c�݂ƌ�����̂ł͂Ȃ��낤���B |

|

|

|

| �E���ɁA���͂��O�D�T�U�T�V�u���|���Ƃ��ďo�͂��Q�W�Q�u���|���i�v����ɂP�O�OVr.m.s�D�j�Ƃ����ꍇ�B �E�܂��̓o�����X�o�͂̈���i�n�t�s-�j�̂e�e�s�����A���ʂ́A �ETotal Harmonic Distortion: 0.056415%�B |

|

|

|

| �E���ɁA�P�O�OVr.m.s�D�o�͎��̃o�����X�o�͂�FFT�B �ETotal Harmonic Distortion: 0.001413%�@�Ƃ��̏ꍇ�������������g���������Ęc���͂P�^�S�O�ł���B �E�r�s�`�w�̏����i�Ɠ��l�A���̘c���O�D�O�P���ȉ��i�P���g���@�P�O�OVr.m.s�D�j�Ƃ����ėǂ������B�i�O�O�j |

|

|

|

| �E�Q�l�܂ł�C�Ăɂ��Ă����l�ɂ��ĂP���g�������g���͂̏ꍇ�̂e�e�s��͂Řc�݂̗l�q���ς�B |

|

|

|

| �E�ŏ��͓��͂Q�u���|���A���Ȃ킿�o�͂P�C�O�O�O�u�i���m�ɂ͂X�U�X�D�V�S�u�j���|���ƁAC�Ăɂ����Ă��قڍő�o�͂̏ꍇ�̃o�����X�o�͂̈���iOUT1)��FFT�ł��邪�A�X�y�N�g���I�ɂ͂`�Ăɂ悭���Ă���B �E�ŁA�k�s�r���������̐肤�c���́A �ETotal Harmonic Distortion: 0.302909% �E�`�āi0.222101%�j���O�D�P�|�C���g�����B |

|

|

|

| �E���ɁA�������o���P�C�O�O�O�u�i���m�ɂ͂X�U�X�D�V�S�u�j���|�������o�����X�o�͂̂e�e�s�B �E�b�Ăł��o�����X�o�͂ł͋����������g���ł�������đ啝�Ɍ������A���̘c���� �ETotal Harmonic Distortion: 0.019304%�@�Ƃb�Ăł��P�^�P�U�Ɍ����ł���B �E���A������A�`�āi0.019272%�j���͂��ɑ����B |

|

|

|

| �E���ɁA���͂��O�D�T�U�T�V�u���|���Ƃ��ďo�͂��Q�W�Q�u���|���i�v����ɂP�O�OVr.m.s�D�j�Ƃ����ꍇ�B �E�܂��̓o�����X�o�͂̈���i�n�t�s�Q�j�̂e�e�s�����A���ʂ́A �ETotal Harmonic Distortion: 0.034889% �E���x�͂`�āi0.056415%�j����c���ɂȂ����B |

|

|

|

| �E���ɁA�P�O�OVr.m.s�D�o�͎��̃o�����X�o�͂�FFT�ł��邪�A �ETotal Harmonic Distortion: 0.001046%�@�Ƃ��̏ꍇ�������������g���������Ęc���͂P�^�R�R�ł���A������`�āi0.001413%�j���͂��Ȃ����c���ł���B |

|

|

|

| �E���l����ɁA�k�s�r���������̐肢���ʂł͂b�ẴI�[�v���Q�C���̕����`�ẴI�[�v���Q�C�����͂��ɑ傫���̂ŁA���҂̓N���[�Y�h�Q�C���ݒ肪����������m�e�a�ɂ��Ă͂`�Ă��b�Ă̕����͂��ɑ傫���B���������āA�b�Ă̘c�����`�Ă��ǂ��Ȃ�̂͗����ł��낤�B�o�͂P�C�O�O�O�u���|���̑�o�͎��ɂ`�Ă̕��̘c�����ǂ��̂́A�����ł͂`�Ă̓d���d����z��́}�Q�V�O�u�A�b�Ă��d���d���������́}�Q�U�O�u�ƁA�`�ĂɗL���ɐݒ肵�����ʂƉ�����̂��Ó����낤�B����A�`�Ă͂b�Ăɔ�ׂ�ΏI�i�G�~�b�^�t�H���A�������ĉ�H����蕡�G�ɂȂ����ɂ�������炸�w�ǂb�ĂƓ����x�̘c���ł���A��������Ă���ΗǍD�Ȍ��ʂƔ��f���ėǂ��̂ł͂Ȃ����B�Ǝv���B |

|

| �E�`�ĂŏI�i�G�~�b�^�t�H���A���a������Ƃ����ꍇ�͂ǂ����B �E���l�Ɋς�B |

|

|

|

| �E�ŏ��͓��͂Q�u���|���A���Ȃ킿�o�͂P�C�O�O�O�u�i���m�ɂ͂X�U�X�D�V�S�u�j���|���̏o�͂̏ꍇ�̈���iOUT�{)��FFT�B �E�k�s�r���������̐肤�c���́A �ETotal Harmonic Distortion: 0.256709% �E�`���̏ꍇ�̘c����0.222101%�ł���������A�͂��Ɉ����Ƃ������ʂ��B |

|

|

|

| �E���ɁA�������o���P�C�O�O�O�u�i���m�ɂ͂X�U�X�D�V�S�u�j���|�������o�����X�o�͂̂e�e�s�B �ETotal Harmonic Distortion: 0.009242% �E�Ȃ�ƁA�`���̏ꍇ�̘c���i0.019272%�j����c���Ƃ������ʂł���B |

|

|

|

| �E���ɁA���͂��O�D�T�U�T�V�u���|���Ƃ��ďo�͂��Q�W�Q�u���|���i�v����ɂP�O�OVr.m.s�D�j�Ƃ����ꍇ�B �E�܂��̓o�����X�o�͂̈���i�n�t�s-�j�̂e�e�s�����A���ʂ́A �ETotal Harmonic Distortion: 0.061501% �E���̏ꍇ�͂�͂�`���̏ꍇ�̘c���i0.056415%�j��葽���B |

|

|

|

| �E���A�P�O�OVr.m.s�D�o�͎��̃o�����X�o�͂̂e�e�s�ł��邪�A �ETotal Harmonic Distortion: 0.001003%�@�Ƃ��̏ꍇ���`���̏ꍇ�̘c���i0.001413%�j����c���Ƃ̐肢���ʂ��B |

|

|

|

| �E���Ȃ킿�A�`�Ăɂ����ďI�i�G�~�b�^�t�H���A���`������̏ꍇ�Ƃa������̏ꍇ�ł́A�o�����X����̈���̏o�͎��̂ł͂a���̏ꍇ�̘c���̕����傫�����A�o�����X�o�͂͂`��������a������ɂ��������c�����������Ƃ������Ƃł���B �E���`�ށB�B�B�ɂ킩�ɂ͐M�����������ʂł��邪�A���ꂪ�����ł���A�`�Ăɂ����ďI�i�a��������̗p���邱�Ƃ́A�G�R�̊ϓ_�����ł͂Ȃ����̓_�ł��L�͂ȑI�����ł���B�Ƃ������ƂɂȂ�B |

|

�@�@

�@�@