�@�@�@�V���v����CPU������Ă݂悤�@�i���̂R�j

�@�@�|VHDL��p�����R���|�[�l���g�̐v�|

���V�@�T�i�@

�P�D�͂��߂�

�O�͂ł́C CPU�̏�̊K�w�i���C�A�j �̐v���s���܂����D

CPU���\������v�f�͂��ׂāC �R���|�[�l���g �Œ�`���C�����̐ڑ��W�� �����M���isignal�j ��p���ĕ\�����܂��D

�{�͂ł́C���̃R���|�[�l���g�̐v�� VHDL ��p���čs���܂��D

������̃R���|�[�l���g���C�ɂ߂ĒP���ȍ\���ƂȂ��Ă��܂��D

CPU�S�̂̒��ł̖�����C���̓��삪��̓I�ɃC���[�W�ł���悤�C��������w�K���ĉ������D

�Q�D�e�R���|�[�l���g�̐v

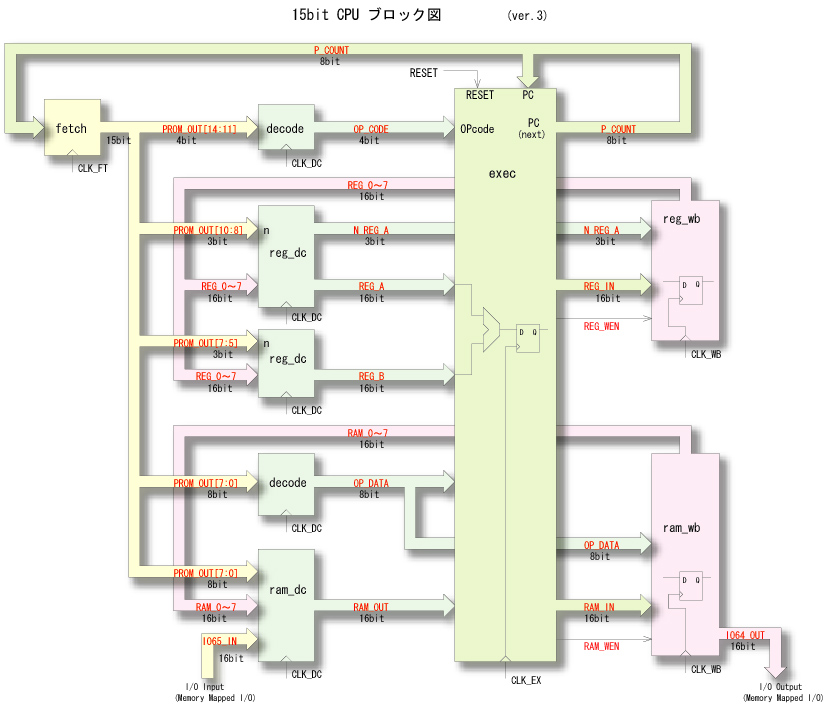

�ȉ��ɁCCPU�̃u���b�N�\���ƁC�e���̐M�����������܂��D

�����́C 4�̃u���b�N �C 8��ނ̕��i�i�R���|�[�l���g�j ����\������Ă��܂��D

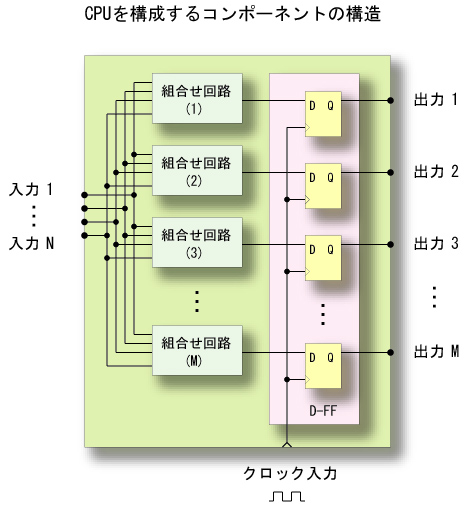

��2�͂ŏq�ׂ��悤�ɁC���ׂẴR���|�[�l���g�́C�ȉ��̂悤�ȍ\���ƂȂ��Ă��܂��D

�������C VHDL �ŋL�q����ƁC�ȉ��̂悤�ɂȂ�܂��D

�����ŁC

'xxx' �@�̓R���|�[�l���g�̖��́C 'CLK' �͂��̃N���b�N�ł��D

architecture RTL of xxx is begin �@�@ process (CLK) �@ begin �@ �@ if (CLK'event and CLK = '1') then �@ �@ �@ --�@�ȉ��C�g������H�̂悤�ȕ\�� �@ �@ �@ component �@�o��1 <=�@ component �@���͂̊� �@ �@ �@ �@�@�@�@�@�@�@�@�@�@�@�F �@ �@ �@ �@�@�@�@�@�@�@�@�@�@�@�F �@ �@ �@ component �@�o��M <=�@ component �@���͂̊� --�@�g������H�̏I�� �@ �@ enf if; �@ end process; end RTL;

�R���|�[�l���g�̒��ŁC�ł��d�v�Ȃ��̂� ���s�u���b�N�iALU�j �ł��D

��1�͂ł́C���̋@�\��C�����p���Ĉȉ��̂悤�ɋL�q���܂����D

void main( void ) { �ϐ��̒�` �@�@�@�F pc = 0; flag_eq = 0; do{ �@ �@ ir = rom(pc); pc++; �@ �@ switch (opcode(ir)){ �@ //�@�ȉ��C �e���߃R�[�h�ɑΉ����鏈�� case MOV �F reg[nRegA(ir)] = reg[nRegB(ir)]�G �@ �@ �@ �@�@�@ �@ break; �@ �@ �@ case ADD �F reg[nRegA(ir)] = reg[nRegA(ir)] + reg[nRegB(ir)]�G �@ �@ �@ �@ �@ break; �@�@�@ �F case JMP �F pc = op_addr(ir); break; �@ �@ �@ �@�@�@ �F default �F break ; //�@�@�@�����̏I�� �@ �@ } �@ } while (opcode(ir) != HLT); } ������C VHDL �ŋL�q����ƁC�ȉ��̂悤�ɂȂ�܂��D

�v���O�����J�E���^ �i pc �j�̈������C��قȂ�܂����C��{�I�ɂ͓����悤�ȏ��������Ă���C

�ȒP�ɂ����̑��ݕϊ����ł��邱�Ƃ��킩��܂��D

architecture RTL of xxx is begin �@�@ process (CLK) �@ begin �@ �@ if (CLK'event and CLK = '1') then �@ �@ �@ case OP_CODE is �@ �@ �@ �@ when "0000" => �@�@�@�@�@�@�@�@�@�@�@ -- MOV �@ �@ �@ �@ REG_IN <= REG_B; �@ �@ �@ �@�@�@�@�@�@ �F �@ �@ �@ PC_OUT <= PC_IN + 1�G when "0001" => �@�@�@�@�@�@�@�@�@�@�@ -- ADD REG_IN <= REG_A + REG_B; �@�@�@�@�@�@ �F PC_OUT <= PC_IN + 1�G �@�@�@�@�@�@ �F when "1100" => �@�@�@�@�@�@�@�@�@�@�@ -- JMP PC_OUT <= OP_DATA; �@�@�@�@�@�@ �F when others => end case ; �@ �@ enf if; �@ end process; end RTL;

�ȉ��C�e�u���b�N�̃R���|�[�l���g�̏ڍׂɂ��Đ������܂��D

�R.�@�N���b�N�u���b�N

�N���b�N�u���b�N�́C1�̃R���|�[�l���g����\������Ă��܂��D

���@�� ��{�N���b�N�@ CLK �o�@�� �@�t�F�b�`�C�A�f�R�[�h�C�B���s�C�C���C�g�o�b�N�̊e�u���b�N

�ɋ�������4�̃N���b�N�M��

CLK_FT �C CLK_DC �C CLK_EX �C CLK_WB�N���b�N ��{�N���b�N�@ CLK

�ȉ��ɁC���̃\�[�X�R�[�h�������܂��Dclk_gen.vhd

-- clk_gen.vhd

-- Y.Izawa

-- H18.3.27

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.std_logic_unsigned.all;

entity clk_gen is port ( CLK : in std_logic ; CLK_FT : out std_logic ; CLK_DC : out std_logic ; CLK_EX : out std_logic ; CLK_WB : out std_logic ); end clk_gen; architecture RTL of clk_gen is

signal COUNT : std_logic_vector (1 downto 0);

begin process (CLK) begin if (CLK'event and CLK = '1') then COUNT <= COUNT + 1; case COUNT is when "00" => CLK_FT <= '1'; �@�@�@�@�@�@ CLK_DC <= '0'; CLK_EX <= '0'; CLK_WB <= '0'; when "01" => CLK_FT <= '0'; CLK_DC <= '1'; CLK_EX <= '0'; CLK_WB <= '0'; when "10" => CLK_FT <= '0'; CLK_DC <= '0'; CLK_EX <= '1'; CLK_WB <= '0'; when "11" => CLK_FT <= '0'; CLK_DC <= '0'; CLK_EX <= '0'; CLK_WB <= '1'; when others => end case ; end if ; end process ; end RTL;

�S.�@FETCH�u���b�N

�t�F�b�`�u���b�N�́C1�̃R���|�[�l���g����\������Ă��܂��D

���@�� �v���O�����J�E���^�iPC�j�̏o�� P_COUNT �i8bit�j �o�@�� �J�E���^���A�h���X�Ƃ���Program ROM�̃f�[�^ PROM_OUT �i15bit�j �N���b�N ��P���̃t�F�b�`�N���b�N CLK_FT �ȉ��ɁC���̃\�[�X�R�[�h�������܂��D

fetch.vhd

-- fetch.vhd

-- Y.Izawa

-- H18.3.27

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.std_logic_unsigned.all;

entity fetch is port ( CLK_FT : in std_logic ; P_COUNT : in std_logic_vector (7 downto 0); PROM_OUT : out std_logic_vector (14 downto 0) ); end fetch; architecture BEHAVIOR of fetch is

subtype WORD is std_logic_vector (14 downto 0);

type MEMORY is array (0 to 15) of WORD;

constant MEM : MEMORY := (

"100000000000000", -- ldl Reg0 0 "100000100000001", -- ldl Reg1 1 "100001000000000", -- ldl Reg2 0 "100001100001010", -- ldl Reg3 10 "000101000100000", -- add Reg2 Reg1 "000100001000000", -- add Reg0 Reg2 "101001001100000", -- cmp Reg2 Reg3 "101100000001001", -- je 9 "110000000000100", -- jmp 4 "111000001000000", -- st Reg0 64 "111100000000000", -- hlt "000000000000000", -- nop "000000000000000", -- nop "000000000000000", -- nop "000000000000000", -- nop "000000000000000" -- nop ) �G

begin READ_OP: process (CLK_FT) begin if (CLK_FT'event and CLK_FT = '1') then �@�@�@ PROM_OUT <= MEM(conv_integer(P_COUNT(7 downto 0))); end if; end process ; end BEHAVIOR;

�T.�@DECODE�u���b�N

�f�R�[�h�u���b�N�́C3�̃R���|�[�l���g����\������Ă��܂��D5.1�@decode.vhd

�ȉ��C�����̓��o�͂ƃ\�[�X�R�[�h�����Ɏ����܂��D

���@�� ���b�`���ꂽProgram ROM�̃f�[�^�o�� PROM_OUT �i15bit�j �o�@�� �I�y�R�[�h OP_CODE �i4bit�j ����уf�[�^�i�A�h���X�j�̃I�y�����h OP_DATA �i8bit�j �N���b�N ��2���̃f�R�[�h�N���b�N CLK_DC

-- decode.vhd

-- Y.Izawa

-- H18.3.27

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.std_logic_unsigned.all;

entity decode is port ( CLK_DC : in std_logic ; PROM_OUT : in std_logic_vector (14 downto 0); OP_CODE : out std_logic_vector (3 downto 0); OP_DATA : out std_logic_vector (7 downto 0) ); end decode; architecture RTL of decode is

begin process (CLK_DC) begin if (CLK_DC'event and CLK_DC = '1') then �@�@�@ OP_CODE <= PROM_OUT(14 downto 11); OP_DATA <= PROM_OUT(7 downto 0); end if; end process ; end RTL;

5.2�@reg_dc.vhd

���@�� Program ROM���������W�X�^A�CB�̔ԍ� N_REG_IN �i3bit�j

8�̃��W�X�^�o�� REG_0�`7 �i16bit�j�o�@�� ���W�X�^A�CB�̔ԍ� N_REG_OUT �i3bit�j

���W�X�^A�CB�̔ԍ� �ɑΉ����� ���W�X�^�̃f�[�^ REG_OUT �i16bit�j�N���b�N ��2���̃f�R�[�h�N���b�N CLK_DC

-- reg_dc.vhd

-- Y.Izawa

-- H18.3.27

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.std_logic_unsigned.all;

entity reg_dc is port ( CLK_DC : in std_logic; REG_0 : in std_logic_vector (15 downto 0); REG_1 : in std_logic_vector (15 downto 0); REG_2 : in std_logic_vector (15 downto 0); REG_3 : in std_logic_vector (15 downto 0); REG_4 : in std_logic_vector (15 downto 0); REG_5 : in std_logic_vector (15 downto 0); REG_6 : in std_logic_vector (15 downto 0); REG_7 : in std_logic_vector (15 downto 0); N_REG_IN : in std_logic_vector (2 downto 0); N_REG_OUT : out std_logic_vector (2 downto 0); REG_OUT : out std_logic_vector (15 downto 0) ); end reg_dc; architecture RTL of reg_dc is

begin process (CLK_DC) begin if (CLK_DC'event and CLK_DC = '1') then case N_REG_IN is when "000" => REG_OUT <= REG_0; �@�@ when "001" => REG_OUT <= REG_1; when "010" => REG_OUT <= REG_2; when "011" => REG_OUT <= REG_3; when "100" => REG_OUT <= REG_4; when "101" => REG_OUT <= REG_5; when "110" => REG_OUT <= REG_6; when "111" => REG_OUT <= REG_7; when others => end case ; N_REG_OUT�@<= N_REG_IN; end if ; end process ; end RTL;

5.3�@ram_dc.vhd

���@�� Program ROM������RAM�̃A�h���X RAM_ADDR �i8bit�j

8��RAM�o�� RAM_0�`7 �i16bit�j

�������}�b�v�hI/O�̓��̓f�[�^ IO65_IN �i16bit�j�o�@�� �A�h���X�Ŏw�肳�ꂽ RAM�̃f�[�^ RAM_OUT �i16bit�j �N���b�N ��2���̃f�R�[�h�N���b�N CLK_DC

-- ram_dc.vhd

-- Y.Izawa

-- H18.3.27

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.std_logic_unsigned.all;

entity ram_dc is port ( CLK_DC : in std_logic; RAM_0 : in std_logic_vector (15 downto 0); RAM_1 : in std_logic_vector (15 downto 0); RAM_2 : in std_logic_vector (15 downto 0); RAM_3 : in std_logic_vector (15 downto 0); RAM_4 : in std_logic_vector (15 downto 0); RAM_5 : in std_logic_vector (15 downto 0); RAM_6 : in std_logic_vector (15 downto 0); RAM_7 : in std_logic_vector (15 downto 0); IO65_IN : in std_logic_vector (15 downto 0); RAM_ADDR : in std_logic_vector (7 downto 0); RAM_OUT : out std_logic_vector (15 downto 0) ); end ram_dc; architecture RTL of ram_dc is

begin process (CLK_DC) begin if (CLK_DC'event and CLK_DC = '1') then case RAM_ADDR is �@�@�@ when "00000000" => RAM_OUT <= RAM_0; when "00000001" => RAM_OUT <= RAM_1; when "00000010" => RAM_OUT <= RAM_2; when "00000011" => RAM_OUT <= RAM_3; when "00000100" => RAM_OUT <= RAM_4; when "00000101" => RAM_OUT <= RAM_5; when "00000110" => RAM_OUT <= RAM_6; when "00000111" => RAM_OUT <= RAM_7; when "01000001" => RAM_OUT <= IO65_IN; when others => end case ; end if ; end process ; end RTL;

�U.�@EXEC�u���b�N

���s�iEXEC�j�u���b�N�́C1�̃R���|�[�l���g����\������Ă��܂��D

���@�� �V�X�e�����Z�b�g���� RESET

�v���O�����J�E���^�iPC) PC_IN �i8bit�j

�I�y�R�[�h OP_CODE �i4bit�j ����уf�[�^�i�A�h���X�j�̃I�y�����h OP_DATA �i8bit�j

���W�X�^�w��I�y�����h�i3bit�j �ɑΉ����郌�W�X�^�̃f�[�^ REG_A �i16bit�j�C REG_B �i16bit�j

�A�h���X�I�y�����h(8bit) �ɑΉ�����RAM�̃f�[�^ RAM_OUT �i16bit�j�o�@�� �v���O�����J�E���^�iPC) PC_OUT �i8bit�j

���W�X�^�̉��Z���� REG_IN �i16bit�j

���W�X�^�ւ̏��������M�� REG_WEN

�A�h���X�I�y�����h(8bit) �ɑΉ�����RAM�̃f�[�^ RAM_IN �i16bit�j

RAM�ւ̏��������M�� RAM_WEN

�N���b�N ��3���̎��s�N���b�N�@ CLK_EX

�ȉ��ɁC���̃\�[�X�R�[�h�������܂��D

exec.vhd

-- exec.vhd

-- Y.Izawa

-- H18.3.27

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.std_logic_unsigned.all;

entity exec is port ( CLK_EX : in std_logic; RESET : in std_logic; OP_CODE : in std_logic_vector (3 downto 0); PC_IN : in std_logic_vector (7 downto 0); REG_A : in std_logic_vector (15 downto 0); REG_B : in std_logic_vector (15 downto 0); OP_DATA : in std_logic_vector (7 downto 0); RAM_OUT : in std_logic_vector (15 downto 0); PC_OUT : out std_logic_vector (7 downto 0); REG_IN : out std_logic_vector (15 downto 0); RAM_IN : out std_logic_vector (15 downto 0); REG_WEN : out std_logic ; RAM_WEN : out std_logic ); end exec; architecture�@ RTL of exec is

signal�@ CMP_FLAG : std_logic;

begin process (CLK_EX, RESET)

beginif (RESET = '1') then PC_OUT <= "00000000" ;

elsif ( CLK_EX'event and CLK_EX = '1' ) thencase OP_CODE is when "0000" => -- MOV REG_IN <= REG_B;

REG_WEN <= '1';

RAM_WEN <= '0';

PC_OUT <= PC_IN + 1;

when "0001" =>

-- ADD REG_IN <= REG_A + REG_B;

REG_WEN <= '1';

RAM_WEN <= '0';

PC_OUT <= PC_IN + 1;

when "0010" =>

-- SUB REG_IN <= REG_A - REG_B;

REG_WEN <= '1';

RAM_WEN <= '0';

PC_OUT <= PC_IN + 1;

when "0011" =>

-- AND REG_IN <= REG_A and REG_B;

REG_WEN <= '1';

RAM_WEN <= '0';

PC_OUT <= PC_IN + 1;when "0100" =>

-- OR REG_IN <= REG_A or REG_B;

REG_WEN <= '1';

RAM_WEN <= '0';

PC_OUT <= PC_IN + 1;

when "0101" =>

-- SL REG_IN <= REG_A(14 downto 0) & '0';

REG_WEN <= '1';

RAM_WEN <= '0';

PC_OUT <= PC_IN + 1;

when "0110" =>

-- SR REG_IN <= '0' & REG_A(15 downto 1);

REG_WEN <= '1';

RAM_WEN <= '0';

PC_OUT <= PC_IN + 1;

when "0111" =>

-- SRA REG_IN <= REG_A(15) & REG_A(15 downto 1);

REG_WEN <= '1';

RAM_WEN <= '0';

PC_OUT <= PC_IN + 1;

when "1000" =>

-- LDL REG_IN <= REG_A(15 downto 8) & OP_DATA;

REG_WEN <= '1';

RAM_WEN <= '0';

PC_OUT <= PC_IN + 1;

when "1001" =>

-- LDH REG_IN <= OP_DATA & REG_A(7 downto 0);

REG_WEN <= '1';

RAM_WEN <= '0';

PC_OUT <= PC_IN + 1;

when "1010" =>

-- CMP if (REG_A = REG_B) then

�@�@CMP_FLAG <= '1';

else

�@�@CMP_FLAG <= '0';

end if

REG_WEN <= '0';

RAM_WEN <= '0';

PC_OUT <= PC_IN + 1;when "1011" =>

-- JE REG_WEN <= '0';

RAM_WEN <= '0';

if (CMP_FLAG = '1') then

�@�@PC_OUT <= OP_DATA ;

else

�@�@PC_OUT <= PC_IN + 1;

end if ;

when "1100" =>

-- JMP REG_WEN <= '0';

RAM_WEN <= '0';

PC_OUT <= OP_DATA ;when "1101" =>

-- LD REG_IN <= RAM_OUT;

REG_WEN <= '1';

RAM_WEN <= '0';

PC_OUT <= PC_IN + 1;when "1110" =>

-- ST RAM_IN <= REG_A;

REG_WEN <= '0';

RAM_WEN <= '1';

PC_OUT <= PC_IN + 1;when "1111" =>

-- HLT when others => end case ; end if ; end process ; end RTL;

�V.�@���C�g�o�b�N�u���b�N

���C�g�o�b�N�u���b�N �́C2�� �R���|�[�l���g ����\������Ă��܂��D

�ȉ��C������ �\�[�X�R�[�h �������܂��D

7.1 reg_wb.vhd

���@�� ���W�X�^�I�y�����h(3 bit) �Ŏw�肵�����W�X�^�̔ԍ� N_REG (3 bit�j

���W�X�^�̉��Z���� REG_IN �i16 bit�j

���W�X�^�ւ̏��������M�� REG_WEN

�o�@�� 8 �̃��W�X�^�̃f�[�^ REG_0�`7 �i16 bit�j �N���b�N ��4���̃��C�g�o�b�N�N���b�N�@ CLK_WB

-- reg_wb.vhd

-- Y.Izawa

-- H18.3.27

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.std_logic_unsigned.all;

entity reg_wb is port ( CLK_WB : in std_logic ; N_REG : in std_logic_vector (2 downto 0); REG_IN : in std_logic_vector (15 downto 0); REG_WEN : in std_logic; REG_0WB : out std_logic_vector (15 downto 0); REG_1WB : out std_logic_vector (15 downto 0); REG_2WB : out std_logic_vector (15 downto 0); REG_3WB : out std_logic_vector (15 downto 0); REG_4WB : out std_logic_vector (15 downto 0); REG_5WB : out std_logic_vector (15 downto 0); REG_6WB : out std_logic_vector (15 downto 0); REG_7WB : out std_logic_vector (15 downto 0) ); end reg_wb; architecture RTL of reg_wb is

begin process (CLK_WB) begin if (CLK_WB'event and CLK_WB = '1') then if (REG_WEN = '1') then case N_REG is when "000" => REG_0WB <= REG_IN; -- REG_0 when "001" => REG_1WB <= REG_IN; -- REG_1 when "010" => REG_2WB <= REG_IN; -- REG_2 when "011" => REG_3WB <= REG_IN; -- REG_3 when "100" => REG_4WB <= REG_IN; -- REG_4 when "101" => REG_5WB <= REG_IN; -- REG_5 when "110" => REG_6WB <= REG_IN; -- REG_6 when "111" => REG_7WB <= REG_IN; -- REG_7 when others => end case ; end if ; end if ; end process ; end RTL;

7.2 ram_wb.vhd

���@�� �A�h���X�I�y�����h(8 bit) �Ŏw�肵��RAM�A�h���X RAM_ADDR �i8 bit�j

�I�����ꂽ RAM �̃f�[�^ RAM_IN �i16 bit�j

RAM �ւ̏��������M�� RAM_WEN

�o�@�� RAM �̃f�[�^ RAM_0�`7 �i16 bit�j �i8��ށj

�������}�b�v�hI/O�̏o�̓f�[�^ IO64_OUT (16 bit)�N���b�N ��4���̃��C�g�o�b�N�N���b�N�@ CLK_WB

-- ram_wb.vhd

-- Y.Izawa

-- H18.3.27

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.std_logic_unsigned.all;

entity ram_wb is port ( CLK_WB : in std_logic ; RAM_ADDR : in std_logic_vector (7 downto 0); RAM_IN : in std_logic_vector (15 downto 0); RAM_WEN : in std_logic; RAM_0 : out std_logic_vector (15 downto 0); RAM_1 : out std_logic_vector (15 downto 0); RAM_2 : out std_logic_vector (15 downto 0); RAM_3 : out std_logic_vector (15 downto 0); RAM_4 : out std_logic_vector (15 downto 0); RAM_5 : out std_logic_vector (15 downto 0); RAM_6 : out std_logic_vector (15 downto 0); RAM_7 : out std_logic_vector (15 downto 0); IO64_OUT : out std_logic_vector (15 downto 0) ); end ram_wb; architecture RTL of ram_wb is

begin �@ process (CLK_WB) begin �@ if (CLK_WB'event and CLK_WB = '1') then �@ if (RAM_WEN = '1') then �@ case RAM_ADDR is �@ when "00000000" => RAM_0 <= RAM_IN; -- RAM_0 when "00000001" => RAM_1 <= RAM_IN; -- RAM_1 when "00000010" => RAM_2 <= RAM_IN; -- RAM_2 when "00000011" => RAM_3 <= RAM_IN; -- RAM_3 when "00000100" => RAM_4 <= RAM_IN; -- RAM_4 when "00000101" => RAM_5 <= RAM_IN; -- RAM_5 when "00000110" => RAM_6 <= RAM_IN; -- RAM_6 when "00000111" => RAM_7 <= RAM_IN; -- RAM_7 when "01000000" => IO64_OUT <= RAM_IN; -- IO_64 when others => end case ; end if ; end if ; end process ; end RTL;

�ȏ�C VHDL�R���|�[�l���g �̓��e�ɂ��āC�Љ�܂����D

�s���ȓ_�������ł��c���Ă���ꍇ�́C ��P�� �� ��Q�� �ɖ߂��āC

C����� �uCPU�V�~�����[�^�v ��C ��ʊK�w��VHDL �̃\�[�X�R�[�h��������x���Ӑ[���ǂݕԂ��ĉ������D

�W�D�@�܂Ƃ�

���̃R���e���c�ł́C�V���v���� CPU�̐v�@ �ɂ��ĉ�����Ă��܂����D

�����̓��e�́C�����ł��܂����ł��傤���H�@

���╪�����_�ɂ��āC�����Ɏw�E���Ă���������ƗL��ł��D

�܂��C�s���ȓ_�͉����Ȃ����₵�ĉ������D

�J��Ԃ��q�ׂĂ���悤�ɁC����� �����̗e�Ղ� �� ���i�̋��p�� ��}�邽�߁C�������𒆐S��

��H�̑啝�� �ȗ��� ���s���Ă��܂��D

�Ⴆ�C�t�F�b�`�u���b�N�� PROM �̓��e���CVHDL�̒��ŋL�q���Ă��܂����C�O���� �t�@�C�� ����

�ǂݍ��ނ̂���ʓI�ȕ��@�ł��D

�܂��C RAM �ɂ��ẮC���W�X�^�Ɠ����\���Ƃ��邽�߁C������ D�^�t���b�v�t���b�v ��p���܂����D

���Ȃ킿�C���C�g�o�b�N�u���b�N�̏o�͂��f�R�[�h�u���b�N�őI������\���ƂȂ��Ă���C

�������T�C�Y��������� �Ή��ł��܂���D

��ʂɂ́C VHDL�̔z��iARRAY�j ��CFPGA�J���c�[���� ���K�t�@���N�V���� ���̋@�\���g�p���܂��D

�z�� ��p�����ꍇ�C���̃C���f�b�N�X�� RAM�̃A�h���X �ɑΉ����܂��D

�܂��C�t�F�b�`�u���b�N�̃A�h���X�o�͂� RAM�̃A�h���X �ɓ��͂��CRAM�ւ̏������݂́C

���C�g�o�b�N�̃t�F�[�Y�ōs���܂��D

����ɂ��C�R���|�[�l���g�Ԃ̐M���̎n���� �P���� ����C ��e�ʉ� �ɂ��Ή��ł��܂��D

�����̏ڍׂɂ��ẮC ��4�� �Ő������܂��D

����C CPU�̍�������@ �����邱�Ƃ��ł��܂��D

�Ⴆ�C�e�u���b�N�̃^�C�~���O�����邱�Ƃɂ��C �u�p�C�v���C�������v �������\�ł��D

���̂悤�Ȗ{�i�I�� CPU�̐v�@ �ɂ��ẮC ��5�� �Ő������܂��D

�{���������p���āC �I���W�i����CPU ��v���邱�Ƃ������߂��܂��D

�v���ē��삵���Ƃ��̊�т͑��ɑւ����������̂ł���C�����œ������M��o���́C

���� �g�ݍ��݃V�X�e�� �� �v���Ő�������邱�Ƃł��傤�D