VHDL�ɂ���

�| �v���Z�X���ƃ^�C�~���O �|

���V�@�T�i

(H19.5.23)

�P. �����������Ə����������D

- VHDL�ɂ́C�u

����������

�v�ƁC�u

����������

�v������܂��D

- �u

architecture

�v�{�̂ɂ́C�u

����������

�v�����ɋL�q���܂��D

- ���ۂ̘_����H�́C��Ɂu

active�ȏ��

�v�ɂ��邽�߁C�{���u

����������

�v�ŕ\������̂����R�ł��D

- �u

����������

�v�ɑ��āC�u

����������

�v������܂��D

- �u

����������

�v�́C�\�t�g�E�F�A�́u

�����I�ȍ\��

�v��p���āC�u

�n�[�h�E�F�A�̃��f�����O

�v���s�����̂ł���C

�����������ɔ�ׁC�u

��蒊�ۓI�ȓ���

�v�ϓI�ɋL�q���邱�Ƃ��\�ł��D

- ���������u

�v���Z�X��

�v�̓����́C���́u

����������

�v���g�p����܂��D

- �Ⴆ�C�u

if��

�v��u

case��

�v�C�u

loop��

�v�Ȃǂ��C���̑�\�I�Ȃ��̂ł��D

- �u

����������

�v�C�u

����������

�v�Ƃ����̂́C�����܂�VHDL�́u

�\������͂��āC��������菇

�v���C

- �u

�������s

�v�C

���邢�́u

����

�v��\���Ă���̂ł���C

- �@�@�u

�M���������ɕω����邩�C���Ȃ���

�v

- ��\���Ă���̂ł͂Ȃ����ƂɁC���ӂ���K�v������܂��D

- ����

�g������H�̗��p���āC��̓I�ɐ������܂��傤�D

| entity

inverter

is |

|

port

( |

|

|

A |

: |

in |

std_logic; |

|

|

B |

: |

out |

std_logic�G |

|

|

C |

: |

out |

std_logic |

|

); |

| end

inverter; |

| architecture

Dataflow

of

inverter

is |

| begin |

|

B

<=

A; |

���������� |

|

C

<=

B; |

���������� |

| end

Dataflow; |

|

- �u

architecture

�v��2�̑�����C

- �@ B�@<=�@A;

- �@�@�@�ƁC

- �@ C�@<=�@B;

- �́C�Ƃ��Ɂu

����������

�v�Ƃ��ĉ�͂���܂��D

- �u

�M��B�ւ̑��

�v�́C�u

�M��A�̕ω�

�v����u

1���Ԍ�

�v�ɍs���܂��D

- ����C�u

�M��C�ւ̑��

�v�́C�u

�M��B�̕ω�

�v����u

1���Ԍ�

�v�C���Ȃ킿�C

- �u

�M��A�̕ω�

�v����u

2���Ԍ�

�v�ɍs���܂��D

- ���̂悤�ɁC�u

�M���ւ̑��

�v�́C�K�����������ɍs����Ƃ͌���܂���D

- �Ȃ��C�u

�x�����ԃ�

�v�̒l�́C�u

0

�v�ł���C�����I��

�x���͂���܂���D

- ���Ȃ킿�C��LVHDL�ł͉�H�̋@�\���L�q���Ă��邾���ł���C

- ��̓I�ȉ�H�́u

�x�����ԃ�

�v�̒l�ɂ��ẮC

�g�p����u

���C�u����

�v ��C

- �u

FPGA�̎��

�v �ȂǁC�u

�_������

�v�̌��ʂɂ�茈�܂�܂��D

- �u

�e�X�g�x���`

�v�ȂǂŁu

0�ȊO�̒x����

�v��ݒ肷��ɂ́C�ȉ��̂悤�ɋL�q���܂��D

|

B

<=

A after 5ns; |

|

|

C

<=

B after 10ns; |

|

- ����́C�u

�M��A

�v���ω����āu

5ns��

�v�Ɂu

�M��B

�v���ω����邱�Ƃ�\���Ă��܂��D

- ���l�ɁC�u

�M��B

�v���ω����āu

10ns��

�v�Ɂu

�M��C

�v���ω����܂��D

�Ȃ��C2�̑�����́u

�ʒu�i�O�E��j

�v����ꊷ���Ă��C�u

����

�v�ł��邱�Ƃ͖��炩�ł��D

�Q.�@�v���Z�X���ɂ��āD

- ��ɏq�ׂ��悤�ɁC�u

architecture

�v�{�̂ɂ́C�u

����������

�v�����ɋL�q���܂��D

- ���̗�Ɏ����悤�ɁC�v���Z�X�����܂܂��ꍇ���C

- �@�@process(CLK)

����

end process�G

- �܂ł̋L�q���C1�́u

����������

�v�Ƃ݂Ȃ����Ƃ��ł��܂��D

| signal

TMP

:

std_logic_vector(3

downto

0); |

|

|

|

|

process

(CLK) |

�b |

|

begin |

�b |

|

|

if

(CLK'event

and

CLK = '1')

then |

�b |

|

|

|

if

TMP =

"1001"

then |

�b |

|

|

�@ |

|

TMP <=

"0000"

; |

�b ���������� |

|

|

|

else |

�b |

|

|

|

|

TMP <= TMP + 1; |

�b |

|

|

|

end if

; |

�b |

|

|

end if

; |

�b |

|

end process

; |

�b |

|

�@ |

|

|

COUNT <= TMP; |

�@�@���������� |

| end

Behavior; |

|

- ���������āC�M���u

COUNT

�v�ւ̑�����̈ʒu�͂ǂ��ł��悭�C

- ���̐}�̂悤�ɁC�u

�v���Z�X��

�v�Ƃ��̈ʒu����ꊷ���Ă������ł��D

|

signal

TMP

:

std_logic_vector(3

downto

0); |

|

|

|

|

COUNT <= TMP; |

�@�@���������� |

|

�@ |

|

|

process

(CLK) |

�b |

|

begin |

�b |

|

|

if (CLK'event and

CLK = '1') then |

�b |

|

|

|

if

TMP = "1001"

then |

�b |

|

|

�@ |

|

TMP <= "0000"

; |

�b ���������� |

|

|

|

else |

�b |

|

|

|

|

TMP <= TMP + 1; |

�b |

|

|

|

end if

; |

�b |

|

|

end if

; |

�b |

|

end process; |

�b |

| end

Behavior; |

|

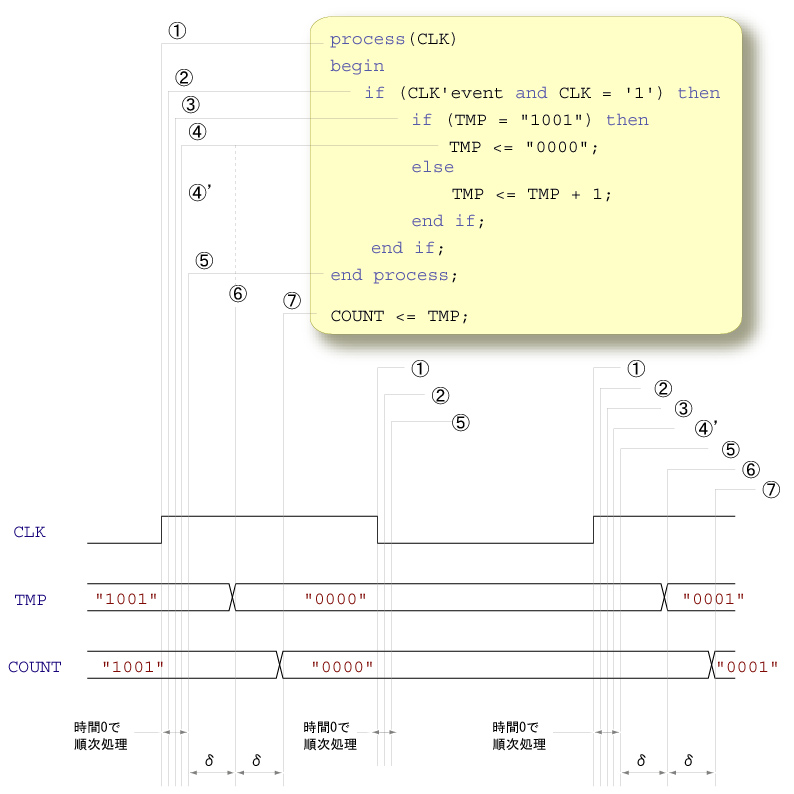

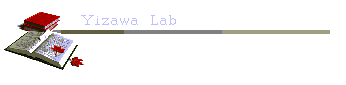

- ���ɉ��̐}��p���āC

����������

���L�q����

�v���Z�X��

��

�^�C�~���O

�̊W�ɂ��āC

- �������Ă݂܂��傤�D

- ���̗�́C

- �@process(CLK)

����

end process;

- �܂ł̂P��

�v���Z�X��

�ƁC

- �@COUNT <= TMP;

- �Ƃ����P�̑�����ō\������Ă��܂��D

- ���Ȃ킿�C�Q�́u

����������

�v���܂܂�Ă��܂��D

- �u

�v���Z�X��

�v����̃J�b�R���́u

�M��

�v���u

�Z���V�e�B�r�e�B�E���X�g

�v�ƌĂсC

- ���̒l���ω������Ƃ��C���̃v���Z�X���u

�A�N�e�B�u

�v�ƂȂ�C�A�`�D�̏������s���܂��D

- �A�ŁCCLK�̕ω����u

�������

�v�ł���ꍇ�́C�B�ȍ~�̏������s���܂��D

- ����C�u

��������

�v�ł���ꍇ�́C�D�Ɉڍs���C�v���Z�X�́u

�X�^���o�C���

�v�ƂȂ�܂��D

- �B�ł́C�u

�M��TMP

�v�̏�ԂׁC���̒l���u

"1001"

�v�̂Ƃ��́C�u

���Ԍ�

�v�C

- �u

�M��TMP

�v��

�u

"0000"

�v��������悤�C�X�P�W���[�����O���s���܂��D

- ����C�u

�M��TMP

�v�̒l���u

"1001"

�v�ȊO�̂Ƃ��́C

�u

�M��TMP

�v�̒l�ɁC

- �u

1�����Z�����l

�v���u

���Ԍ�

�v�ɑ������悤�C�X�P�W���[�����O���܂��D

- �u

�X�P�W���[�����O

�v���I�������C�D�Ɉڍs���C�v���Z�X�́u

�X�^���o�C���

�v�ƂȂ�܂��D

- �����Łu

�̒l

�v�́u

0

�v�ŁC�u

�x���͂Ȃ�

�v�̂ł����C�u

�v���Z�X���I��

�v������ɁC

- ������s���邱�Ƃɒ��ӂ��ĉ������D

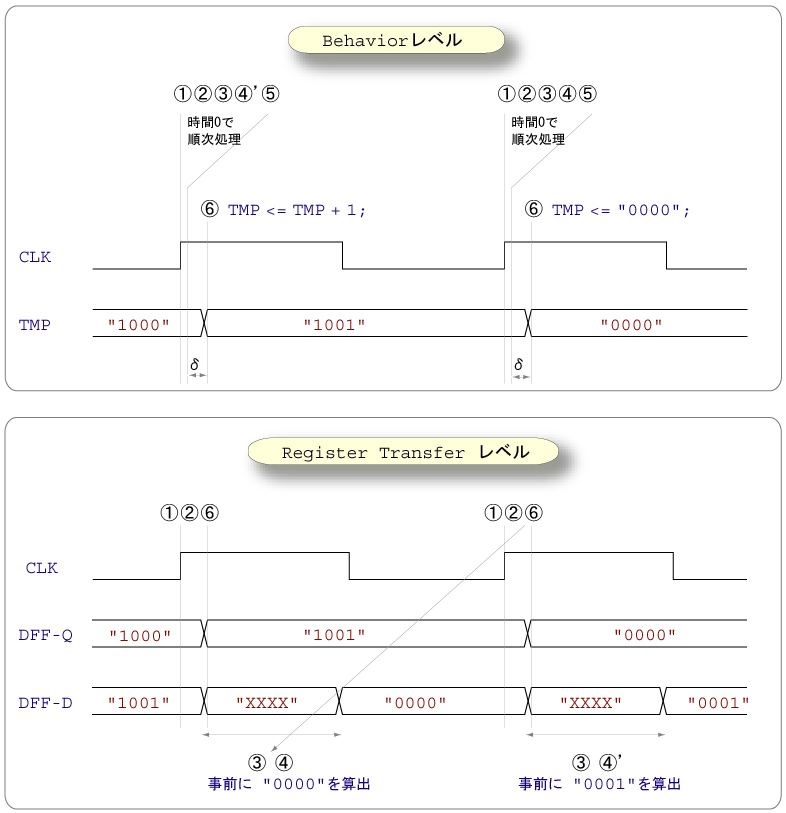

�R.�@Behavior ���x���� Register Transfer ���x���D

- �O�߂�VHDL�́u

architecture�̎d�l

�v�́C�u

Behavior

�v�ƂȂ��Ă��܂��D

- �g�b�v�_�E���v�ł́C�܂��u

Behavior���x���̋L�q

�v���s���C�V�X�e���̑S�ʓI�ȋ@�\���m�F���܂��D

- �u

Behavior���x��

�v�̃V�~�����[�V�����ł́C

������u

�C�x���g�E�h���u��

�v�Ƃ�����@�ɂ��C

- �u

�M������̃^�C�~���O

�v�������I�Ɍv�Z���܂��D

- �Ⴆ�C�M���́u

CLK

�v���ω������Ƃ��C�u

end process;

�v�܂ł̏������C�u

����0

�v�ŏ����Ɏ��s���܂��D

- �������C���̂悤�ȏ����́u

�\�t�g�E�F�A�ɂ��V�~�����[�V����

�v��Ő���������̂ł��D

- �Ⴆ��10�i�J�E���^�ŁC�u

�M����TMP

�v�̒l���Ăяo���C����Ɂu

1�����Z

�v���邽�߂ɂ́C

- 4bit��1bit�̉��Z�ɔ������Z���Ԃ��K�v�ł��D

- �Q�[�g�x�������ۂ́u

�n�[�h�E�F�A

�v�Ŏ����ł�����̂ł͂���܂���D

- ���Ȃ킿�C������e�X�g�x���`��ŁC�u

����d�l

�v�Ɋ�Â��_�����{�I�ȃ^�C�~���O�Ɋւ���

- �V�~�����[�V�������s���̂��ړI�ƂȂ�܂��D

- �u

Behavior���x��

�v�̌����I����ƁC

�u

VHDL�̃��C�u����

�v����p���āC

- �u

Register Transfer���x��

�v�̋�̓I�ȉ�H�\���ɕϊ����C�����̃^�C�~���O�������Ɍ����܂��D

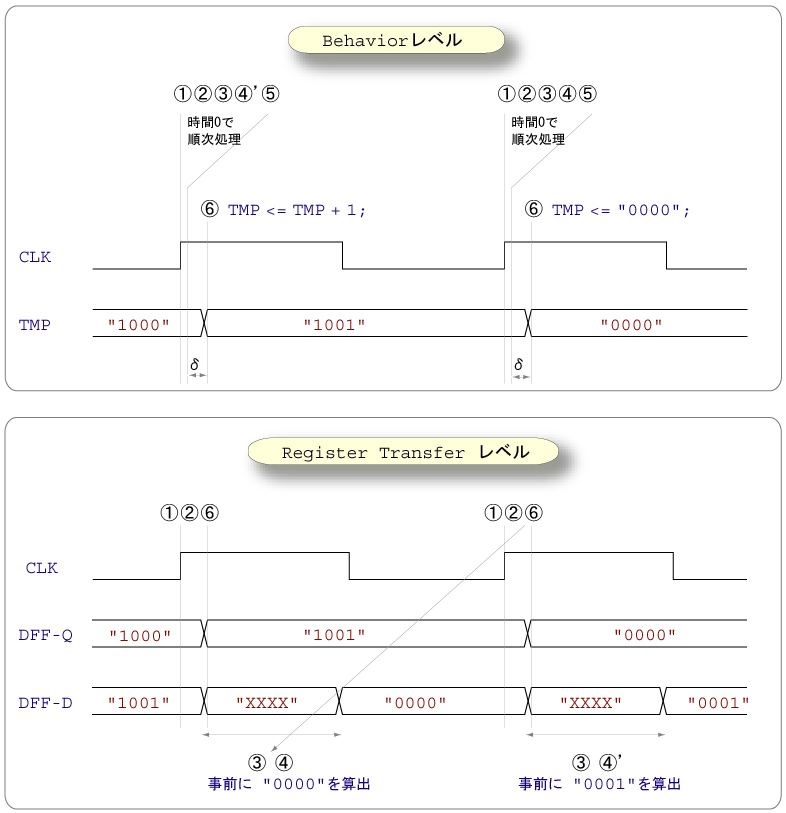

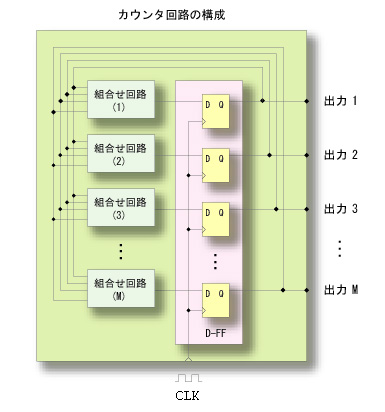

- ���̐}��p���āC�u

Register Transfer ���x��

�v�̉�H�̓���ɂ��Đ������܂��傤�D

- �u

Behavior���x��

�v�ł́C�N���b�N�̗�����肪�u

���ׂĂ̋N�_

�v�ƂȂ��Ă��܂����D

- �u

�M��TMP�ւ̑��

�v�́C�N���b�NCLK�̗�����肩��u

���Ԍ�

�v�ɍs���܂��D

- �Ƃ������Ƃ́C�u

�M��TMP�̒l

�v�́C�ق�1�N���b�N�O�ɁC���łɊm�肵�Ă��邱�ƂɂȂ�܂��D

- �u

RT���x��

�v�ł́C�u

�M��TMP�̒l

�v���m�肵�����_���u

�N�_

�v�Ƃ��܂��D

- ���Ȃ킿�C�u

TMP�̒l���`�F�b�N

�v������C�u

TMP�̒l��1�����Z

�v���鏈�����C

- �قځu

1�N���b�N�O

�v����J�n���C

���̌��ʂ��C�u

�t���b�v�t���b�v

�v�́u

D-FF

�v��p���āC

- �N���b�N�u

CLK

�v�̗������Ŋm�肵�܂��D

- �u

D-FF

�v�̉����͔�r�I�����̂ŁC�u

Behavior���x��

�v�ɋ߂��V�~�����[�V�������ʂ������܂��D

- �u

RT���x��

�v�̉�H�v�ł́C�u

TMP�̒l���`�F�b�N

�v������C�u

TMP�̒l��1�����Z

�v���鏈���́C

- ���ׂāu

�g������H

�v�Ŏ������܂��D

- ���Ȃ킿�C���̐}�Ɏ����悤�Ɂu

1�N���b�N�O��TMP

�v�̒l���u

�g������H

�v�ɓ��͂��C

- ���̏o�͂��u

D-FF

�v��p���āC�g�`���`���܂��D

- ���̂悤�ȉ�H�\���ɂ��C�u

D-FF

�v�̏o�͂́C�u

Behavior���x��

�v�̐v�Ɠ��l�C

- �u

CLK�̗������

�v����ɕω�����M���ƂȂ�܂��D

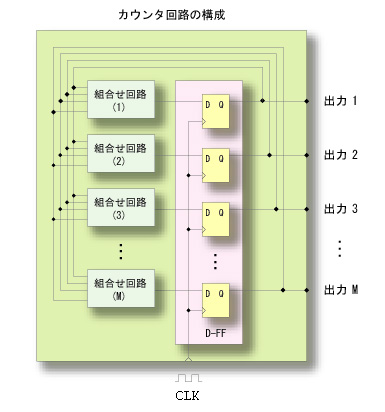

�S.�@�v���Z�X���ɂ��g������H�D

- ���ׂẮu

�g������H

�v�́C�u

����������

�v�ŕ\���ł��܂����C

- �����u

����������

�v���g����

�u

�v���Z�X��

�v��p���ċL�q����邱�Ƃ�����܂��D

- �u

if-else��

�v��

�u

case��

�v����p���āC��H�̋@�\��₷���\�����邱�Ƃ��ł��邽�߂ł��D

- ���̂Ƃ��C�ȉ���2�_�ɒ��ӂ���K�v������܂��D

- �@

�u

�Z���V�e�B�r�e�B�E���X�g

�v �Ɂu

���ׂĂ̓��͐M��

�v ���C

����Ȃ��L�q���邱�ƁD

- �A�@�u

���͂̂��ׂĂ̏��

�v�ɑ���o�͂̒l���C����Ȃ��L�q���邱�ƁD

- �u

���̏�������������Ȃ��Ƃ�

�v�C���͂̕ω��ɏo�͂��������Ȃ����Ƃ�����C

- ���ʓI�Ɂu

���b�`�@�\

�v�����ߍ��܂�Ă��܂����Ƃ�����̂ŁC���ӂ��K�v�ł��D

- �v���Z�X���́u

�Z���V�e�B�r�e�B�E���X�g

�v�́C���̐M�����u

�ω�

�v�����Ƃ��C

- ����ȉ��́u

����������

�v�����s����܂��D

- ���������āC��L�@�ƇA�̏�������������Ă���C�u

���͐M���̕ω�

�v�ɑ��C

- �K���u

�o�͐M���ւ̑��

�v���s���邽�߁C�����I�Ɂu

�x����H

�v���\������܂��D

- �Ƃ��낪�C�u

���͐M�����ω�

�v�����C�u

�o�͐M���ւ̑��

�v���s���Ȃ��ꍇ�́C

- �u

�v���Z�X

�v�I����C�����I�Ɂu

�X�^���o�C���

�v�ƂȂ��Ă��܂��̂ŁC���͐M���ɒǐ��ł��܂���D

- ���̂��߁C���́u

�o�͂̒l

�v��ێ����邽�߂́u

���b�`��H

�v ����������Ă��܂��킯�ł��D

- �u

�v���Z�X��

�v ��p���āu

�g������H

�v ���L�q����ꍇ�́C��L�u�Q����

�v �����Ă��邩�C

- �K���m�F����悤���ĉ������D

�T.�@�M���ƕϐ��ɂ��āD

- �����ł́C�u

�M���@signal

�v�ƁC�u

�ϐ��@variable

�v�̈Ⴂ�ɂ��Đ������܂��D

- �������������ʂ��C�u

���̕\

�v�Ɏ����܂��D

|

VHDL |

���ԓI�v�f |

����\�� |

�Ӂ@�� |

| �M�� |

signal |

���� |

<= |

�n�[�h�E�F�A�I |

| �ϐ� |

variable |

�Ȃ��i���Ԓl�j |

:= |

�\�t�g�E�F�A�I |

- �u

�M��

�v�́C�u

�z��

�v��u

D-FF

�v�ŕ\�����u

�n�[�h�E�F�A

�v�ł��D

- �u

�������

�v�ɂ��u

�X�P�W���[�����O

�v���s���C

���̒x���i0���܂ށj�̌�ɁC

���̒l�͕ω����܂��D

- ����́u

�ϐ�

�v�́C�u

�R���p�C�����̃\�t�g�E�F�A����

�v�ŗ��p�����ꎞ�I�ȕϐ��ł���C

- �M���̂悤�ȁu

����

�v�������Ȃ����Ƃɒ��ӂ��ĉ������D

�U. �܂Ƃ߁D

- �{�����ł́C�u

VHDL

�v�Ŏg�p�����u

�v���Z�X��

�v�Ƃ��́u

�^�C�~���O

�v�̊W�𒆐S�ɉ�����܂����D

- �u

VHDL

�v�́C�u

�\�t�g�E�F�A

�v�I�ȗv�f�ƁC�u

�n�[�h�E�F�A

�v�I�ȗv�f�����˔���������ł���C

- ���̗��p���l�͋ɂ߂č����̂ł����C��������ʂ�����ƌ����Ă��܂��D

- �{�������C�����̈ꏕ�ƂȂ邱�Ƃ�����Ă��܂��D

- �Ȃ��C�u

���

�v��u

�������₷���L�q

�v������܂�����C���[�����ł��A������������K���ł��D