コンピュータ・アーキテクチャ [補足資料]

コンピュータの構成

-

井澤 裕司

-

1. はじめに

-

-

ここでは

「コンピュータアーキテクチャ」

に関する補足資料を示します。

-

-

-

本節では、

「コンピュータの全体構成」

について、その概要を説明します。

-

なお、各部の詳細については、稿を改めて解説します。

-

コンピュータの内部にも関心をもち、それらの構造や機能への理解を深めるよう学習して下さい。

-

-

解りやすい説明を心がけたつもりですが、不明な点、あいまいな点、誤り等がありましたら、

-

お手数ですが

メール等で井澤(e-mail : yizawa.cs@gmail.com)までお知らせ下さい。

-

-

本資料が有効に活用されることを願っています。

-

2. コンピュータの全体構成

-

-

ここでは、デスクトップ型のパーソナルコンピュータの全体構成について解説します。

-

-

下の図に示すように、コンピュータは本体とキーボード、マウス、モニタ等で構成されます。

-

-

図のコンピュータ本体は、フルタワー型と呼ばれ、サーバ等を構築するため、多くの拡張

-

スロットや多数のハードディスク等を内蔵するためのスペースが確保されており、拡張性

-

を考慮して大型の筐体が用いられています。

-

この他、用途により中規模のミドルタワー型、小型のミニタワー型が使用されます。

-

-

コンピュータ本体の前面には、CD-ROMやフロッピーディスクドライブ等が実装されます。

-

本体後部には、入力装置のキーボードとマウス、出力装置のモニタテレビや液晶ディスプレイ

-

を接続するコネクタが用意されています。

-

-

さらに、インターネットを利用する場合は、EthernetをはじめとするLANカードを実装したり、

-

ADSL等のモデムをシリアルポートやUSB(Universal Serial Bus)ポートに接続します。

-

-

また、印刷用のプリンタは、パラレルポートやUSBポートに専用ケーブルを接続して使用

-

します。

-

-

-

-

-

それでは、コンピュータ本体の内部はどのような構造になっているのでしょうか?

-

コンピュータ本体の筐体を開けて、その内部を覗いてみましょう。

-

3. コンピュータ本体の構成

-

-

-

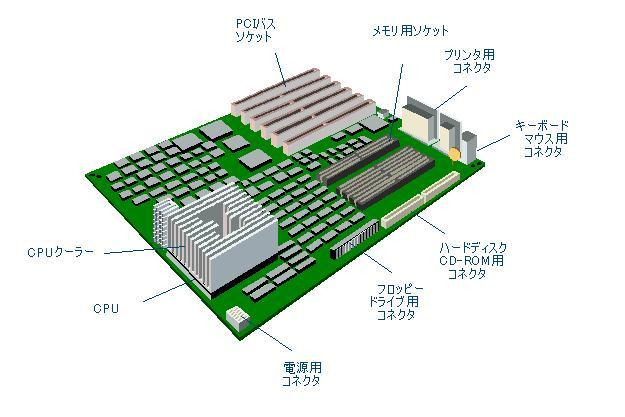

3.1 マザーボード

-

-

筐体内部には、CD-ROMやフロッピーディスクドライブ、ハードディスク、電源等のハードウェア

-

が内蔵され、それらは専用のケーブルで接続されています。

-

-

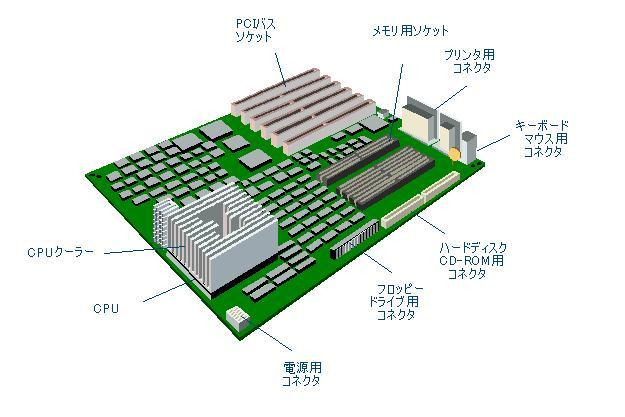

その中で最もサイズが大きく、重要な機能を果たすのが

「マザーボード」

と呼ばれる基板です。

-

下の図にその概観を示します。

-

この基板は多層になっており、CPUをはじめとするいくつかのLSIや多種多様のソケット、コネクタ

-

類が実装されています。ソケットやコネクタの電極は、基板表面もしくは内部層のプリント配線に

-

より、電気的に接続されています。

-

-

CPUは言うまでもなくコンピュータの頭脳に当たるVLSIであり、内部の回路は数百MHzから

-

数GHzの極めて高い周波数のクロックで動作しています。

-

一般に、クロックの周波数が高くなるほど処理能力も向上しますが、多量の熱を発生させるので、

-

パッケージの表面に、CPUクーラーあるいはヒートシンクと呼ばれる冷却装置が装着されています。

-

-

CPUを動作させるためには、データを一時的に保存するメモリが必要です。

-

代表的なメモリにSDRAM(Synchronous DRAM)があります。このメモリは、ダイナミックRAMの

-

一種であり、連続するアドレスのデータをバースト的に読み書きすることにより、高速化されてい

-

ます。このメモリを実装するためのソケットが、DIMM(Dual Inline Memory Module)ソケットです。

-

-

ディスプレイ用のグラフィックボードやネットワークカード、サウンドカード等を、自由に拡張できるよ

-

うに、PCI(Peripheral Component Interconnect)バスソケットが用意されています。

-

このPCIバスにはプラグ・アンド・プレイ機能が実装されており、新規に拡張カードを増設すると、

-

OSがメーカーや機種名、必要なメモリサイズ等を自動的に認識して、必要なソフト(デバイスドライ

-

バ)をインストールする準備をします。

-

最近のマザーボードには、ディスプレイの高速化を図るため、PCIの数倍のデータ転送速度をもつ

-

AGP(Accelerated Graphics Port)と称する専用のソケットが1つ設けられています。

-

-

一方、専用のケーブルを用いて様々なデバイスを接続するためのコネクタ類が用意されています。

-

例えば、キーボードやマウスを接続するのが、PS2コネクタです。これは一種のシリアルポートであり、

-

最近はより高速なUSBポートに移行しつつあります。

-

このUSBポートには、1.5Mbps と 12Mbps の2種類があり、従来のRS-232Cに比べ1桁以上高速化

-

されています。ハブ(HUB)を接続すれば、増設することも可能です。

-

-

ハードディスクと接続するためのIDEコネクタは、CD-ROMやDVDの接続にも使用されます。

-

フロッピーディスクドライブ用のコネクタは、独自の仕様になっています。

-

また、プリンタを接続するパラレルポート用コネクタや、モデム等を接続するシリアルポート、USB

-

ポート等が設けられています。

-

-

電源コネクタからは、 5Vと12Vの直流電圧がマザーボードに供給されます。

-

-

-

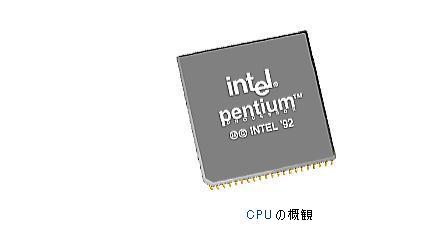

3.2 CPU

-

-

CPUはCentral Processing Unitの略で、中央処理装置を意味します。

-

よく似た名称にMPU(Micro Processing Unit)がありますが、これはマイクロプロセッサを指します。

-

マルチプロセッサ方式の特殊なコンピュータを除き、通常のパソコンには1つのMPUが実装されており、

-

これらはほぼ同義語になっています。

-

-

CPUの処理速度と消費電力は、トレードオフの関係にあります。

-

すなわち、処理速度を向上させるため高い周波数のクロックで動作させると、消費電力も大きくなり、

-

冷却効果の高いCPUクーラーが必要になります。

-

ノートパソコンは、充電式の2次電池を用いるため、処理速度と消費電力のバランスが重要になります。

-

このように、CPUには処理能力志向タイプから省電力タイプまで、様々な性能・仕様のものがあり、

-

用途により使い分けられています。

-

-

CPUの内部には、クロック逓倍回路が組み込まれており、マザーボードの水晶振動子を用いて発振

-

した66MHz(100MHz)の基本クロックを入力すると、内部でその整数倍のクロックが生成され、各回

-

路に供給されます。

-

-

CPUは下の図に示すように、数百のピンをもつセラミック製のパッケージ(PGA:Pin Grid Array)に

-

収められています。ピンの数はCPUの種類により、478、423など様々で、これらを実装するソケット

-

の形状も異なります。

-

薄型のノートパソコンでは実装面積等の制約から、PGAではなくBGA(Ball Grid Array)が用いられ

-

れることもありますが、ボール状のハンダを熔かして溶着するため、基本的に取り外しはできません。

-

-

CPU(MPU)の進歩は留まることがなく、世界初のMPU4004のトランジスタ数が2000程度であった

-

のに対し、現在は1000万に達しています。

-

この進歩は、1年半に2倍という「ムーアの法則」として知られており、基本的には半導体の微細

-

加工技術によるところが大きいといえます。最新のCPUは、0.13μmの半導体プロセスで製造さ

-

れています。この微細加工技術も着実に進んでおり、2004年には、クロックが10GHzに達するも

-

のと予想されています。

-

しかし、クロックの周波数にほぼ比例して発生する熱の問題等、解決すべき課題も残されています。

-

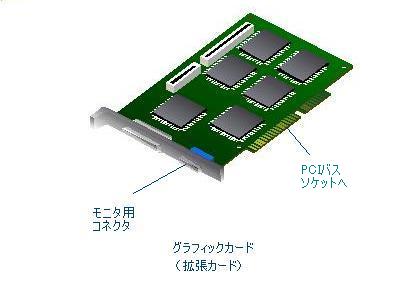

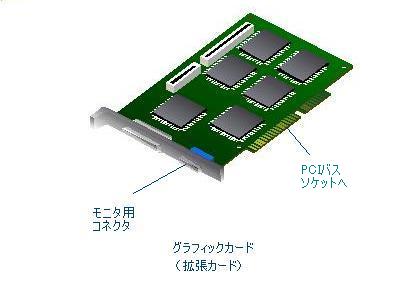

3.3 グラフィックボード(グラフィックカード)

-

画像を表示するのがグラフィックボードです。このボードではCPUから送られたデータに基づき、表示

-

画像に対応するグラフィックメモリ上に、文字や画像データを書き込みます。これを一定の周波数で、

-

RGB(赤、緑,青)のアナログ信号に変換し、モニタ上に表示します。

-

-

特殊なサーバ類を除き、現在のパソコンにはGUI(Graphical User Interface)が組み込まれています。

-

このGUIは、パソコンの画面上のアイコンやメニュー、ダイヤログ等をマウスを用いて指示するものです。

-

アイコンやメニューは2次元の画像で構成されており、これらをリアルタイムに移動したり、更新する必要

-

があります。かつてのDOSのように、文字を定められた位置に表示する場合に比べると、表示に要する

-

データ処理の量は桁違いに増加します。このため、CPUとグラフィックボード間を接続する高速のバスが

-

必要となり、PCIをはじめとする高速バスが開発されました。

-

-

さらに、マルチメディア関連のアプリケーションで、動画像をリアルタイムに表示する機能が不可欠に

-

なり、PCIの数倍のデータ伝送能力を有するAGPと称する超高速バスが導入されました。

-

最近のマザーボードには、このAGP専用のソケットが設けられています。

-

-

一方、ゲームや設計用CAD等のアプリケーションで、3次元画像をリアルタイムに生成する機能が

-

求められるようになりました。このような3次元表示では、膨大な量の3次元の座標変換や画像変換

-

処理をリアルタイムに行う必要があります。

-

しかし、CPUでこれらの処理を行うのには自ずから限度があります。

-

最近のグラフィックボードには、これらの変換処理を専用ハードウェアで実行する3次元画像処理機能

-

が実装されています。

-

-

-

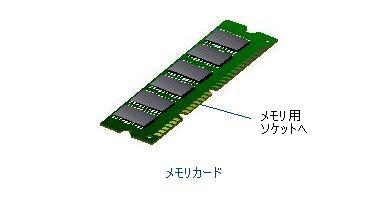

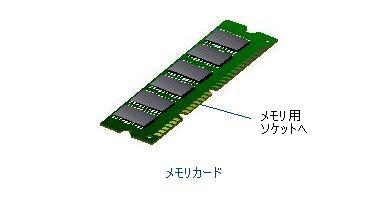

3.2 メモリカード

-

-

メインメモリには、ダイナミックRAMを実装したSDRAM(Synchronous DRAM)が用いられています。

-

このSDRAMでは、アドレスが連続するデータをバースト的に読み書きすることにより、キャッシュ

-

メモリ間のデータ伝送時間を大幅に短縮することができます。

-

SDRAMは下の図に示すような168ピンのメモリカードとなっており、マザーボードのDIMM(Dual Inline

-

Memory Module)ソケットに装着して使用します。

-

-

一般的なSDRAMのクロック周波数は、100MHz~133MHzであり、より高速なRDRAM(Direct

-

Rambus DRAM )も導入され始めています。

-

-

この一方で、クロック信号を差動入力化することにより、高速化を図ったDDR-SDRAM方式も普及

-

し始めています。このメモリはピン数が184のDIMM仕様になっているため、これまでのSDRAMとの

-

互換性はありません。

-

-

このように、メインメモリを高速化する技術開発は精力的に行われていますが、CPUのクロック

-

周波数との開きは広がる一方であり、この間を埋めることが大きな課題となっています。

-

-

-

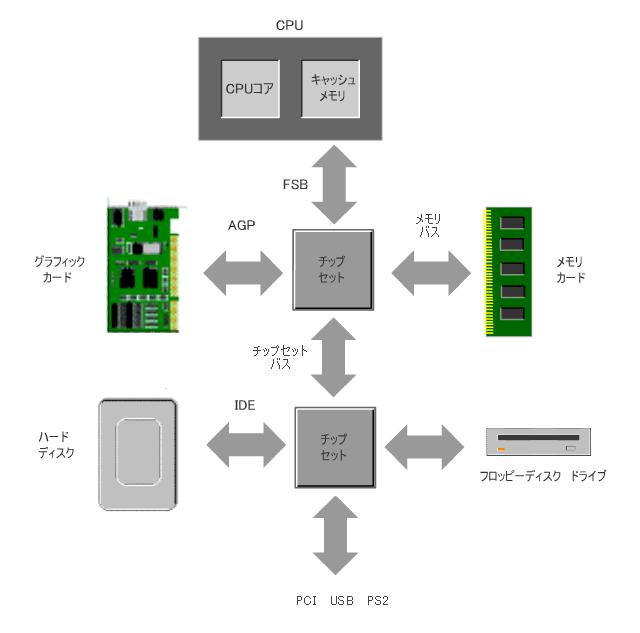

4. マザーボードの構成

-

-

ここでは、マザーボードの構成について、解説します。

-

-

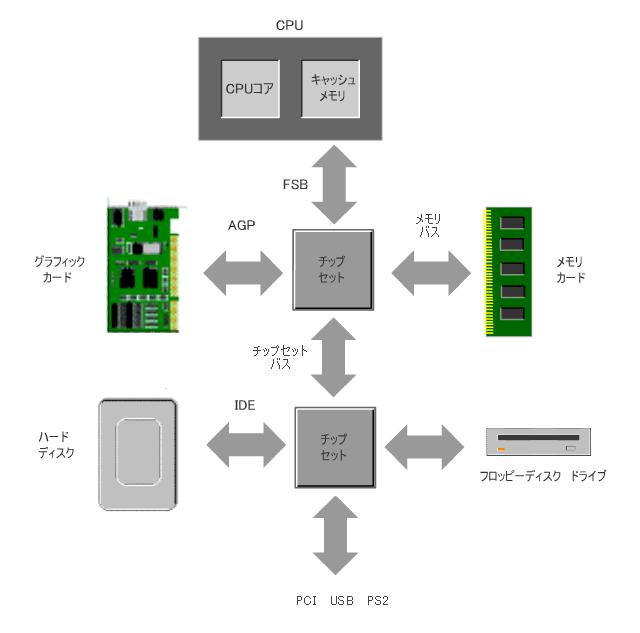

マザーボード上には、CPU(中央処理装置)と、データを記憶・保存する各種デバイスや、

-

様々な入出力機器を制御するための回路を内蔵したLSI(これをチップセットと言います)

-

が実装されています。

-

-

一般に、高速メモリの容量は少なく、逆に容量が大きいメモリは動作速度が遅いという問題

-

があります。このように2つの条件が両立し得ず、最適な解が中間的な条件となるとき、

-

「メモリの速度と容量はトレードオフの関係にある」

と言います。

-

-

マザーボードでは、CPUの近くには小規模ながら高速なメモリを、遠くには低速ながら大容量

-

の記憶装置を配置します。

-

最も高速なメモリが1次キャッシュ、その次に高速なメモリが2次キャッシュ、メインメモリという

-

順になっています。

-

最新のCPUでは、1次と2次のキャッシュメモリは、CPU内部すなわち、CPUの半導体チップ上

-

に実装されています。キャッシュメモリの大きさはCPUにより異なりますが、1次キャッシュは

-

64KB、2次キャッシュは256~512KB程度です。

-

-

CPUとメインメモリとのデータ入出力を担当するのが、いわゆる

ノースブリッジ

と呼ばれる

-

チップセットです。

-

これらを接続しているのが、FSB(Front Side Bus)という高速バスで、通常100MHz~

-

400MHzのクロックで動作します。(最近では、533MHzに達しています。)

-

バス幅は64bitで、データ伝送速度は最大800MB/s~3.2GB/sになります。

-

-

このノースブリッジには、

-

-

(1) AGP(Accelerated Graphics Port)というバスを経由したグラフィックカード

-

(2) DRAMを高速化したSDRAM等のメモリカード

-

(3) もう1つのチップセットであるサウスブリッジ

-

-

がそれぞれ異なる仕様のバスにより接続しています。

-

-

以下、簡単に補足します。

-

-

AGP(Accelerated Graphics Port)は、それまで高速とされていたPCI(Peripheral

-

Component Interconnect)というバスを高速化したグラフィックカード専用のデータバスです。

-

当初、このPCIの133MB/sという伝送速度は十分過ぎる性能と見なされていましたが、

-

MPEG2をはじめとする動画を滑らかに表示するアプリケーションが利用されるようになり、

-

より高速な性能の画像表示専用バスが求められるようになりました。

-

-

このAGPバスは、基本的にはPCIバスのデータとアドレスをそれぞれ独立した配線に分離し、

-

伝送速度の高速化を図った仕様になっています。

-

さらに、グラフィックコントローラが直接メインメモリにアクセスすることができます。

-

これにより3次元のポリゴンに、大容量の2次元画像を貼り付ける「テクスチャマッピング処理」

-

が実現され、リアルな3次元画像の表示が可能になります。

-

最近の仕様では、クロック周波数がPCIの4倍の266MHz、伝送速度は最高1.06GB/sに

-

達しています。

-

-

メインメモリには、DRAMを高速化したSDRAM(Synchronous DRAM)、あるいはさらに

-

高速なRDRAM(Direct Rambus SDRAM)が用いられています。

-

SDRAMはバス幅が64bitであり、100MHz~133MHzのクロックで動作し、データ転送は

-

800MB/s~1.06GB/sに達します。

-

メモリカードのスロットは64本のデータ信号線をもつDIMM(Dual Inline Memory Module)

-

という形式で、ピン数は168です。

-

-

ノースブリッジとサウスブリッジの間は、当初33MHzのクロックのPCIバス(133MB/s)が

-

使用されていましたが、現在はより高速化されたV-Link(266MB/s)、あるいは

-

MuTIOL(Multi-Threaded I/O Link ; 533MB/s)という高速バスが用いられています。

-

-

サウスブリッジと呼ばれるチップセットには、低速ながら容量の大きな記録デバイスと

-

データ交換を行う機能が組み込まれています。

-

例えば、ハードディスクやCD-ROM、DVD等は、IDEという形式のバスで接続されます。

-

これらの仕様も高速化が進み、現在では UltraATA/133が実用化され、伝送速度も

-

133MB/sに達しています。

-

-

この他、サウスブリッジには、上記PCIバスや、フロッピーディスクドライバ、USB

-

(Universal Serial Bus)、RS-232Cのシリアルバス、プリンタ等を接続するパラレル

-

ポートなどを接続する機能が実装されています。

-

-

最近のOSには、マルチタスク、マルチスレッド方式が導入され、アプリケーションソフトも、

-

多量のメモリを必要としています。メインメモリの容量も増えつつありますが、ソフト側の

-

要求にはとても追いつけません。このため、ハードディスクを用いた仮想メモリ方式が

-

用いられています。

-

-

この方式は、限られたメモリ容量でも、あたかも大きなメモリ空間が存在するように、プログラム

-

を動作させる方式であり、実際には存在しないメモリ空間をアクセスするたびに、メインメモリの

-

内容をスワップファイルとして、一旦ハードディスクに保存します。

-

そして、これからアクセスする仮想メモリのデータを、該当するスワップファイルからメインメモリ

-

上に読み出して使用します。当然のことながら、メインメモリとハードディスクのデータ交換には、

-

メモリアクセスの数十~数百倍と、桁外れの時間を要するため、その間CPUは待ち続けることに

-

なります。

-

-

マザーボードやチップセットは、このようなデータ転送による性能低下を最小限に抑えるよう、

-

キャッシュメモリ等を活用する手法が導入されています。

-

-

-

-

マザーボードは基本的にハードウェアですが、BIOSと呼ばれるソフトウェアがEEPROMの形で

-

組み込まれています。電源を投入すると、CPUはこのBIOSのデータを読み込み、マザーボード

-

のデバイスをチェックし、2つのブリッジLSIをはじめ、ディスプレイカードやキーボード、マウス、

-

ハードディスク、CD-ROMのように接続しているハードウェアを動作可能な状態に初期化します。

-

その後、ブート(起動)するデバイス(通常はハードディスク)からメモリ上にOSのカーネルを

-

読み込んで実行します。

-

-

BIOSはハードウェアを直接制御しますが、単純な処理しかできません。このため、OSはそれ

-

ぞれのハードウェアを制御するデバイスドライバというソフトウェアを、ハードディスクから読み

-

込んで、それぞれのアプリケーションから利用できるように準備します。

-

-

各種アプリケーションからハードウェアに特定の処理をさせる場合、OSのAPI(Application

-

Programming Interface)を呼び出します。このAPIはそれぞれのハードウェア固有のデバイス

-

ドライバを読み出し、BIOS経由で制御します。

-

-

このように、ハードウェアを制御するためのソフトウェアが階層化されている理由は、拡張ボード

-

やコネクタに接続されるハードウェア(例えば、グラフィックボード)が変わっても、柔軟に対応

-

できるようにするためです。

-

-

例えば、新しいグラフィックボードを開発する場合、AGPソケットやPCIソケットのようなハード

-

ウェアの仕様と、各種OSのAPIの仕様を満たすようにソフトウェア(デバイスドライバ)を開発

-

すればよいことになります。

-

-

このように現在のパソコンは、CPUやマザーボード、ハードディスク、CD-ROM等、それぞれの

-

メーカーが分業して開発できる仕様の上になりたっています。

-

5. CPUの構成

-

-

一口にCPUといっても、8bitの1チップマイコンから、本格的なコンピュータに内蔵されている

-

プロセッサまで、多種多様です。また、半導体プロセスやコンパイラをはじめとするソフトウェア

-

技術の進歩により、次々に新しい技術が取り入れられ、その内部構造も進化しています。

-

ここでは、一般的なパソコンに使用されている代表的なCPUの構成について、その概要を

-

説明します。

-

なお、CPUを高速化するため、「スーパーパイプライン方式」や「スーパースカラ方式」等

-

高度な手法が取り入れられています。その詳細については、教科書及び「CPUの高速化

-

手法」等を参照してください。

-

-

はじめに、CPU開発の歴史について簡単に説明します。

-

CPUには、複雑な命令体系をもつCISC型と、命令体系を単純化することにより高速化を図った

-

RISC型が存在します。

-

CPUの処理内容は、次の4つに大きく分類することができます。

-

-

(1) メインメモリから命令コードを読み込むフェッチ処理

-

(2) フェッチした命令コードを解読するデコード処理

-

(3) デコードした結果をアキュムレータで実行する処理

-

(4) 実行結果をレジスタやメインメモリに書き込むライトバック処理

-

CPUが開発されて間もない頃、メモリの性能は低く、(1)のフェッチ処理に最も時間を要しました。

-

この条件では、フェッチの回数を減らすことが、処理能力の向上につながります。

-

このため、1回にフェッチできる命令コードが徐々に複雑化し、CISC(Complex Instruction Set

-

Computer)型のプロセッサが生まれました。

-

当時は、CISCという概念自体がなく、この後で述べるRISCが登場した後、この用語が使われる

-

ようになりました。

-

-

一方、半導体プロセスの進歩により、1年半に2倍という他に類を見ない速度で、1チップ内に

-

実装可能なトランジスタ数が増えてゆきました。これに伴い、命令コードをメモリから読み込む

-

速度を高速化する手法について多くの研究が行われ、キャッシュメモリの技術が実用化され

-

ました。

-

これにより、フェッチ処理の実質的な時間は大幅に短縮され、相対的に命令のデコードや実行

-

に要する時間の短縮が課題になりました。

-

そこでCISCとは逆に、命令コードを極力単純化し、パイプライン処理や並列化等の技術を導入

-

することにより高速化を図るRISC(Reduced Instruction Set Computer)型プロセッサが開発

-

されるようになりました。

-

現在の代表的なパソコンは、過去に開発したソフトウェアの遺産を継承する上位互換路線の

-

もとに発展してきました。

-

このため、歴史のあるCISC型の命令コードを、RISC型の最新技術により高速化するという

-

複雑なCPUが開発されるようになりました。

-

このCPUでは、CISC型の命令コードを、一旦RISC風のマイクロ命令コードに変換し、これら

-

をRISC型のスーパーパイプライン方式やスーパースカラ方式で高速処理しています。

-

-

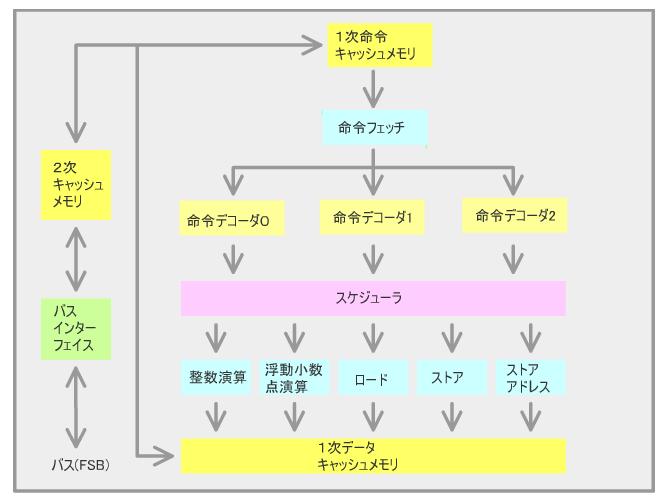

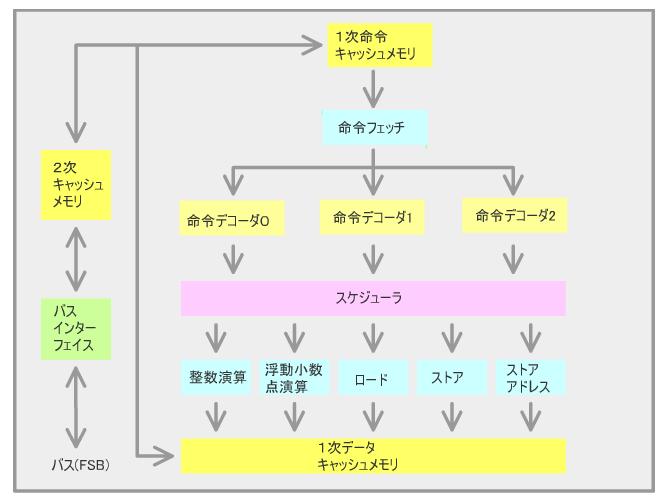

下の図を用いて、このCPUの動作を具体的に説明します。

-

-

CPUがメインメモリから命令コードを読み込む要求があると、メモリのデータをブロック単位に

-

まとめて2次キャッシュメモリ、そして1次命令キャッシュメモリに書き込みます。

-

1次命令キャッシュメモリの命令コードは、1命令ごとにフェッチ回路に取り込まれます。

-

これらは、3つの命令デコード回路で解読され、マイクロ命令コードに変換された後、

-

スケジューラに送られます。

-

以上の処理は、通常パイプライン処理されます。

-

-

マイクロ命令コードは、5つの演算ユニットで実行されます。この演算ユニットはそれぞれ特徴が

-

あり、整数演算ユニット、浮動小数点演算ユニット、メモリからの読み込み(ロード)を行うユニット、

-

メモリへの書き込み(ストア)を行うユニット、データをストアするメインメモリのアドレスを計算する

-

ユニットから構成されています。

-

メインメモリへの書き込み(ストア)は、1次データキャッシュメモリ、2次キャッシュメモリを経由して、

-

行われます。

-

なお、キャッシュメモリの動作については、稿を改めて説明します。

-

-

-

-

6. まとめ

-

-

ここでは、デスクトップ型パソコンの内部構成を中心に解説してきました。

-

大まかな機能や構造について、理解が深まったと思います。

-

-

なお、CPUのより詳細な原理、内部構成については、別途解説する予定ですが、関心のある

-

項目については、各自教科書やインターネット等で調べて下さい。

-