| SUBCKT の作成と SPICE Netlist の応用 ・ SUBCKT の登録と使用については、既に項を設けて説明してあり ます。 SUBCKT の登録と使用 ここでは、もう少し先に進んだ話をします。 |

|

| ● |

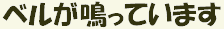

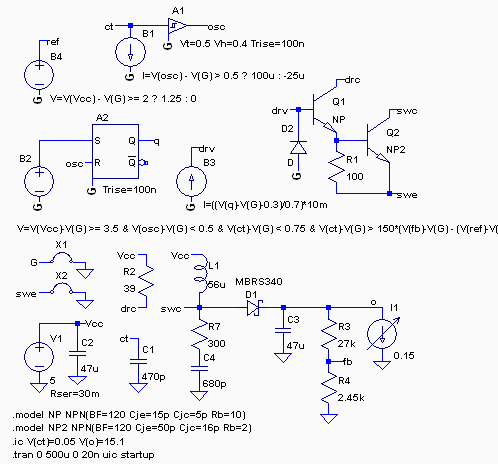

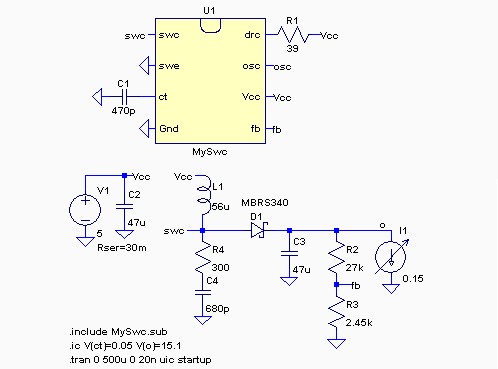

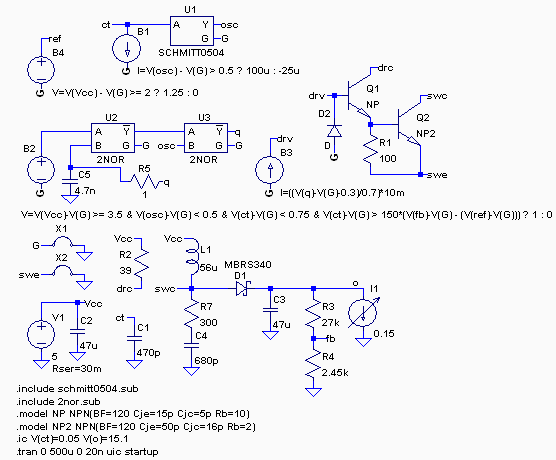

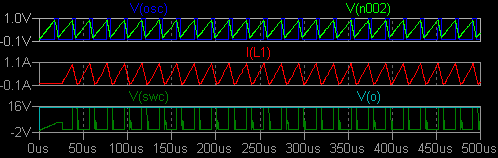

回路図から SUBCKT ファイルを簡単に作成する方法を試しました。 まずは回路を作成して動作確認をしますが、subckt 化することを意識して接続部には Label を使用 します。 下記回路の上半分を subckt にする予定です。   Draft1.asc Draft1.plt この上半分だけを切り出して新規回路にします。View → SPICE Netlist を実行すると、*.net ファイルが作成されます。これを一部編集して MySwc.sub を作ります。(赤字の部分が手動編集した部分です。) .subckt MySwc swc swe ct G fb vcc osc drc A1 ct G G G G G osc G SCHMITT Vt=0.5 Vh=0.4 Trise=100n B1 ct G I=V(osc) - V(G) > 0.5 ? 100u : -25u B2 N001 G V=V(Vcc)-V(G) >= 3.5 & V(osc)-V(G) < 0.5 & V(ct)-V(G) < 0.75 & V(ct)-V(G) > 150*(V(fb)-V(G) - (V(ref)-V(G))) ? 1 : 0 A2 N001 osc G G G G q G SRFLOP Trise=100n Q1 drc drv N002 0 NP Q2 swc N002 swe 0 NP2 R1 N002 swe 100 B3 G drv I=((V(q)-V(G)-0.3)/0.7)*10m D1 G drv D B4 ref G V=V(Vcc) - V(G) >= 2 ? 1.25 : 0 .model D D(Is=2.52n Rs=0.568 N=1.752) .model NP NPN(BF=120 Cje=15p Cjc=5p Rb=10) .model NP2 NPN(BF=120 Cje=50p Cjc=16p Rb=2) .ends シンボルファイル MySwc.asy も 作成しておきます。 このシンボルを利用したトップレベルの回路を作成しますが、このときも先の回路図の 下半分が大幅に流用できます。  Draft3.asc Draft3.plt MySwc.sub MySwc.asy 簡単なものであれば *.sub を直接作るのもいいのですが、複雑なものを一度間違えるとその原因を探すのが大変 です。 この方法なら、とても楽に subckt ファイルを作成できます。 |

| ● |

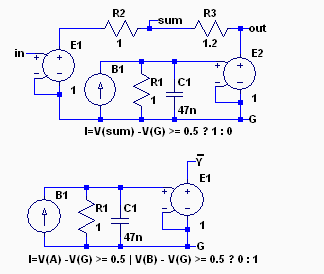

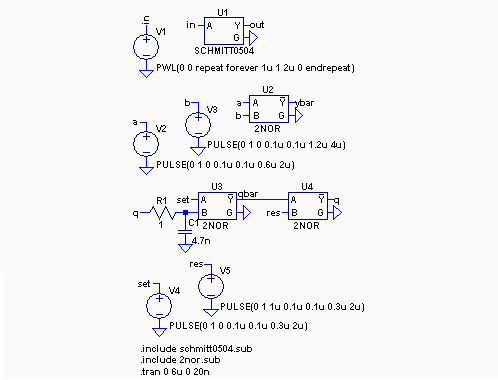

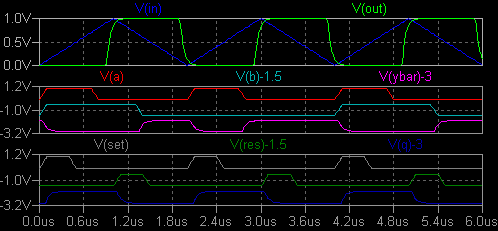

SUBCKT や回路を他の Spice にエクスポートしてみました。 Export の相手として WinSpice を使いました。 http://www.winspice.co.uk/ が御本家の HP です。 説明書 は http://woody.us.es/ASIGN/TCEF_1T/Prob/WSpiceman.pdf などにあります。 無理とは思いながらも、先の Draft3.asc から View → SPICE Netlist で Draft3.cir を作成しま した。(まずは Draft3.net を名称変更して Draft3.cir とします。) MySwc.sub はそのまま使い ます。 Error 等をつぶしていくと、次のことがわかりました。 WinSpice では: 電圧源の直列抵抗 Rser は使用不可。 インダクターの寄生素子 (Rser, Rpar, Cpar) は使用不可。 ダイオード .model の Iave, Vpk, type は使用不可。 .backanno は消しておくこと。 ここまでの結果。 Draft3.cir 予想していたことですが、SCHMITT 等は使用できません。 OuseTech\WinSpice\examples\SCHMITT.cir は 見つけたのですが、これはトランジスタをあからさまに使っています。 そこで A デバイスを使用しない schmittbuf と 2 入力 NOR を作成しました。 回路図で書くと:  schmitt0504.sub 2nor.sub schmitt0504.asy 2nor.asy 上記 subckt の試験をしておきます。   Draft6.asc Draft6.plt これでも不安なので、こんなのも作って確かめておきました。  ここまでは問題ありません。上図の R5, C5 がちょっと余分で心残りなのですが、このまま先に進みます。 |

| ・ |

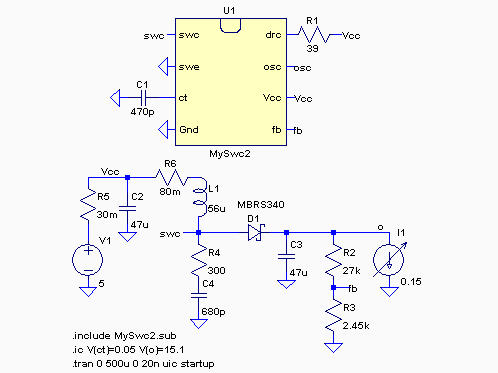

前記回路図の上半分を View → SPICE Netlist で

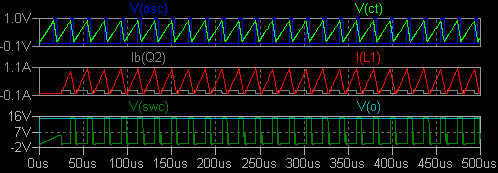

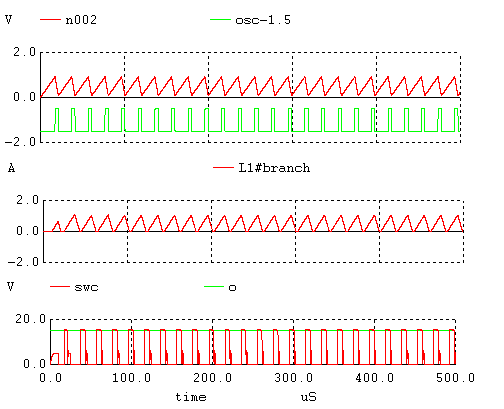

ネットリスト化し、手動編集して MySwc2.sub を作成します。 赤字の部分を手動編集しました。 .subckt MySwc2 swc swe ct G fb vcc osc drc B1 ct G I=V(osc) - V(G) > 0.5 ? 100u : -25u B2 N001 G V=V(Vcc)-V(G) >= 3.5 & V(osc)-V(G) < 0.5 & V(ct)-V(G) < 0.75 & V(ct)-V(G) > 150*(V(fb)-V(G) - (V(ref)-V(G))) ? 1 : 0 Q1 drc drv N004 0 NP Q2 swc N004 swe 0 NP2 R1 N004 swe 100 B3 G drv I=((V(q)-V(G)-0.3)/0.7)*10m D1 G drv D B4 ref G V=V(Vcc) - V(G) >= 2 ? 1.25 : 0 XU1 ct osc G SCHMITT0504 XU2 N001 N002 N003 G 2NOR XU3 N003 osc q G 2NOR C1 N002 0 4.7n R2 q N002 1 .include schmitt0504.sub .include 2nor.sub .model D D(Is=2.52n Rs=0.568 N=1.752 Cjo=.64p M=.4 Tt=5n) .model NP NPN(BF=120 Cje=15p Cjc=5p Rb=10) .model NP2 NPN(BF=120 Cje=50p Cjc=16p Rb=2) .ends 周辺回路の寄生素子を明示した回路を作って動作確認をした後、これも View → SPICE Netlist を利用して Draft7.cir とします。   Draft7.cir MySwc2.sub schmitt0504.sub 2nor.sub これで WinSpice (winspice3.exe) を実行しました。 plot n002 osc plot I(L1) plot swc o これらは .cir に含めず、手動で実行する必要がありました。 正規に登録していないという理由のせいかもしれません。  |

| もどる |

| |