| デジタル信号伝送の歪み |

|

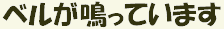

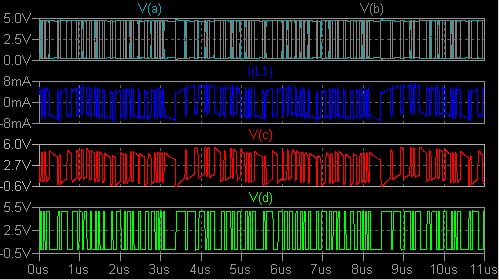

| ・ | デジタル信号も伝送中に歪んで

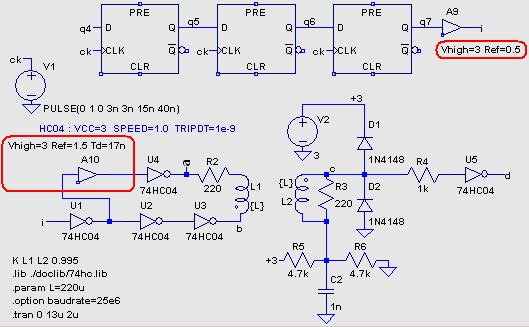

しまい、正しい情報を伝えられなくなります。 この評価

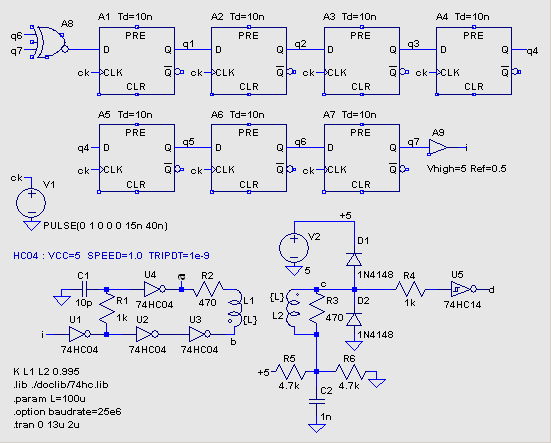

のために擬似ランダム信号発生器とドライバー、結合トランス、レシーバー

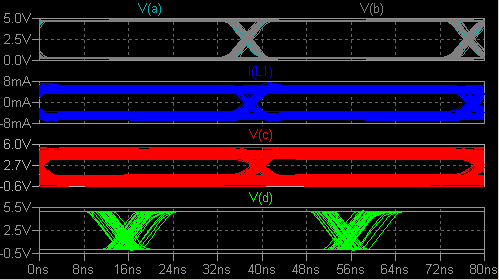

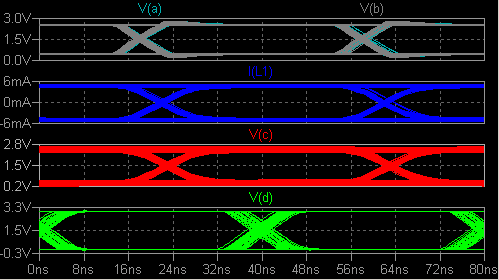

を回路化しました。 伝送ビットレートは 25Mbps です。 dtld.asc 74hc.lib 74hc04.asy 74hc14.asy 74HC シリーズのライブラリーとシンボルファイル は http://groups.yahoo.com/group/LTspice/files/Lib/ から入手しました。 V1 クロックから q7 出力までが擬似ランダム信号発生器です。 これ は PN (pseudo noise) 発生器とも呼ばれます。「擬似」ですから実はくり返しの ある信号で、クロックが 25MHz のときの周期は約 5μs です。  ドライバー、レシーバーを通った後の信号波形は次のようになります。  いくら これを眺めていても性能の評価はできないでしょう。 ディレクティブ に「.option baudrate=25e6」と書いておきました。 この 指定があると「アイダイアグラム」を表示させることができ ます。 アイダイアグラムは、元データを 1 / baudrate の区間に 区切って、その波形を重ね書きします。 まず過渡応答グラフのウィンドウをクリック し、Plot Setting → Eye Diagram の Enable をクリックします。  かなり限度に近い状態です。 もっと高速の部品を使って電力消費にも眼をつぶれば、簡単に高性能化できるの ですが。 なお、伝送する信号の連続する '0' または '1' の個数に制限を付けると、 伝送路に対する品質要求は楽になります。 |

| ・ |

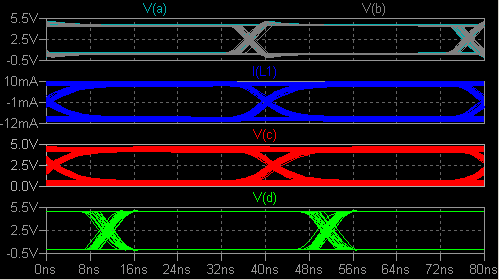

少しは改良できないものかと試してみまし

た。 R2, R3 を 220Ω、L1, L2 を 220μH、U6 を 74HC04 に変えるとだいぶ改善されます。 どの素子パラメーターの変化がどのような結果を生み出すか、シミュ レーションとはいえ予測・確認できるのはたいへん心強いものです。 |

| ・ |

この回路を電源電圧 3V で動作させようとする

と、興味深いことに R1, C1 の遅延回路が性能悪化の原因になります。 そこで

遅延素子に変えました。 A9 の Vhigh は 3V に変更します。 アイパターンはけっこうまともです。 1N4148 のスレッショルド電圧が気になった のですが、元のままが最良でした。 U5 74HC04 の動作がやや不審です。 という ことは、ドライバーの 74HC04 もあぶないということですね。  25Mbps の伝送回路に 3V 動作の 74HC04 を使うというのが、そもそも冒険的でした。 |

| もどる |

| |