僗僫僢僠儍乕偺SCC 偦偺2

丂BABAX偝傫偺僒僀僩偵SCC搵嵹婎斅偺夞楬恾偑傾僢僾偝傟偨嵺偵丄壓婰僐儊儞僩偑偁傝傑偟偨丅

SCC搵嵹僇乕僩儕僢僕偺夞楬恾岞奐

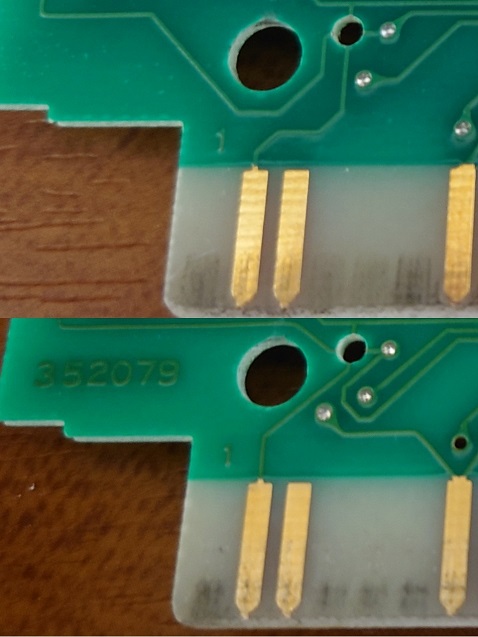

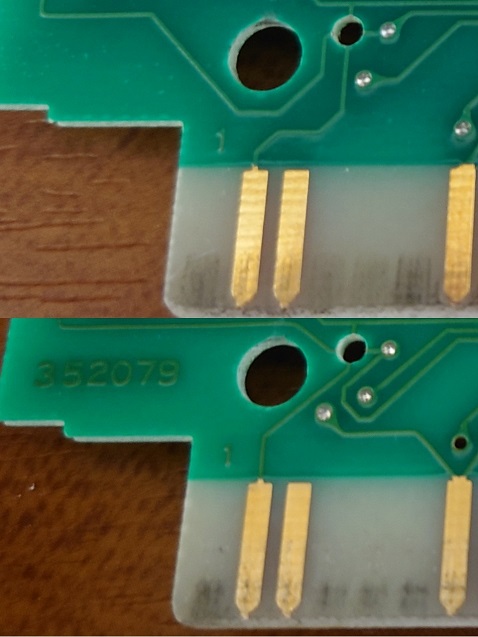

丂乽SD僗僫僢僠儍乕偺婎斅偼351446偲摨堦偲巚偭偰偄偨偺偱偡偑丄夋憸専嶕偡傞偲352079偲偄偆婎斅傕偁傞傛偆偱偡丅乿

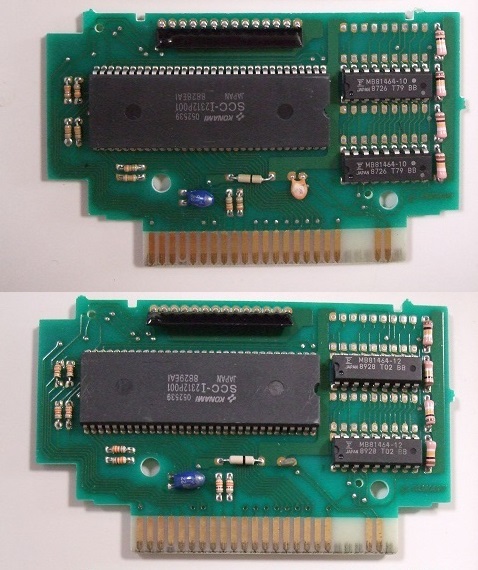

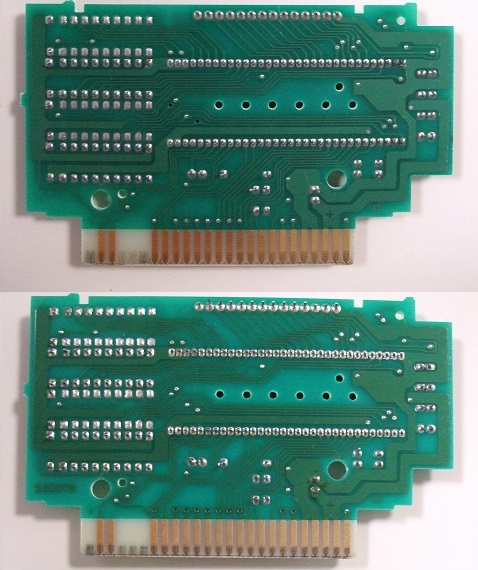

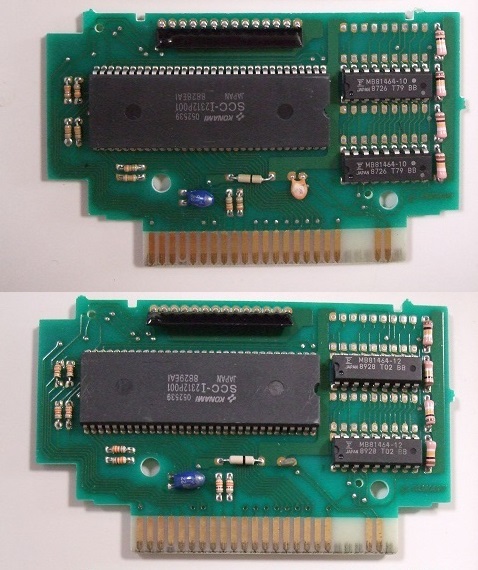

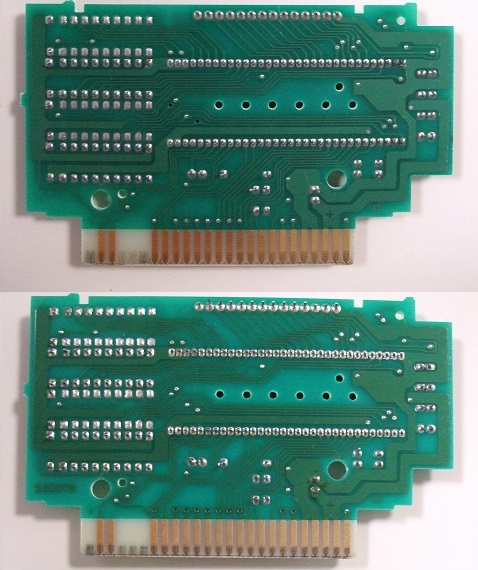

丂庤尦偵僗僫僢僠儍乕偲SD僗僫僢僠儍乕偺SCC僇乕僩儕僢僕偑2屄偢偮偁偭偨偺偱妋擣偟偨偲偙傠丄僗僫僢僠儍乕偺SCC僇乕僩儕僢僕偼椉曽偲傕351446丄SD僗僫僢僠儍乕偺僇乕僩儕僢僕偼椉曽偲傕352079偱偟偨丅摨堦婎斅偱RAM偑嵹偭偰偄傞偲偙傠偑堘偆偩偗丒丒丒偲巚偄崬傫偱偄傑偟偨偑丄幚偼堦尒丄摨偠偲偙傠偵嵹偭偰偄傞傛偆偵尒偊偨傝偟傑偡丅忋偑僗僫僢僠儍乕偺婎斅丄壓偑SD僗僫僢僠儍乕偺婎斅偱偡丅

丂

丂

丂壗屘偲巚偄偮偮丒丒丒堎側傞応強傪扵偟偰傒傞偲丄僗儘僢僩偺1僺儞晅嬤偺僷僞乕儞偑旝柇偵堎側偭偰偄傑偟偨丅

丂

曄峏揰侾丗僗僫僢僠儍乕梡SCC婎斅(351446)偱偼DRAM偺4僺儞(/WE)偑SCC-I偺14僺儞(/MWE)偵偮側偑偭偰偄傑偡偑丄SD僗僫僢僠儍乕梡SCC婎斅(352079)偱偼僗儘僢僩偺13僺儞(/WR)偵偮側偑偭偰偄傑偡丅

曄峏揰俀丗SD僗僫僢僠儍乕梡SCC婎斅偱偼僗儘僢僩偺1僺儞晅嬤偵3屄偺僗儖乕儂乕儖偑偁傝丄偦偺偆偪1屄偼僗儘僢僩偺13僺儞(/WR)偲偮側偑偭偰偄傑偡丅巆傝偺擇偮偺僗儖乕儂乕儖偼SCC-I偺59僺儞(/MCAS0)偲58僺儞(/MCAS1)偵偮側偑偭偰偍傝丄/MCAS0偑Bank #00乣07h梡偺DRAM丄/MCAS1偑Bank #08乣0Fh梡偺DRAM偵偮側偑偭偰偄傑偡丅幨恀傪尒傞偲暘偐傞偲偍傝丄僗儖乕儂乕儖偺埵抲偼摨偠偱偡偑攝慄偑擖傟懼傢偭偰偄傑偡丅偦偺偨傔丄僗僫僢僠儍乕梡偲SD僗僫僢僠儍乕梡偱偼榑棟揑偵偼DRAM偑擖傟懼傢偭偰偄傑偡偑丄DRAM傪嵹偣傞埵抲偲偟偰偼摨偠偵傒偊偰偄傑偡丅

丂僗僫僢僠儍乕梡SCC僇乕僩儕僢僕偲SD僗僫僢僠儍乕梡SCC僇乕僩儕僢僕偼摨偠偵尒偊傞偗偳偍屳偄巊偊側偄亖屳姺惈偑柍偄丄儊儌儕傪捛壛偟偰傕柍懯偲巚傢偣偨偐偭偨偺偐側偲偪傚偭偲姩偖偭偰偟傑偄傑偟偨偑丄惢憿岺掱偱娫堘偊側偄傛偆偵DRAM傪嵹偣傞埵抲傪崌傢偣偨偩偗偩偲巚偄傑偡丅

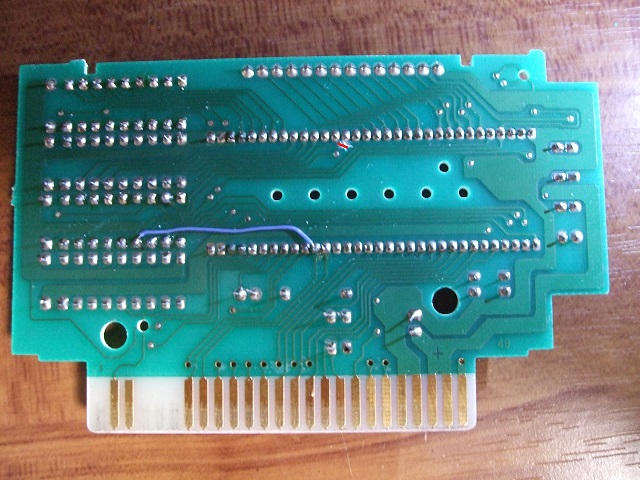

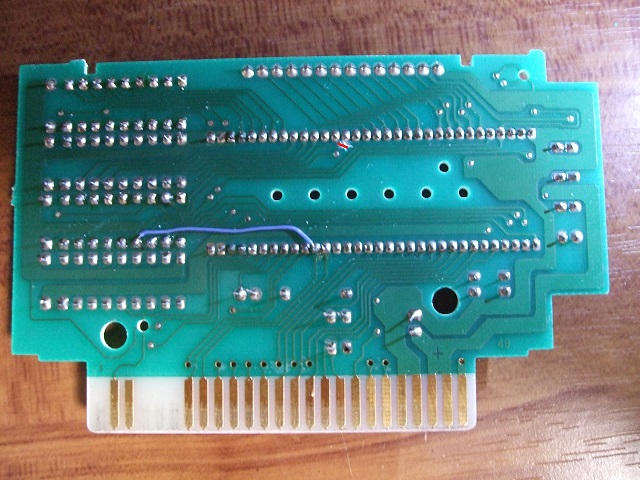

丂DRAM偺4僺儞(/WE)偺曄峏棟桼偼撲偱偡偑丄MSX Resource Center(MRC)偵壓偺幨恀偑嵹偭偰偄傑偟偨丅

丂Konami Sound Cartridge - MSX Wiki傛傝

丂

丂僆儗儞僕偺僕儍儞僷偑偮偄偰偍傝丄DRAM偺4僺儞(/WE)偲SCC-I偺54僺儞(/WR, 僗儘僢僩偺13僺儞偲偮側偑偭偰偄傞)傪偮側偄偱偄傑偡偺偱丄SD僗僫僢僠儍乕梡SCC婎斅憡摉偵曄峏偝傟偰偄傞傛偆偱丄壓婰僐儊儞僩偑彂偐傟偰偄傑偟偨丅

乽It seems that there are two versions of the PCB: an older version with a wire on the back and a newer version PCB without it. Probably because the SCC+ could not address 128kB with the older PCB.乿

丂傛偆偡傞偵128kB偺DRAM傪娗棟偱偒側偄偨傔偵捛壛偝傟偨偺偱偼側偄偐丄偲丅棟桼傪悇應偟偰偄傞偲尵偆偙偲偼丄堄恾偟偰捛壛偟偨栿偱偼柍偔丄尦偐傜偙偺僕儍儞僷偑懚嵼偟偰偄偨壜擻惈偑崅偄偲偄偆偙偲偱偡丅巹偺僗僫僢僠儍乕梡SCC僇乕僩儕僢僕偺婎斅偵偼僕儍儞僷偼偁傝傑偣傫偱偟偨偑丄偁傞帪婜偐傜捛壛偝傟偨偺偐傕抦傟傑偣傫丅棟桼偼偝偰偍偒丄杮摉偵128kB偺DRAM傪娗棟偱偒側偄偺偱偁傟偽丄僕儍儞僷柍偟偺忬懺偱偼DRAM傪捛壛偟偰傕SD僗僫僢僠儍乕偑摦偐側偄偺偱偼丄偲巚偄専徹偟偰傒傑偟偨丅

丒FS-A1ST亄僗僫僢僠儍乕梡SCC婎斅(DRAM枹憹愝)亄SD僗僫僢僠儍乕丗婲摦偣偢

丒FS-A1ST亄僗僫僢僠儍乕梡SCC婎斅(DRAM憹愝嵪)亄SD僗僫僢僠儍乕丗婲摦偡傞

丂DRAM憹愝偵傛偭偰SD僗僫僢僠儍乕偑婲摦偡傞傛偆偵側偭偨偺偱丄堦墳娗棟偱偒偰偄傞傛偆偱偡丅擮偺偨傔丄尦偐傜偁傞DRAM(Bank #00-07h)偲憹愝偟偨DRAM(Bank #08-0Fh)傪暘偗偰娗棟偱偒偰偄傞偺偐丄SHEM傪巊梡偟偰偦傟偧傟偺Bank偵懳偟偰彂偒崬傒傪偟偰傒傑偟偨偑丄偒偪傫偲暿乆偺抣傪曐帩偟偰偍傝丄娗棟偼栤戣側偄傛偆偱偡丅

丂偙偙偱偆偵僗僉乕條偑僣僀乕僩偝傟偰偄偨僗僫僢僠儍乕婲摦帪偺栤戣傪傆偲巚偄弌偟傑偟偨丅1Chip MSX偱偼僗僫僢僠儍乕偑婲摦偟側偄丄偲偄偆晄嬶崌偑偁傞傛偆偱偡丅僗僫僢僠儍乕偔傜偄桳柤側僜僼僩偼1Chip MSX奐敪帪偵専徹偟偰偄傞婥傕偟傑偟偨偑丄傑偢偼1Chip MSX偱帋偟偰傒傞偲丒丒丒妋偐偵僗僫僢僠儍乕梡SCC僇乕僩儕僢僕偑擣幆偝傟傑偣傫偱偟偨丅僗僫僢僠儍乕偼婲摦偣偢丄SD僗僫僢僠儍乕偼乽僒僂儞僪僇乕僩儕僢僕傪偝偟偰偔偩偝偄乿偲偄偆儊僢僙乕僕偱巭傑傝傑偟偨丅

丂娭學偁傞偺偐柍偄偺偐丄偲傝偁偊偢僗僫僢僠儍乕梡SCC婎斅(DRAM憹愝嵪)傪僇僢僩仌僕儍儞僷傪偟偰SD僗僫僢僠儍乕梡SCC婎斅憡摉偵夵憿偟偰傒傞偲丒丒丒栤戣側偔僗僫僢僠儍乕偲SD僗僫僢僠儍乕偑摦偔傛偆偵側傝傑偟偨丅1Chip MSX奐敪帪偵専徹偵梡偄偨SCC僇乕僩儕僢僕師戞偱偼晄嬶崌偑尒偮偐傜側偐偭偨壜擻惈偑偁傝偦偆偱偡丅

丂

丂愒慄偺偲偙傠偼SCC-I偺14僺儞(/MWE)偑DRAM偺4僺儞(/WE)偲偮側偑偭偰偄傞偺傪僇僢僩丄悈怓偺僕儍儞僷慄偱SCC-I偺54僺儞(/WR丄僗儘僢僩偺13僺儞偲偮側偑偭偰偄傞)偲DRAM偺4僺儞(/WE)傪偮側偘偰偄傑偡丅

丂偲丄偄偆偙偲偱棟桼偼傛偔暘偐傝傑偣傫偑丄尦乆偺婎斅偱偼屳姺惈丄嫲傜偔僞僀儈儞僌偵偐傜傓栤戣偑偁傝丄曄峏偝傟偨傕偺偲巚傢傟傑偡丅堦墳丄Panasonic偺MSX2+偺6MHz儌乕僪偑娭學偁傞偺偐妋擣偟偰傒傑偟偨偑丄曄峏慜偱傕曄峏屻偱傕僗僫僢僠儍乕偼婲摦偟傑偣傫偱偟偨偺偱丄偦傟偑尨場偱偼柍偄傛偆偱偡丅

丂捛壛偱僆僔儘僗僐乕僾傪巊偭偰攇宍傪偲偭偰傒傑偟偨丅2ch偟偐側偄偺偱偪傚偭偲尒偵偔偄偱偡偑丒丒丒

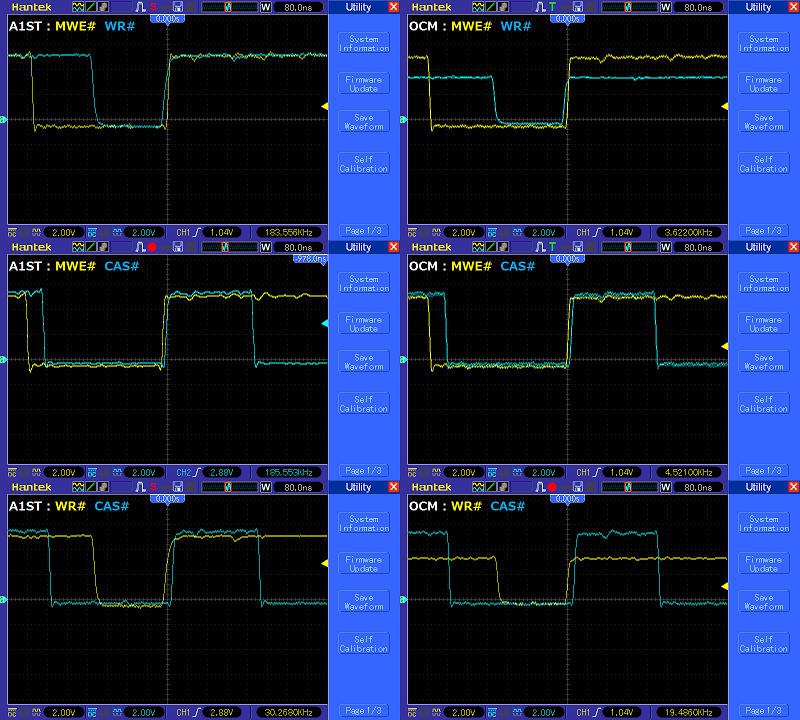

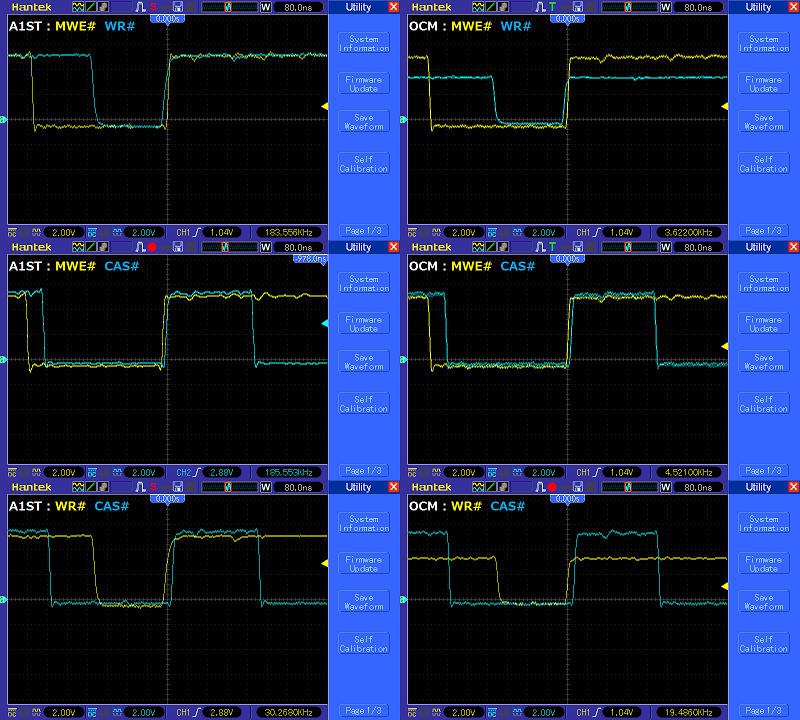

丂嵍偑FS-A1ST丄塃偑1Chip MSX偱偺攇宍偱偡丅忋偐傜乽SCC-I偺14僺儞(/MWE)偲僗儘僢僩偺13僺儞(/WR)乿丄乽SCC-I偺14僺儞(/MWE)偲DRAM偺/CAS乿丄乽僗儘僢僩偺13僺儞(/WR)偲DRAM偺16僺儞(/CAS)乿偱偡丅1Chip MSX偺弌椡偑3.3V偺偨傔丄/WR偺崅偝偑堎側傞埲奜偵偮偄偰偼丄僞僀儈儞僌偵嵎偼側偔丄偙傟偩偗偱偼尨場偑暘偐傝傑偣傫丅

丂

丂僗儘僢僩偐傜偺/WR偑Low偵側傞傛傝傕憗偔SCC-I偺/MWE偑Low偵側偭偰偄傞偲偙傠偑堦偮偺億僀儞僩偱偡丅DRAM傊偺彂偒崬傒偑峴傢傟傞偺偼丄DRAM偺/CAS偲/WE乮偙偙偵SCC-I偺/MWE傑偨偼僗儘僢僩偐傜偺/WR偑偮側偑傞乯偺椉曽偑Low偵側偭偰偄傞偲偒偱偡丅Low偵側傞弴斣偼/MWE, /CAS, /WR側偺偱丄DRAM偺/WE偵SCCI-偺/MWE偑偮側偑偭偰偄傞偲偒乮枹廋惓偺僗僫僢僠儍乕梡SCC婎斅乯偼/CAS偑Low偵側偭偨屻偵僨乕僞偑彂偒崬傑傟傑偡丅DRAM偺/WE偵僗儘僢僩偺/WR偑偮側偑偭偰偄傞偲偒乮廋惓偝傟偨僗僫僢僠儍乕梡SCC婎斅傑偨偼SD僗僫僢僠儍乕梡SCC婎斅乯偼/WR偑Low偵側偭偨屻偵僨乕僞偑彂偒崬傑傟傑偡丅慜幰偺僞僀儈儞僌偱偺彂偒崬傒偼/OE-Controlled Write Cycle丄屻幰偺僞僀儈儞僌偱偺彂偒崬傒偼Early Write Cycle偲傛偽傟傞彂偒崬傒儌乕僪偵側傝傑偡丅

丂師偵丄僨乕僞偲偺僞僀儈儞僌傪妋擣偟偰傒傑偟偨丅

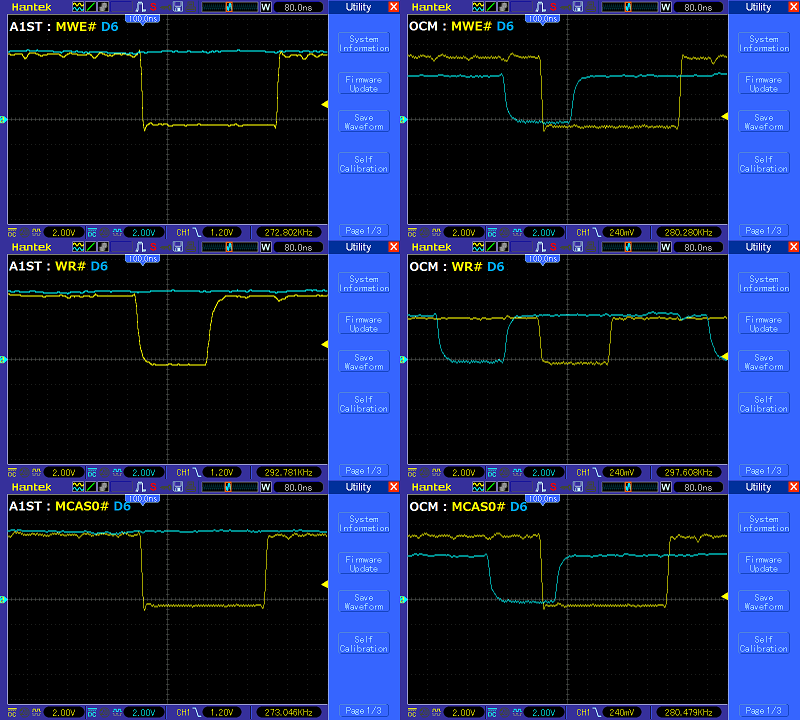

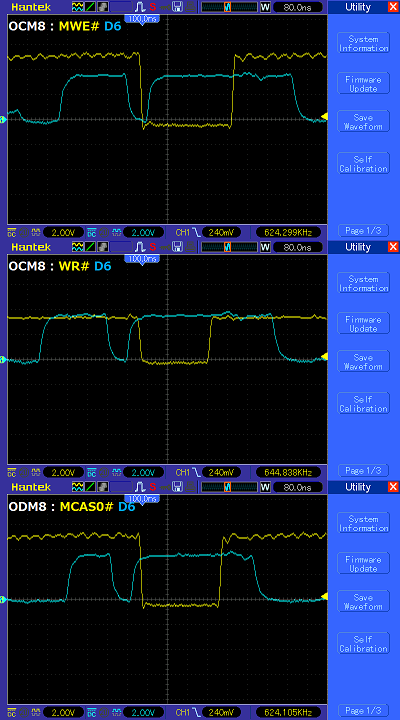

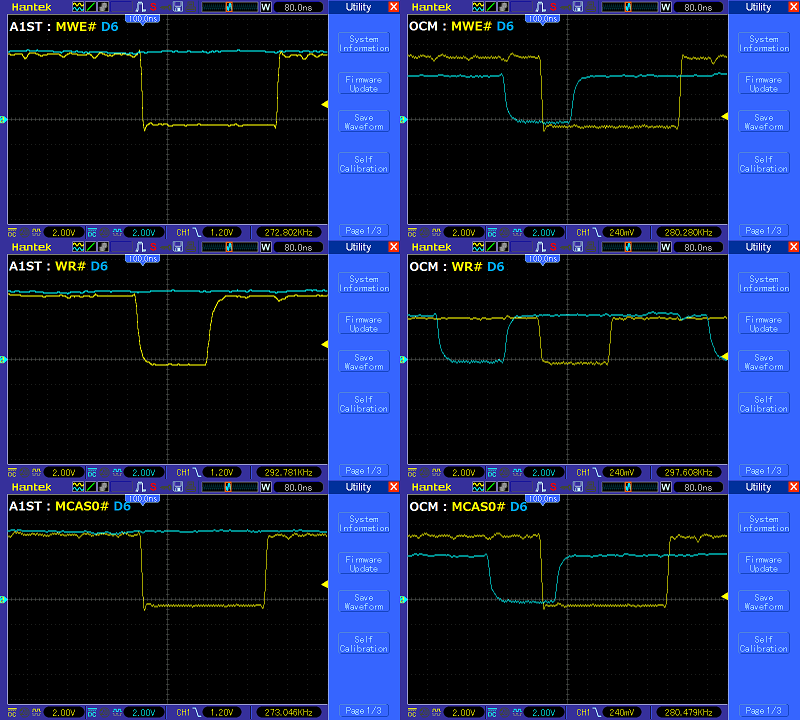

丂嵍偑FS-A1ST丄塃偑1Chip MSX偱偺攇宍偱偡丅忋偐傜乽SCC-I偺14僺儞(/MWE)偲僨乕僞(D6)乿丄乽SCC-I偺14僺儞(/MWE)偲僨乕僞(D6)乿丄乽DRAM偺16僺儞(/CAS)偲僨乕僞(D6)乿偱偡丅1Chip MSX偺弌椡偑3.3V偺偨傔丄/WR偲D6偺崅偝偑FS-A1ST偲1Chip MSX偱偼堎側偭偰偄傑偡丅

丂

丂偳偪傜傕摨偠僾儘僌儔儉偱FFh傪SCC婎斅忋偺DRAM偵彂偒崬傫偩偲偒偺傕偺偱偡偑丄柧傜偐偵悈怓偺僨乕僞偺摦偒偑堎側偭偰偄傑偡丅FS-A1ST偱偼埨掕偟偰偄傑偡偑丄1ChipMSX偱偼/MWE傗/CAS偑Low偵側偭偨屻丄/WR偑Low偵側傞慜偵僨乕僞偑曄壔偟偰偄傑偡丅偦偺偨傔丄/MWE偲/CAS傪巊偆枹廋惓偺僗僫僢僠儍乕梡SCC婎斅偱偼僨乕僞偑惓偟偔彂偒崬傑傟偢丄/CAS偲/WR傪巊偆廋惓偝傟偨僗僫僢僠儍乕梡SCC婎斅傑偨偼SD僗僫僢僠儍乕梡SCC婎斅偱偼僨乕僞偑惓忢偵彂偒崬傑傟傞傛偆偱偡丅

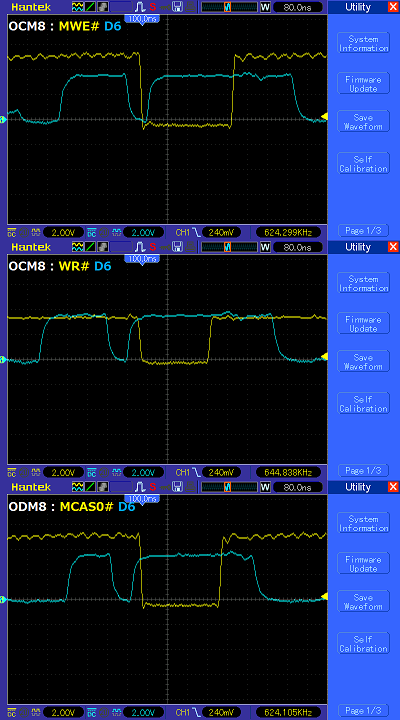

丂偪側傒偵丄1ChipMSX夵偺8MHz儌乕僪偱偼乮壒偼暿偵偟偰乯惓忢偵摦偔偲偄偆榖傕偁偭偨偺偱丄攇宍傪尒偰傒傑偟偨丅忋偺1Chip MSX偺攇宍偲帡偰偄傑偡偑丄偦傟偲偼堎側傝丄/MWE偑Low偵側偭偨屻丄/CAS傗/WR偑Low偵側傞慜偵僨乕僞偑曄壔偟偰偄傑偡丅/CAS偑Low偵側偭偨屻偺僨乕僞偼埨掕偟偰偄傞偺偱丄枹廋惓偺僗僫僢僠儍乕梡SCC婎斅偱傕僨乕僞偑惓忢偵彂偒崬傑傟傞傛偆偱偡丅

丂

丂妋擣偟偨傢偗偱偼偁傝傑偣傫偑丄嫲傜偔1Chip MSX偺僨乕僞偺攇宍帺懱偼Z80偺巇條偵斀偟偰偄傞栿偱偼側偄偲巚偄傑偡丅枹廋惓偺僗僫僢僠儍乕梡SCC婎斅偱偺僨乕僞彂偒崬傒僞僀儈儞僌偑Z80偱偺彂偒崬傒僞僀儈儞僌偐傜奜傟偰偟傑偭偰偍傝丄偦偺偨傔偵婎斅廋惓偑偝傟偨偺偩偲巚偄傑偡丅

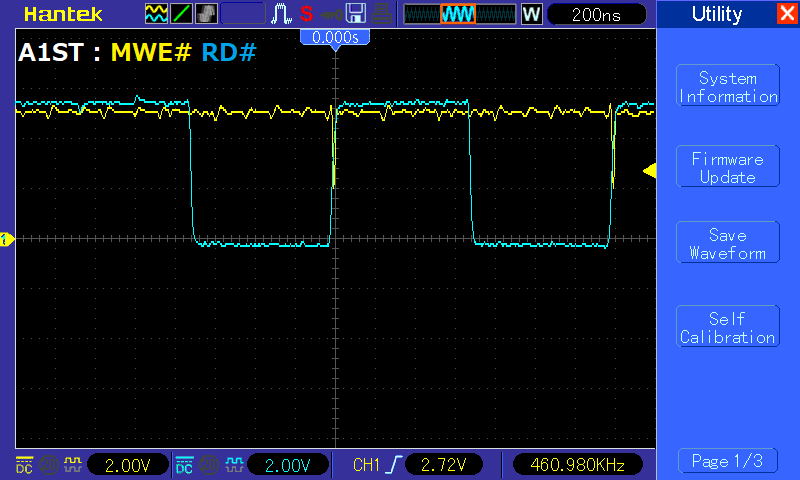

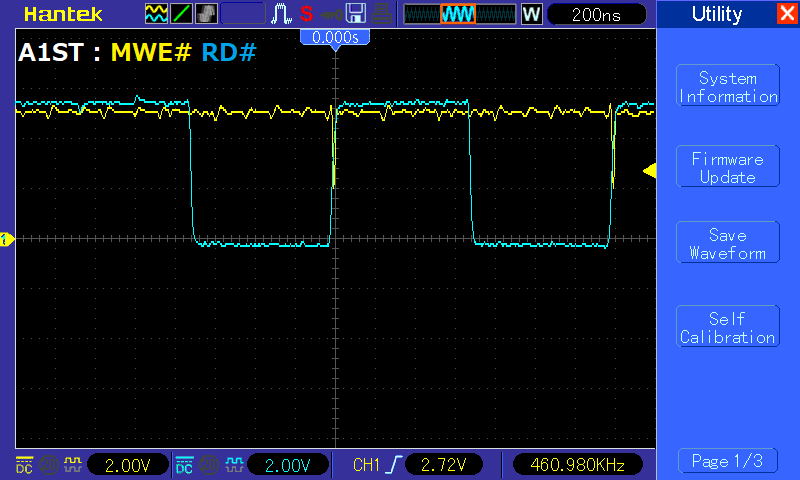

丂僗儘僢僩偐傜偺/WR傛傝愭偵SCC-I偺/MWE偑Low偵側傞偺偑偪傚偭偲晄巚媍偩偭偨偺偱偡偑丄偳偆傗傜僗儘僢僩偐傜偺/SLTSL偑Low偱/RD偑High偺帪偵丄/MWE偑Low偵側傞傛偆偱偡丅偪側傒偵丄/MWE偵寢峔側昿搙偱僌儕僢僠僲僀僘乮堦弖偩偗Low偵側傞僲僀僘乯偑敪惗偟偰偄傑偟偨丅偙偺僌儕僢僠僲僀僘帺懱偼FS-A1ST偱傕1Chip MSX偱傕弌偰偄傞偺偱丄晄嬶崌偲偼嫲傜偔娭學偁傝傑偣傫丅/MWE偲/RD偺攇宍傪妋擣偟偨偲偙傠丄/RD偑High偵側傞帪偵僌儕僢僠僲僀僘偑敪惗偟偰偄傞偙偲偑暘偐傝傑偟偨丅MSX2僥僋僯僇儖僴儞僪僽僢僋偺僞僀儈儞僌僠儍乕僩偵傛傞偲/SLTSL偲/RD偼摨帪丄傕偟偔偼/SLTSL偺曽偑抶偔Low偵側傞偺偱丄/RD偑Low偵側傞帪偼栤戣柍偝偦偆偱偡丅偟偐偟丄/RD偑High偵側傞帪偼/SLTSL偺曽偑抶偔High偵側傞偺偱丄偙偙偱僌儕僢僠僲僀僘偑偱傞傛偆偱偡丅

丂

丂偪側傒偵丄乽SX-1Mini+偱SD僗僫僢僠儍乕偑摦偐側偄乮幚婡偱偼摦偄偨乯乿偲偄偆僣僀乕僩傕尒偐偗傑偟偨丅偟偐偟丄乽僗僫僢僠儍乕梡SCC婎斅傪廋惓偟偰SD僗僫僢僠儍乕梡SCC婎斅憡摉偵偟偨偲偙傠SX-1Mini偱SD僗僫僢僠儍乕偑摦偄偨乿丄乽SX-2偱偼摦偄偰偄傞乿偲偄偆僣僀乕僩傕偁傝傑偟偨丅尨場偑摨偠偩偲偡傞側傜丄SD僗僫僢僠儍乕偺敪攧摉帪偼丄傑偩枹廋惓偺僗僫僢僠儍乕梡SCC婎斅乮偨偩偟DRAM偺埵抲偑堎側傞乯偑巊傢傟偰偄偨偺偐傕抦傟傑偣傫丅偄偢傟偵偣傛丄偁偲偼摦偐側偄幚暔偑柍偄偲暘偐傝傑偣傫偺偱丄挷嵏偼偙偙偱廔傢傝偨偄偲巚偄傑偡丅

丂僱僞傪採嫙偟偰壓偝偭偨乮彑庤偵捀偄偨偲傕偄傑偡偑^-^;乯BABAX條丄偆偵僗僉乕條丄僴儉僇僣條丄Y.Katsume條偵姶幱偄偨偟傑偡丅傑偨丄婱廳側傾僪僶僀僗傪偄偨偩偒傑偟偨HRA!偝傫丄桾擵偝傫丄OKEI偝傫偵傕姶幱偄偨偟傑偡丅

丂偍栺懇偱偡偑丄偙偺塡傪尒偰夵憿側偳傪峴偄屘忈傗偦偺懠栤戣偑敪惗偟偰傕愑擟偼晧偊傑偣傫丅奺帺偺愑擟偵偍偄偰忣曬傪峀偔廤傔偰峴偆偙偲傪偍偡偡傔偟傑偡丅