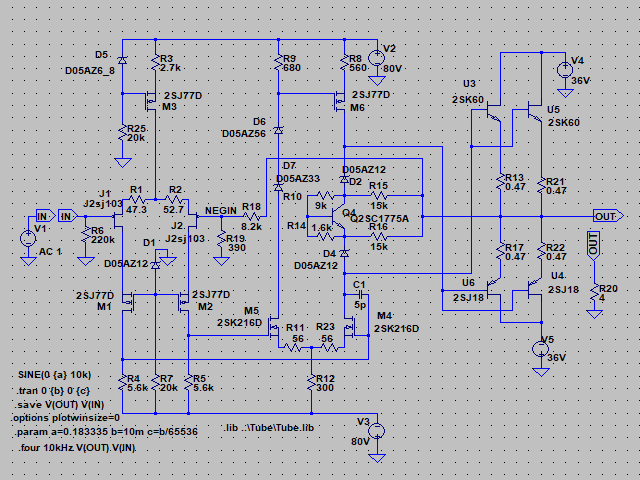

�E�Q�O�N�O�ɐ��삵���u�|�e�d�s���S�Ώ̌^�p���[�A���v�i�������B-1�H�^�C�v�j���A�Q�N�O��V-FET�i�r�h�s�j���S�Ώ̌^�p���[�A���v���p���[�h�u�b�Ƃ��čĐ������B

�E���A���̍ہA���̂a�|�P�^�C�v��V-FET�i�r�h�s�j���S�Ώ̌^�p���[�A���v���p���[�h�u�b���A�d���h���C�u�̃v�b�V���v���\�[�X�t�H���A�o�͒i�ɂ��s���S�Ώ̌^�p���[�A���v���p���[�h�u�b�Ƃ��čāX������B�@

|

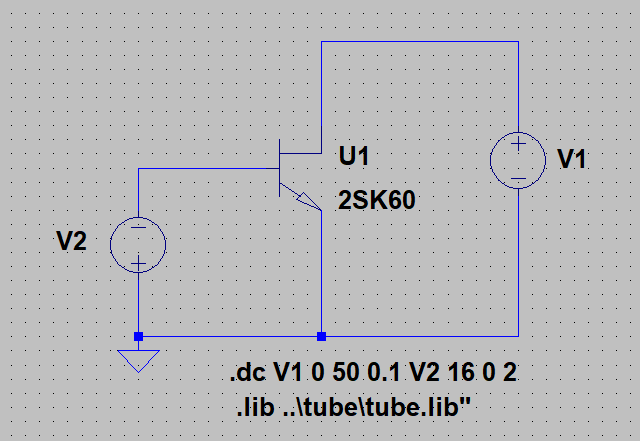

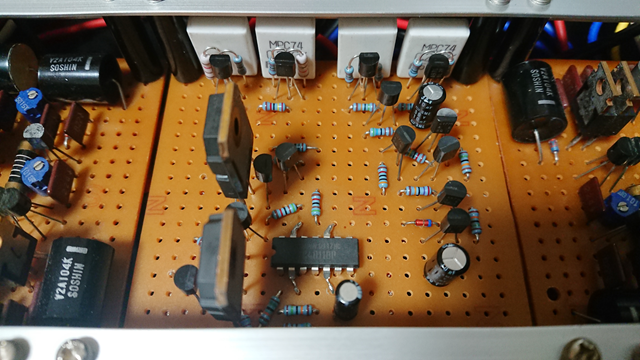

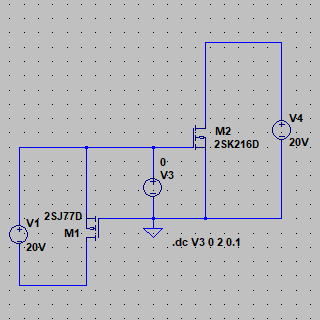

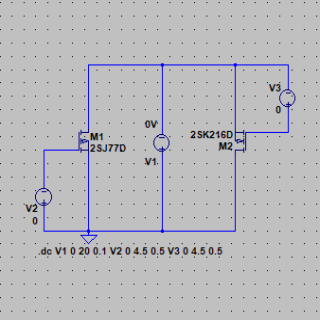

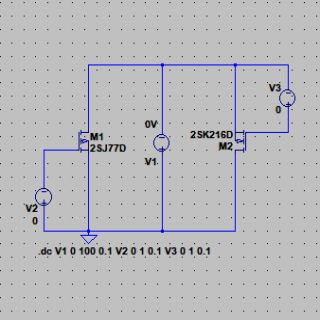

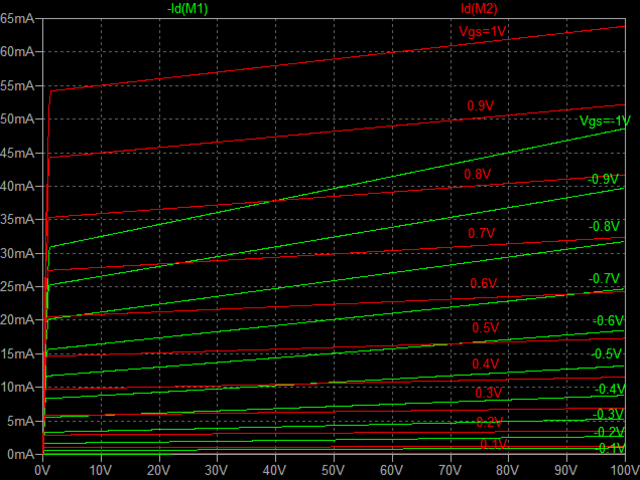

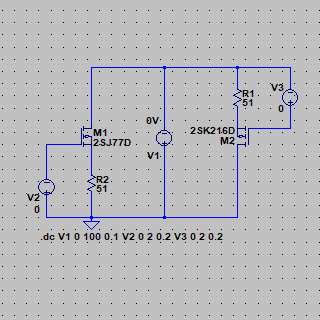

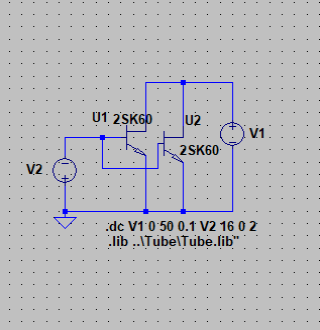

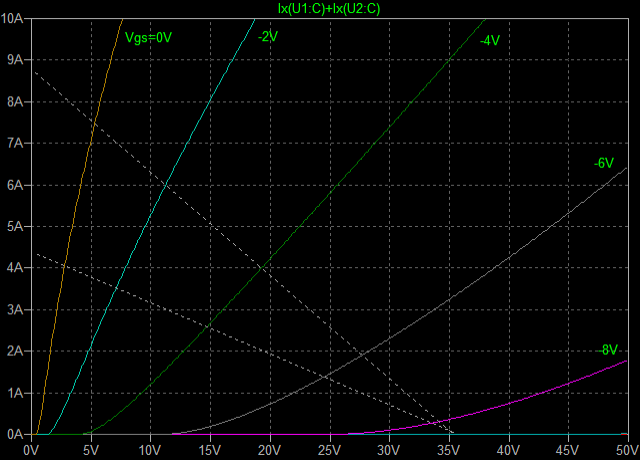

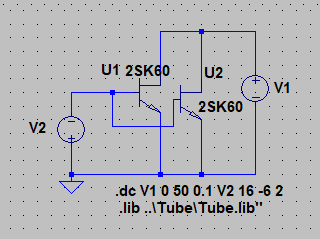

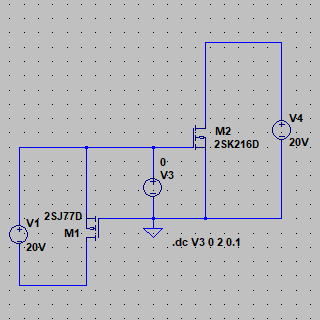

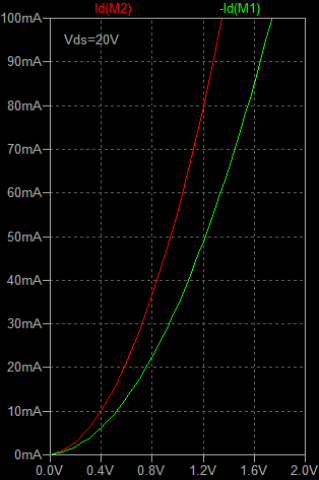

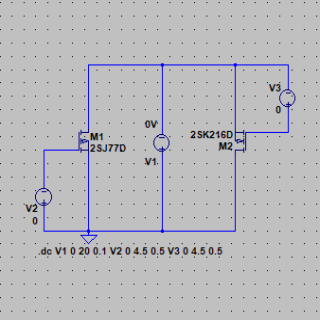

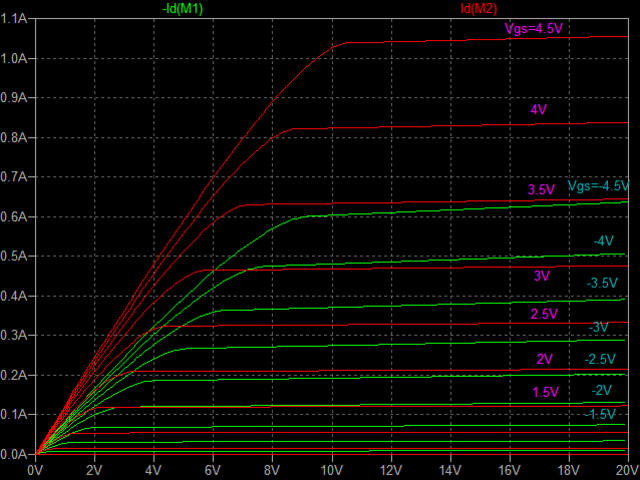

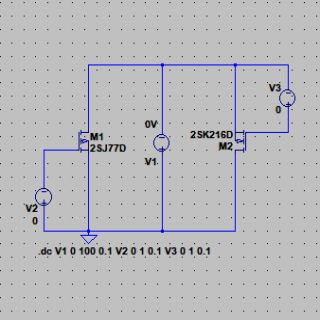

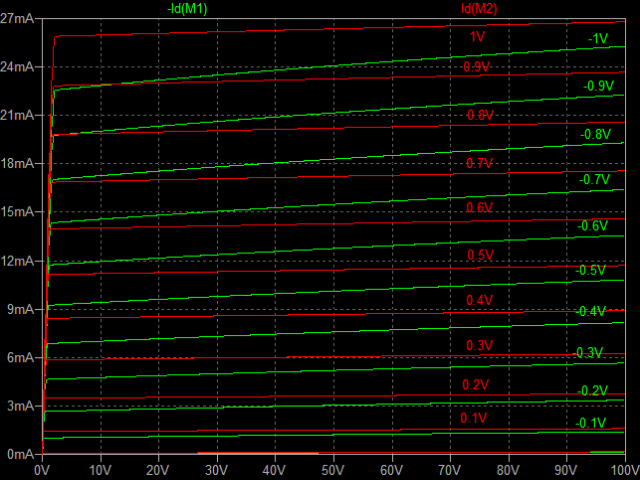

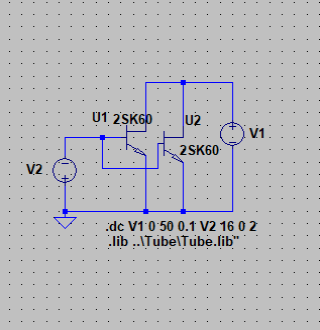

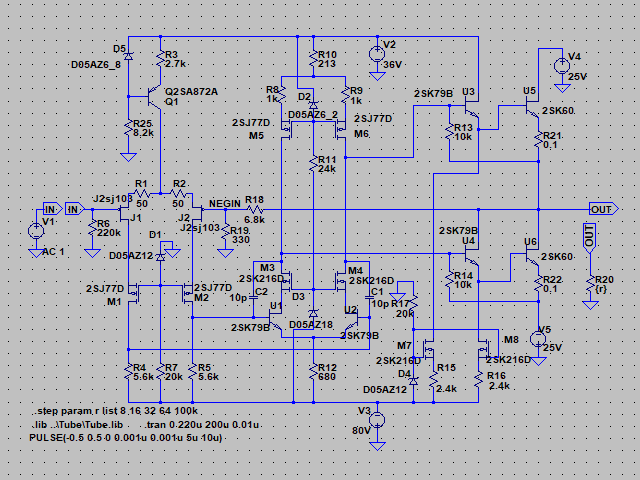

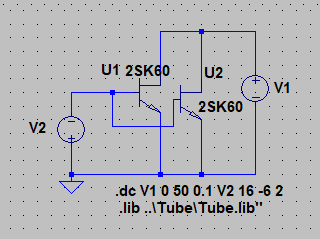

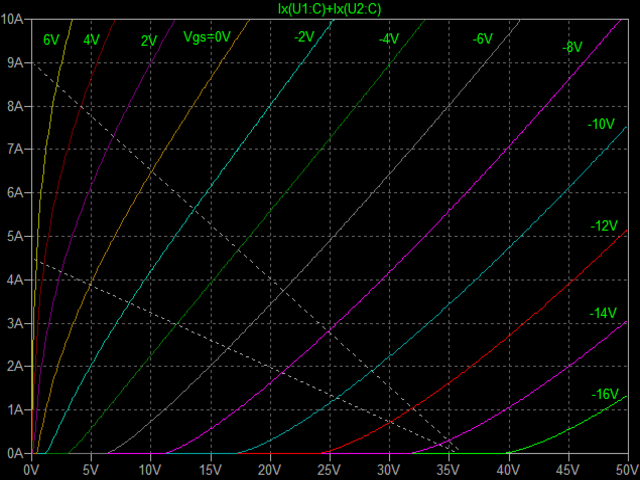

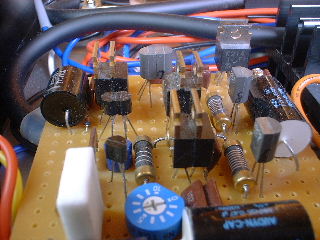

�E���̑O�ɁA�g�p����Q�r�i�V�V�ƂQ�r�j�Q�P�U�̂r�����������f�����܂�������ƘM���Ă݂��B

�E�������QSJ77D�A�QSK216D�Ƃ��A���̐Ó����B

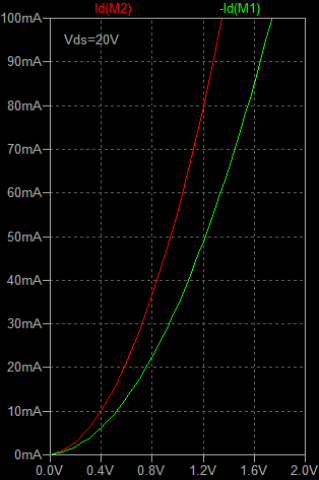

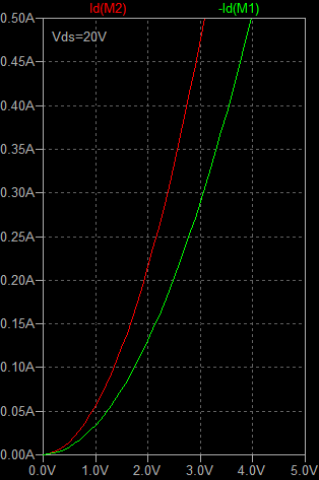

�E�u�������Q�O�u�ł̂u�����|�h�������B

�E���Q�r�i�V�VD�ŐԂ��QSK216D�B

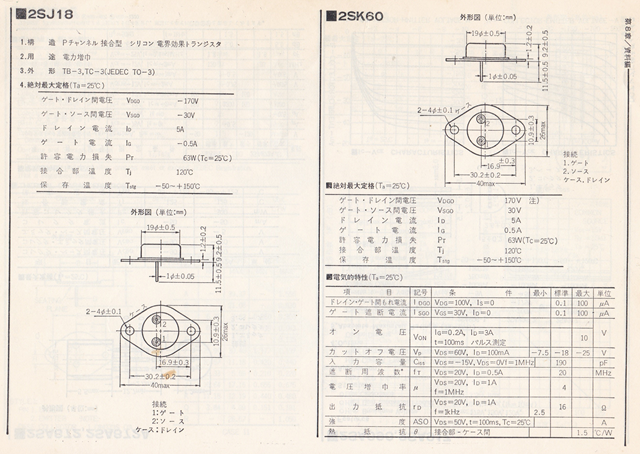

�E�f�[�^�V�[�g�Ɣ�ׂ�ƁA�܂��܂����ȁB

|

|

|

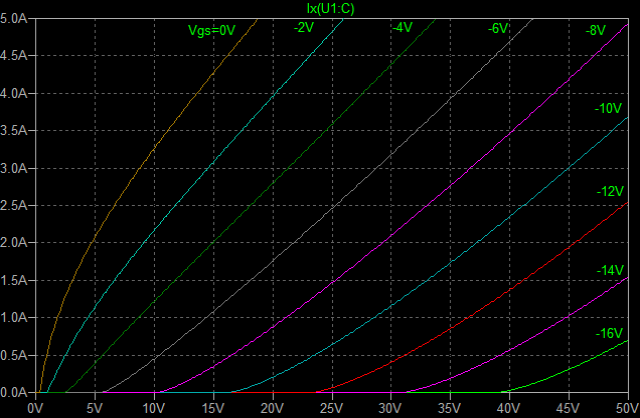

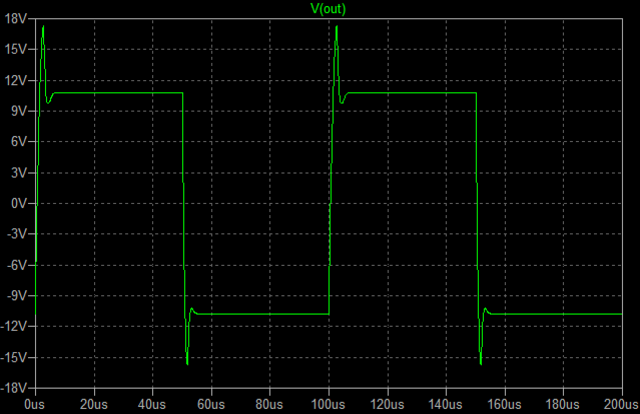

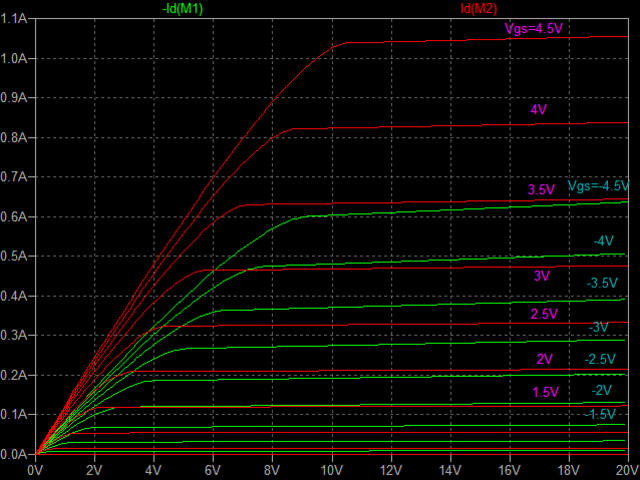

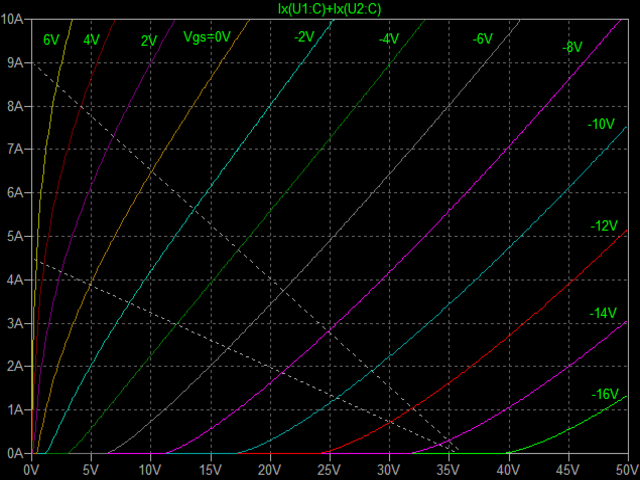

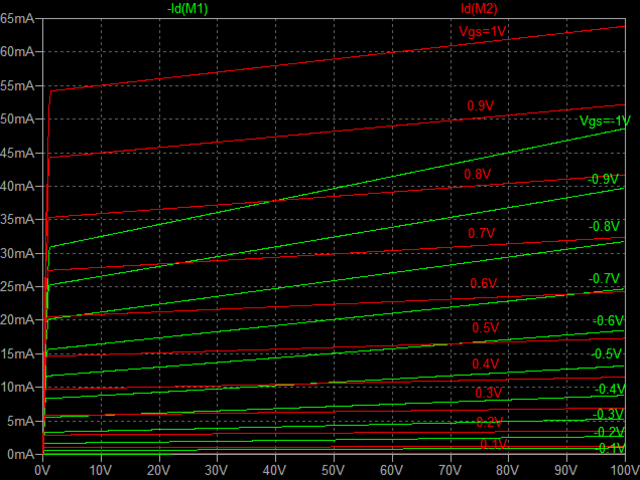

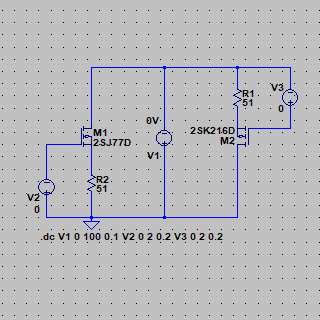

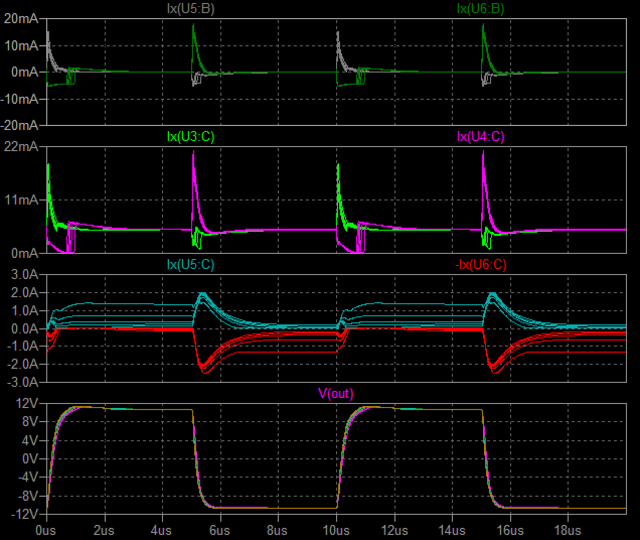

�E�u�����|�u�����[�h�������B

�E�h���̐�ő��i�͂T�O�O���`�ł��邩��A�E�̂T�O�O���`�ȏ�̃f�[�^�̓t�F�C�N�ł���B

�E�f�[�^�V�[�g�Ɣ�ׂ�ƁA���d��������₷���i�����j���A�܂��܂����ȁB

|

|

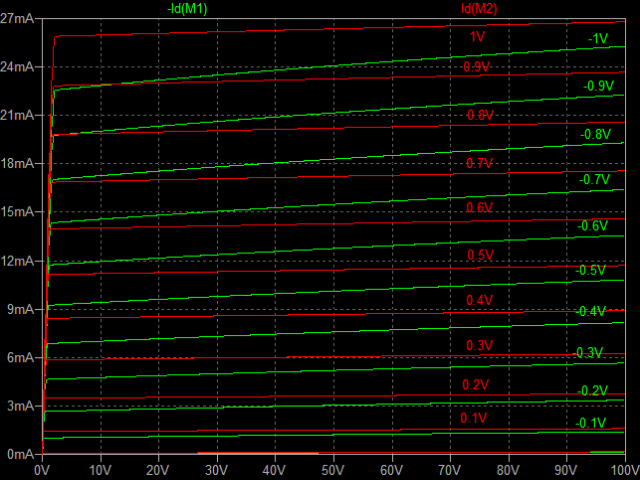

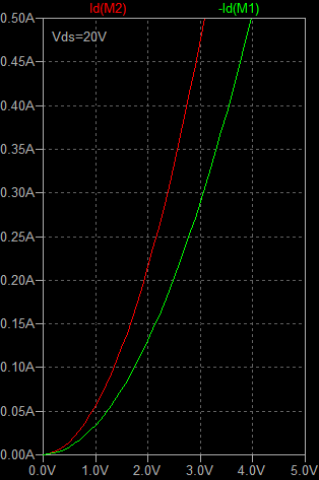

�E���ۂɎg�p�����d���̈�̂u�����|�u�����|�h�������B

�E�u�������Q�O�u�ȉ��̗̈�ɂ�����A�d���̗���肪�u���[�h�ł���ׂ��Ƃ���́A���ς�炸�Č��ł��Ă��Ȃ��B

�E�f�[�^�V�[�g�Ɣ�ׂ�ƁA���x�͂��d��������ɂ����i���Ȃ��j���A�܂��܂����ȁB

�E�f�[�^�V�[�g�ł����������A�h�����P�O���`�t�߂̏o�̓C���s�[�_���X�͂QSK216�Ő��\�������x�̂悤�B

|

|

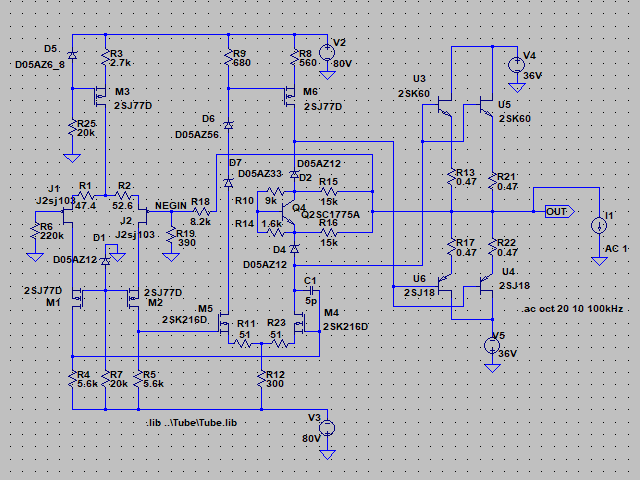

�E�\�[�X��R�T�P�������ēd���A�҂��|���Ă݂�B

�E�o�͒�R�͂P�������Ȃ����悤�B

�E���R�����A�����͏������Ȃ����B

|

|

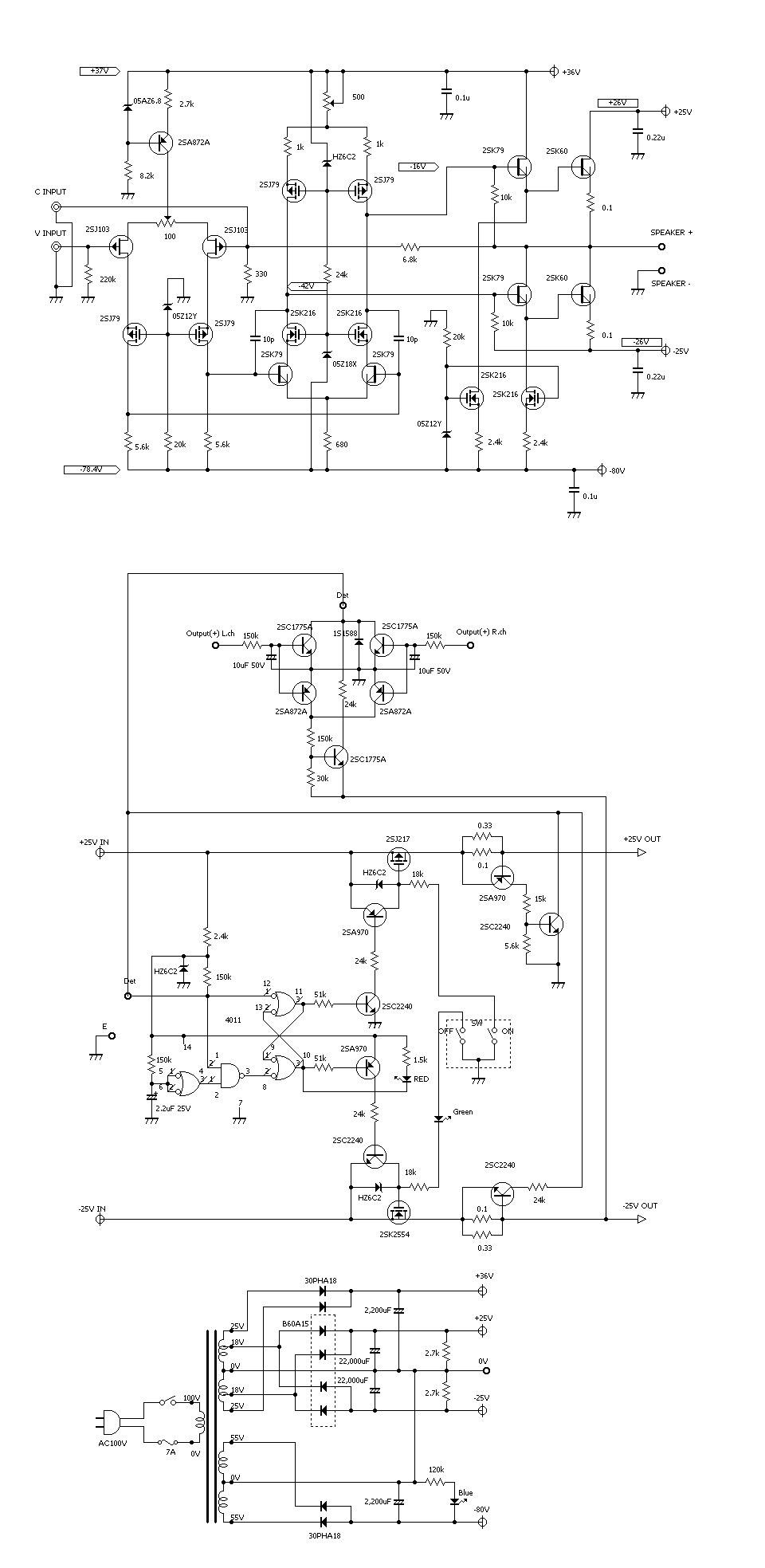

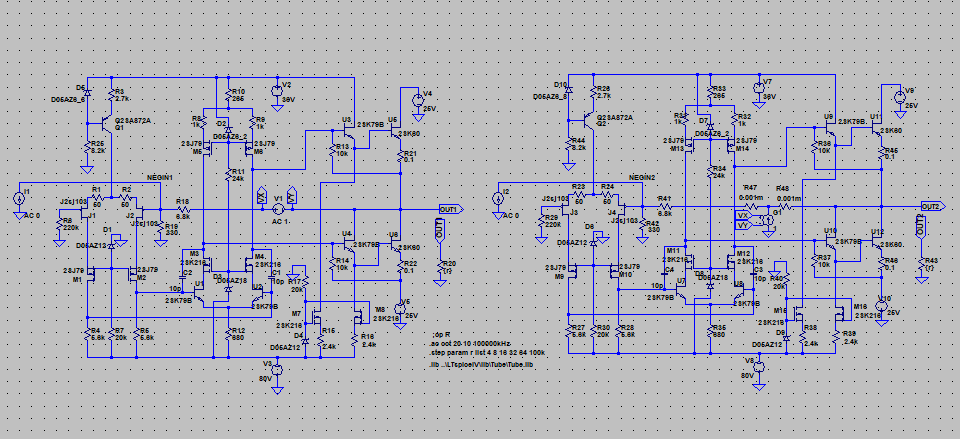

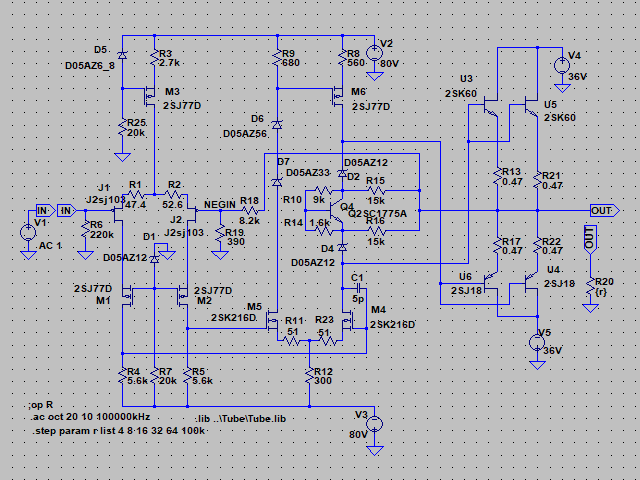

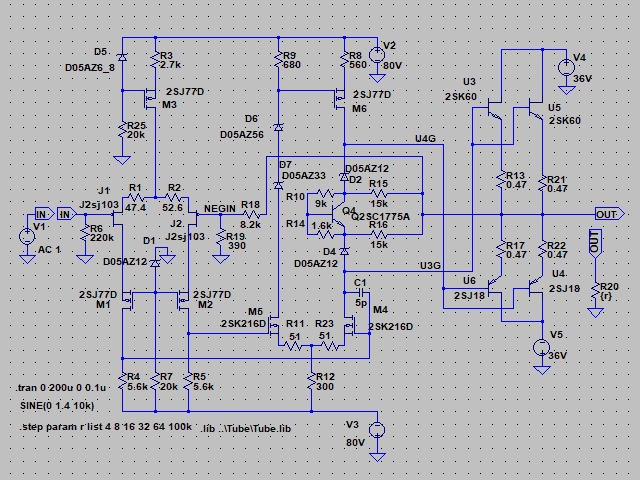

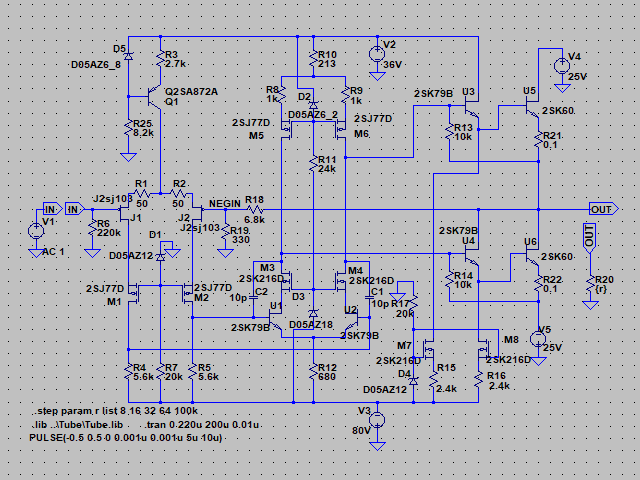

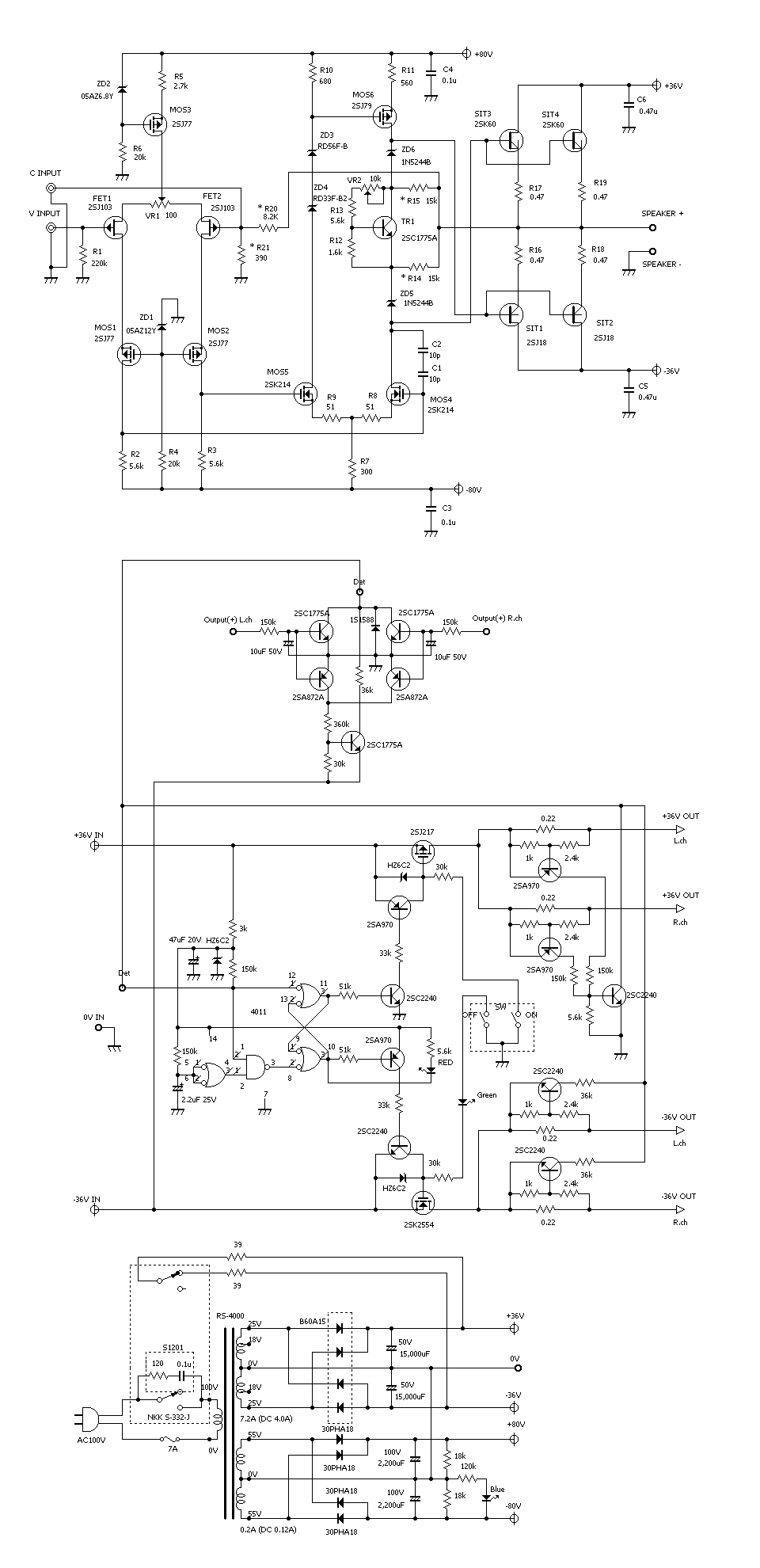

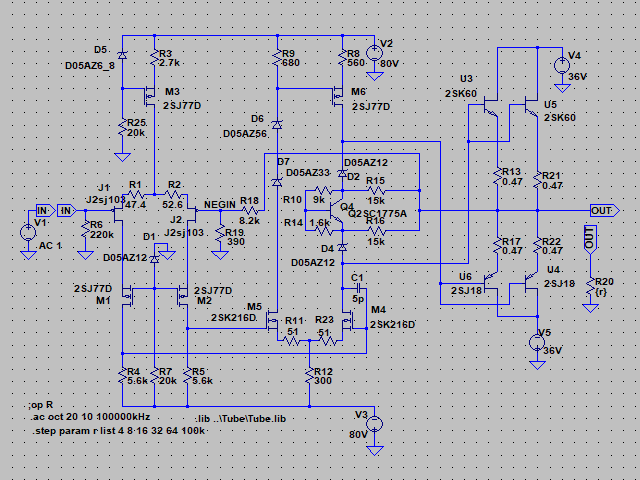

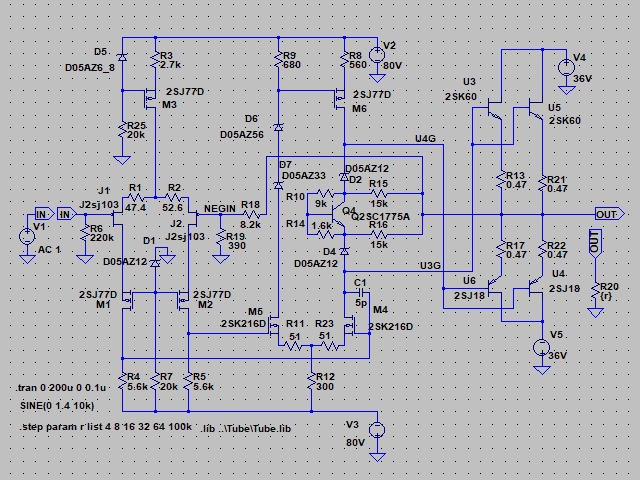

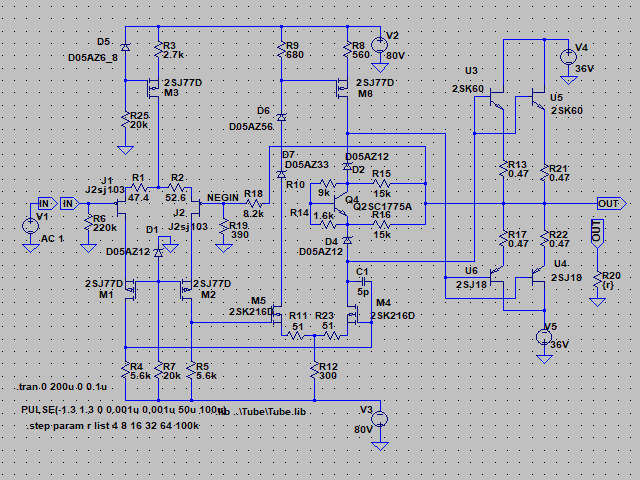

�E���X�A������ƍl���āA�����B

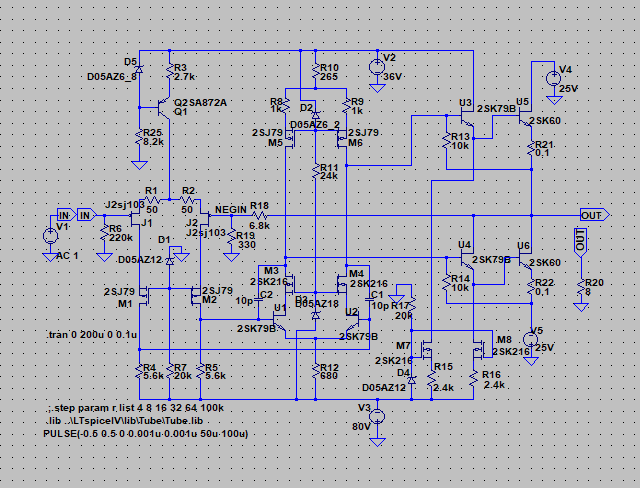

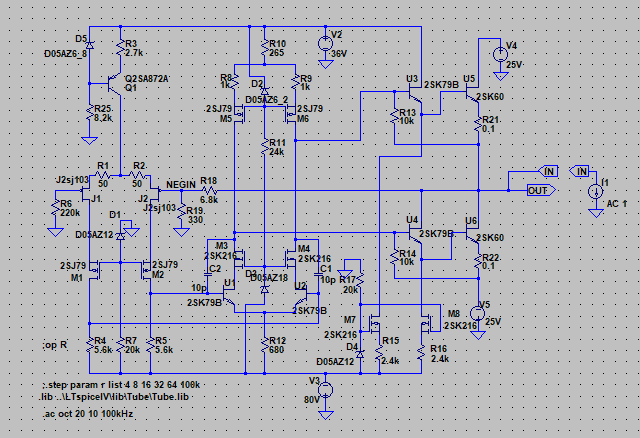

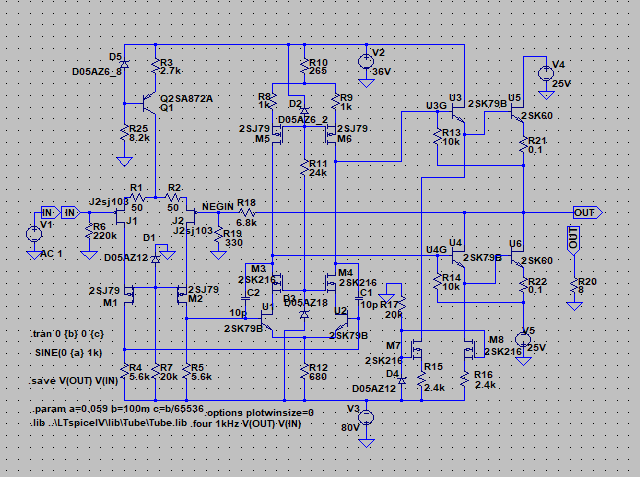

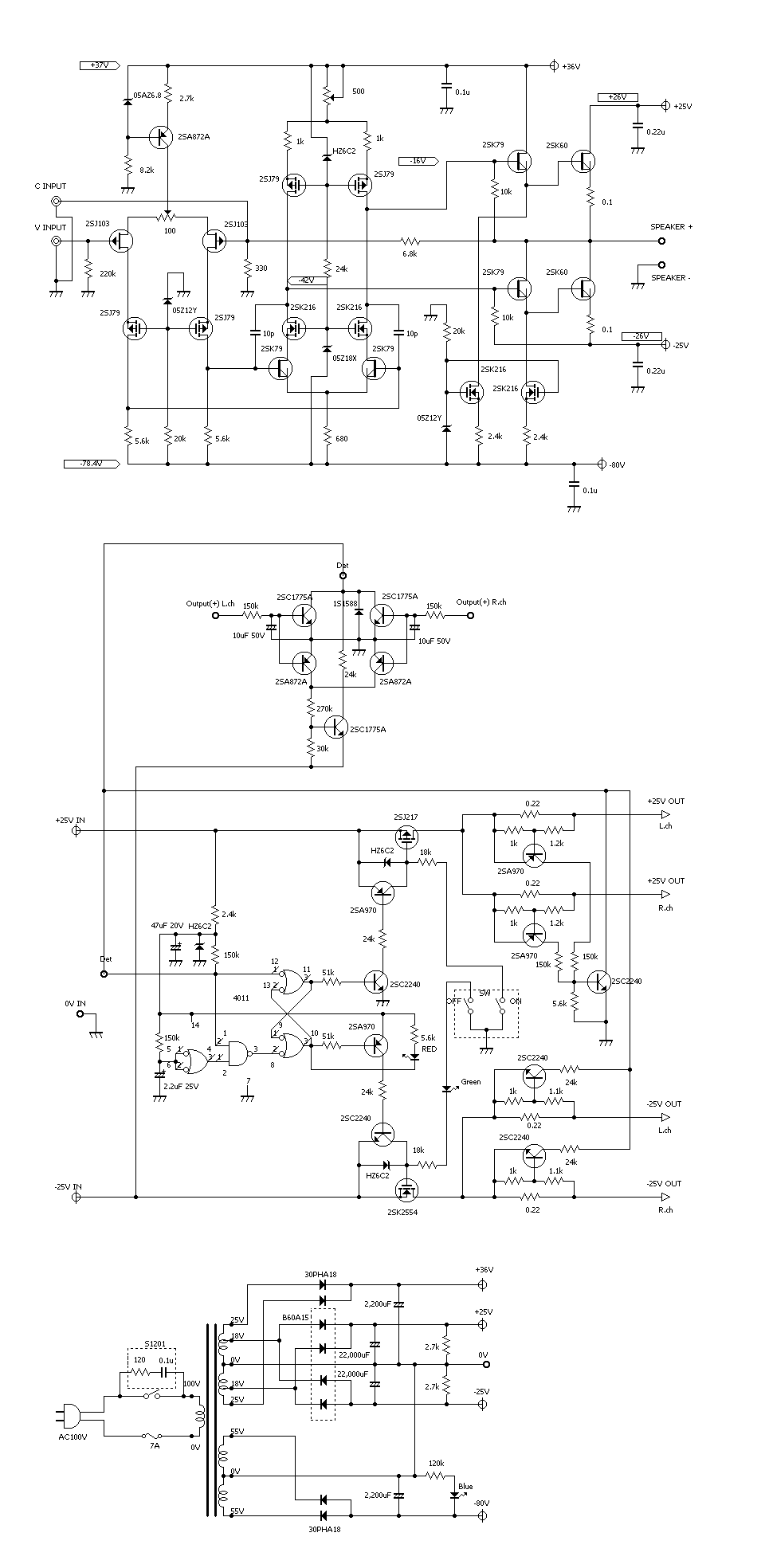

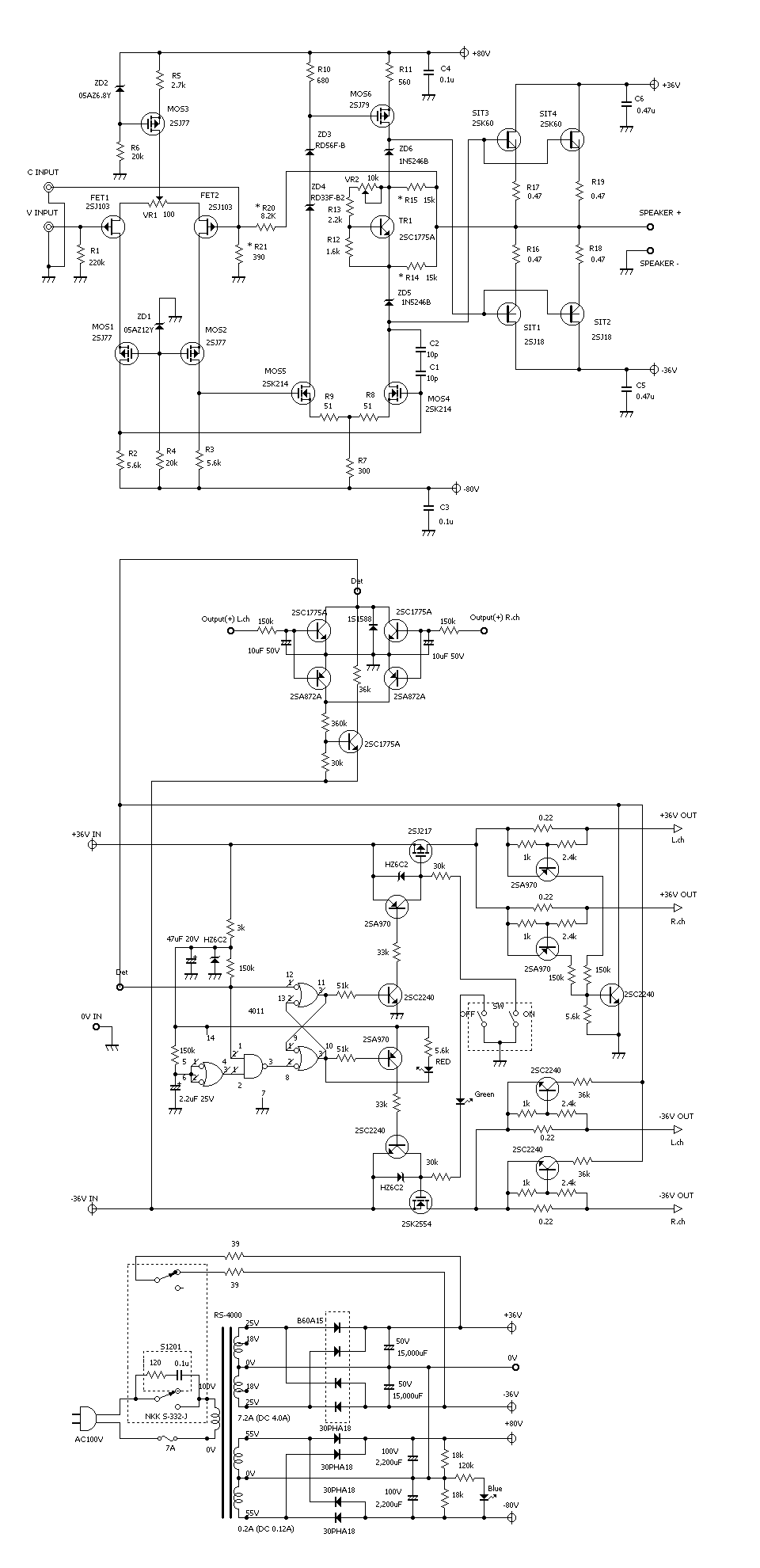

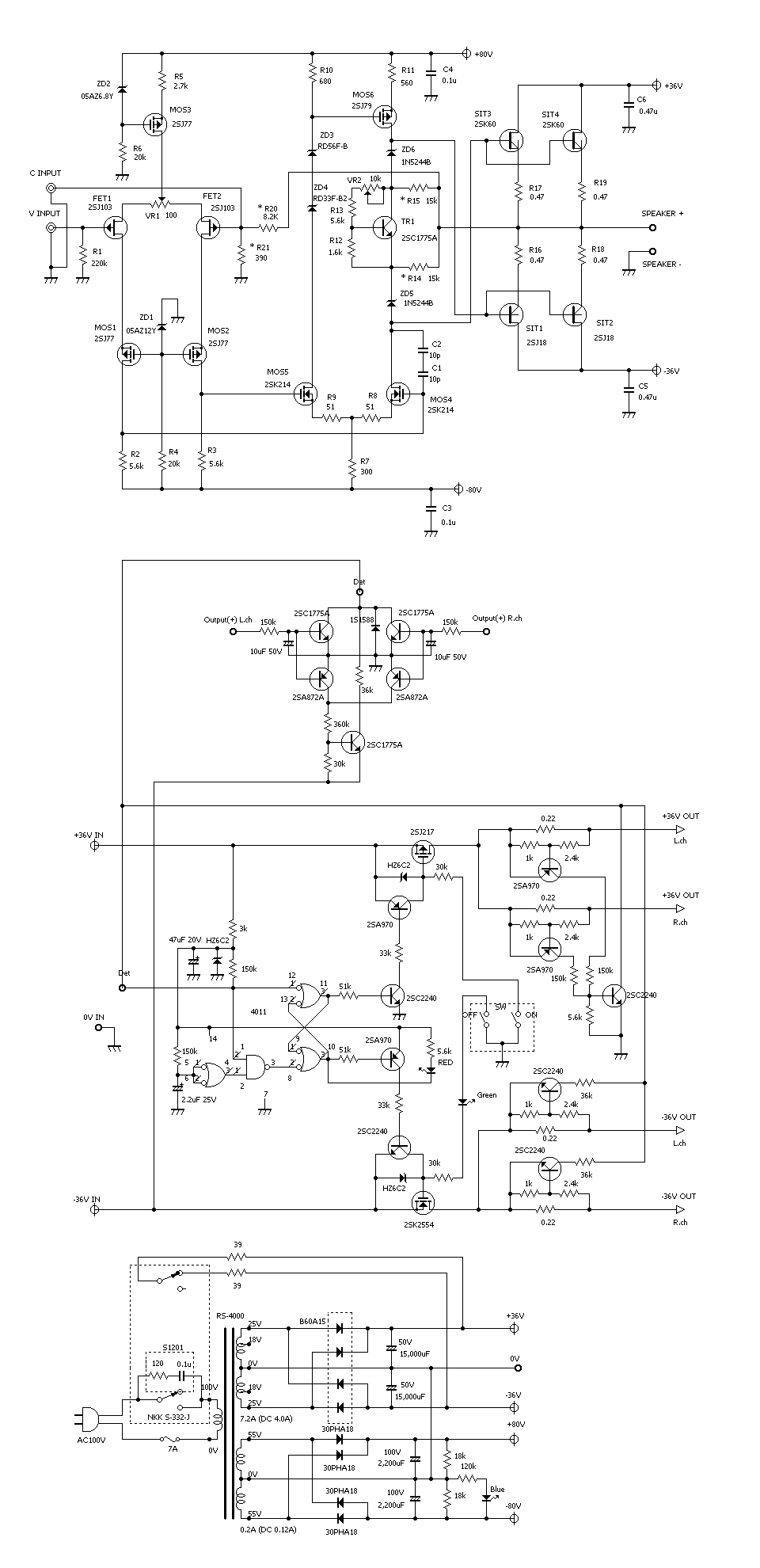

�EB-1���̊��S�Ώ̌^�͂�߁A�s���S�Ώ̌^�̓d���h���C�u�E�v�b�V���v���\�[�X�t�H���A�o�͒i�Ƃ���B

�E�d���g�����X�͏]�O�̂��̂����̂܂g���B

�E�ƁA�A���v�O�i�̓d���d���́}�W�OV���x��������B

�E�o�͒i�p�ɂ͏]�O�ǂ���Ɂ}�Q�TV���x�ł��ǂ��̂����A������������̂Ł}�R�UV���x��������B

�E�̂ŁA���̓d�����g���A�����āA�o�͒i���p���ڑ��ɂ��ăp���[�A�b�v���}�낤�B�K���g�����X�̗e�ʂ��\���B

�E�Q�r�i�P�W�|�Q�r�j�U�O�́A�Q�r�i�Q�O�`�|�Q�r�j�V�O�`�ɔ䂷�Ƃ������������̂ŁA�h���C�u�d���ɂ͂��傫�ȐU�����K�v�ɂȂ�B����āA�O�i�̓d���d���͏o�͒i���啪�����d�����K�v�B

�E��肢��ɑO�i�p�Ɂ}�W�O�u�̓d���������銪�����������ďd��B

�E�Ȃ��A�]�O�̉�H�f�q�Ŏg������̂͋ɗ͊��p�B�P�[�X�������̂܂܁B

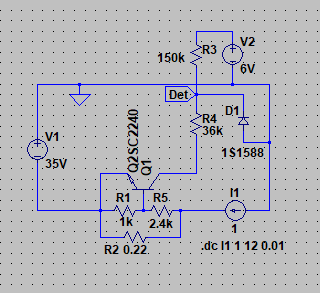

�E��������ƕ��M�\�͂͏]�O�̂܂܂Ȃ̂ŁA�I�i�f�q�̃A�C�h�����O�d���͊e�f�q�P�O�O��A�A�p���łQ�O�O��A�ƁA�]�O�^�̃V���O���łQ�O�O��A�������A�C�h�����O�d���Ɠ����ɂ���B�E�̃V�~�����[�V������H�ł��������Ă���B

�E����ł��A�I�i�f�q�̃A�C�h�����O���̑����͕Ѓ`�����l���ŏ]�O�^�łP�OW���������̂��P�S�D�SW�Ƒ�����B���A�]�O�^�ł͕��M��͂ق�̂艷�܂���x�Ȃ̂ŁA�܂��A���v���ȁB

|

|

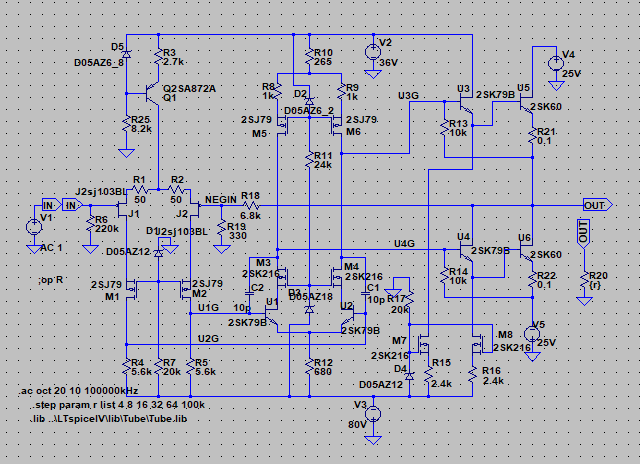

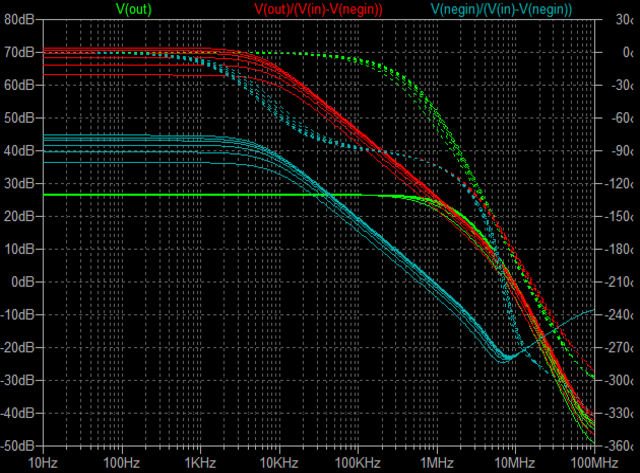

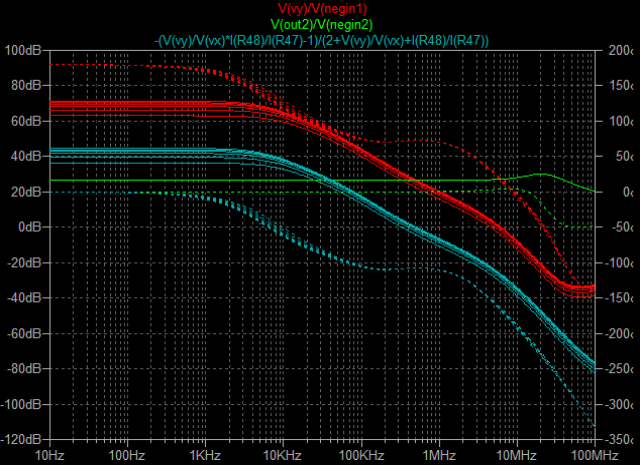

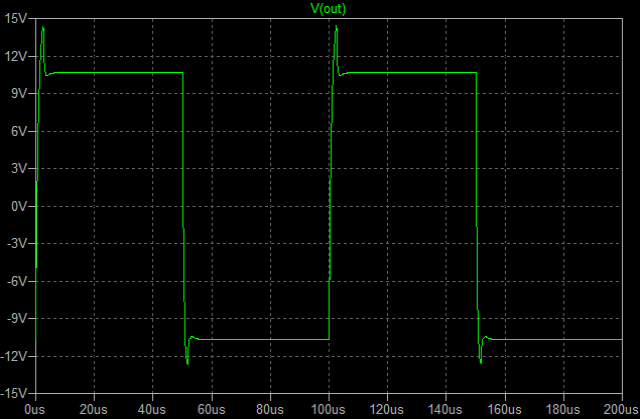

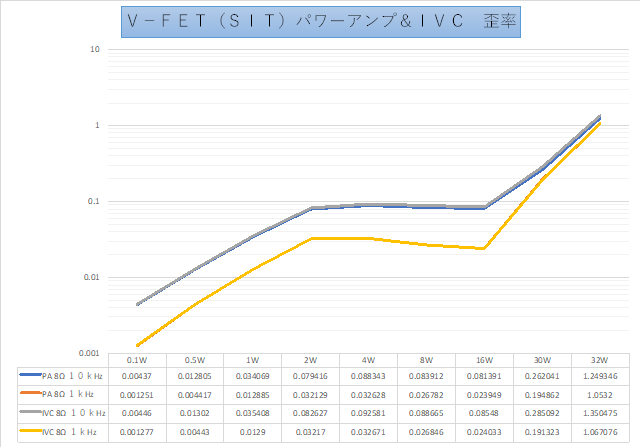

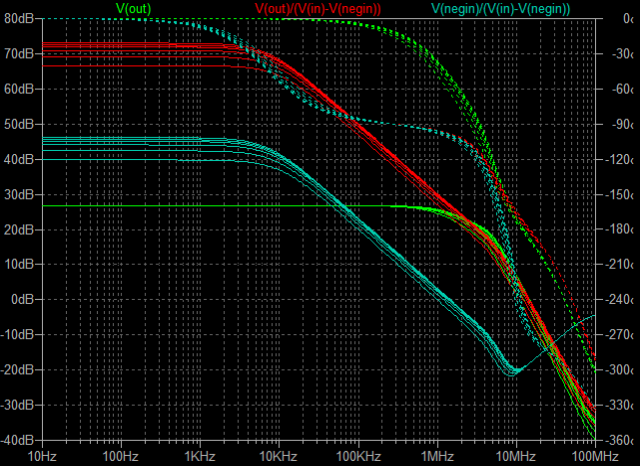

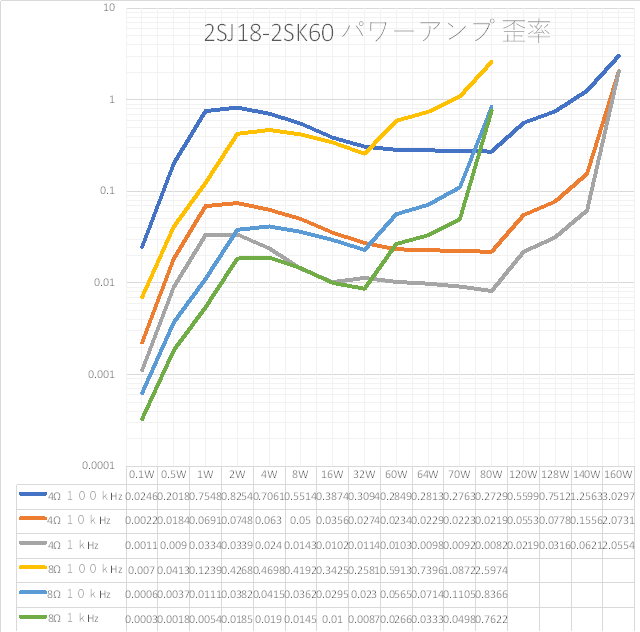

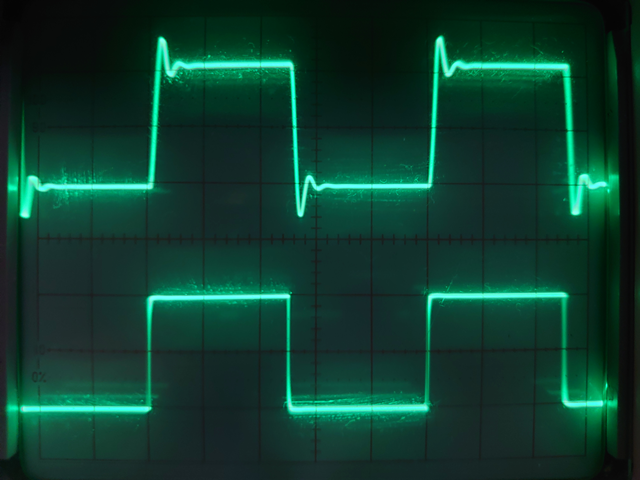

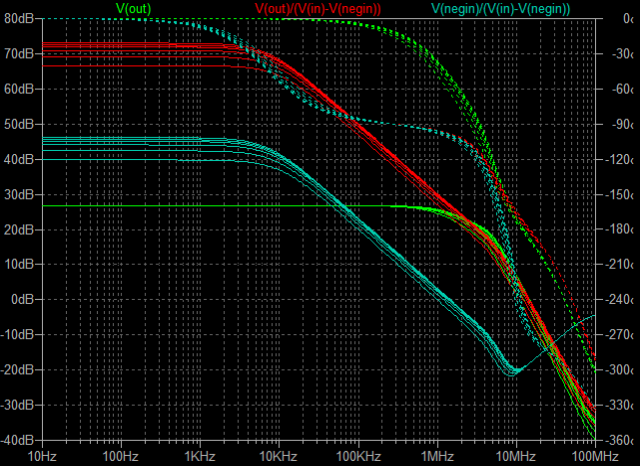

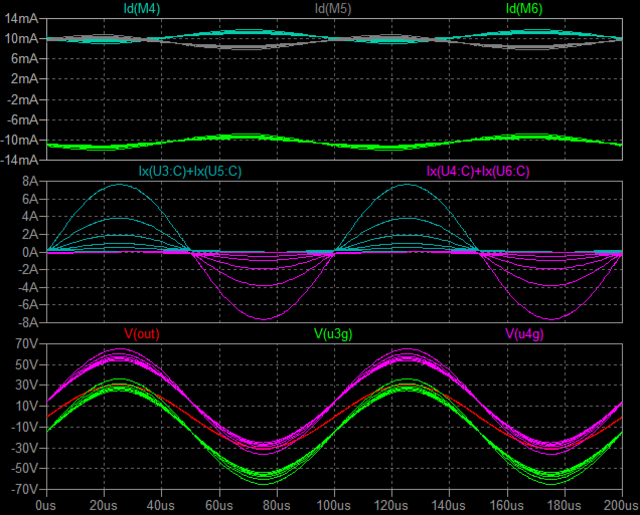

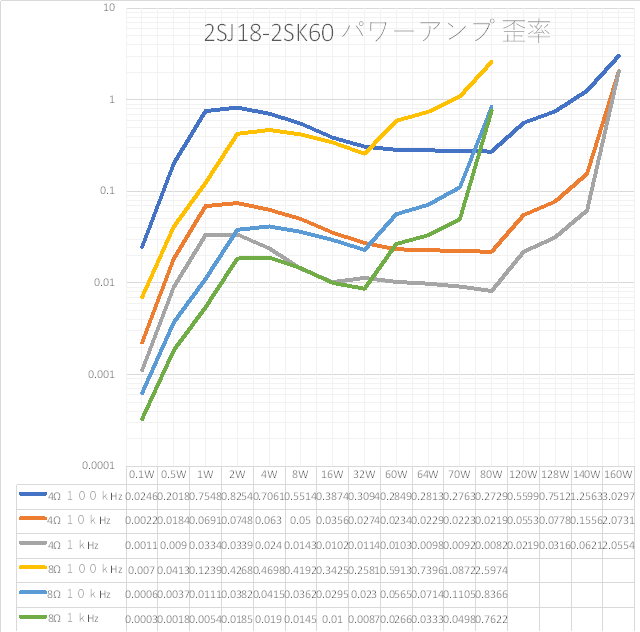

�E���̃Q�C��-���g�������B

�E�p�����g���b�N��͂ŁA�Ԃ��I�[�v���Q�C���A���N���[�Y�h�Q�C���A�����[�v�Q�C���ł���A�I�[�v���Q�C���ƃ��[�v�Q�C���́A�������ɕ��ׂ��S���A�W���A�P�U���A�R�Q���A�U�S���A�P�O�O�����i���׃I�[�v�������j�̏ꍇ�B

�E�̃N���[�Y�h�Q�C���͂Q�U�D�W���a���x�B

�E�I�[�v���Q�C���ƃ��[�v�Q�C���́A�]�O�̊��S�Ώ̌^�Ƃقړ����B

�E�Q�i�ڍ����A���v�̂Q�r�j�Q�P�U�ɓd���A�҂��|���āA��肢��ɒ��x�ǂ��I�[�v���Q�C���Ɏ��܂����B���āA�ŏI�I�ɂ͕s���S�Ώ̒�R�l�̒����Ŏ��߂Ă���B

�E�p���[IVC���쎞�̓����́A����܂ł̌o������قړ����Ǝv����̂ŁA�~�h���u���b�N�@�ɂ���p���[IVC���쎞�̃V�~�����[�V�����͏ȗ��B |

|

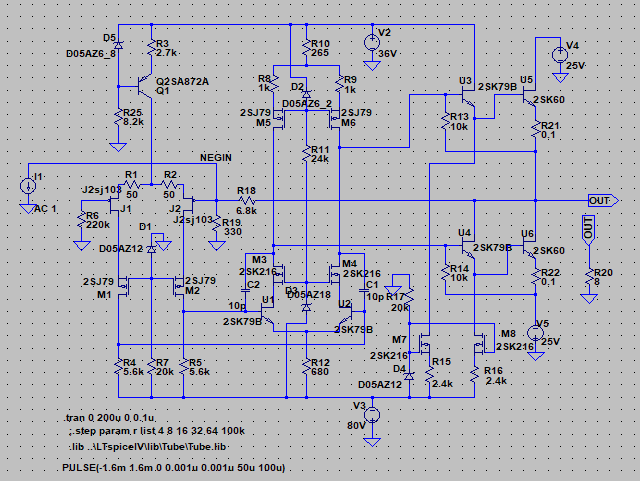

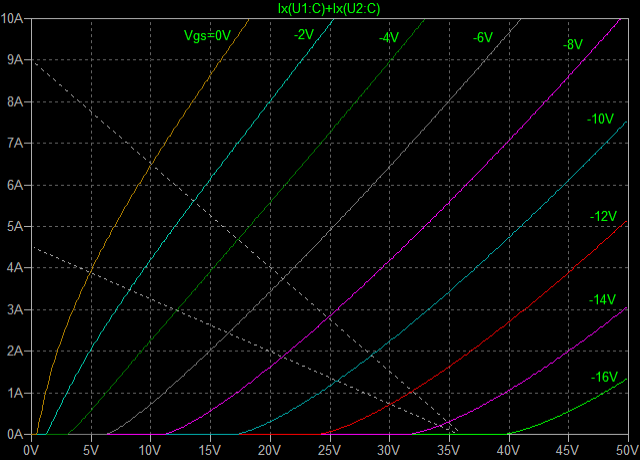

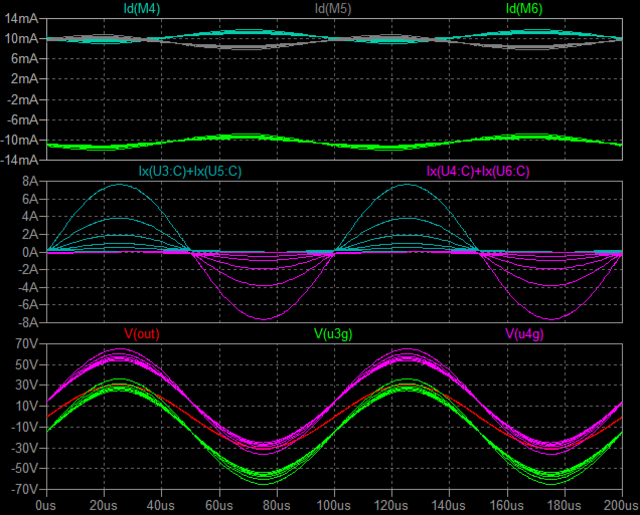

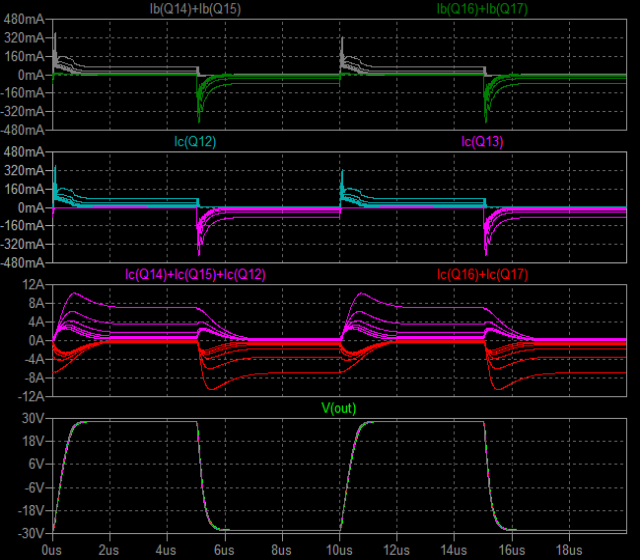

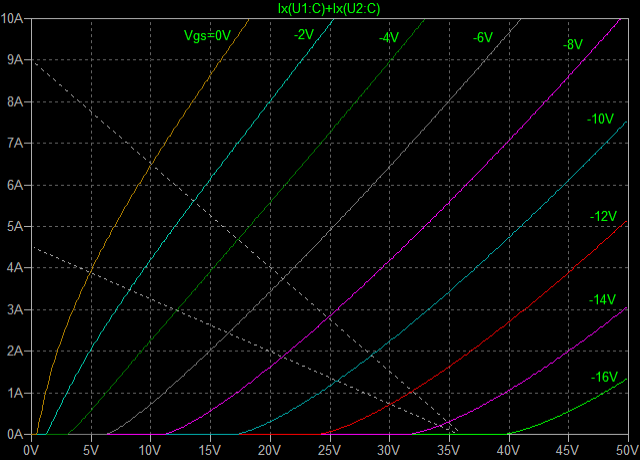

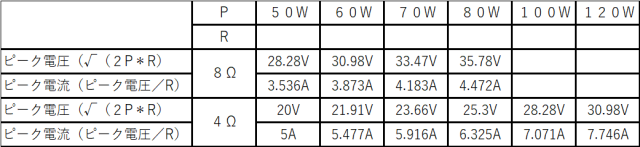

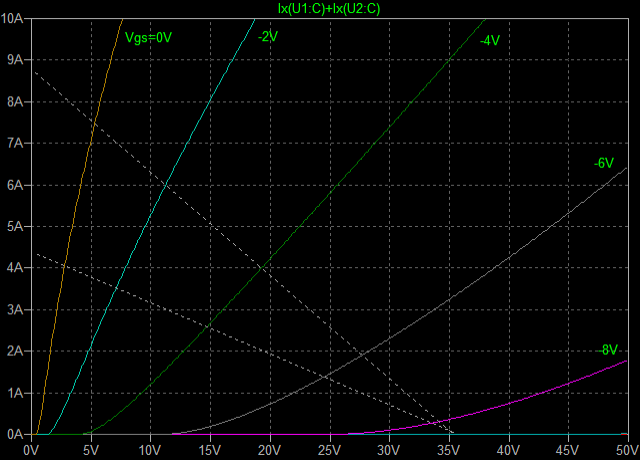

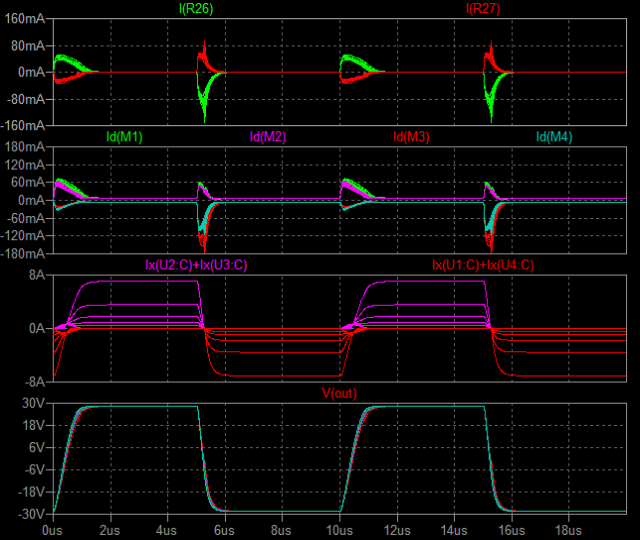

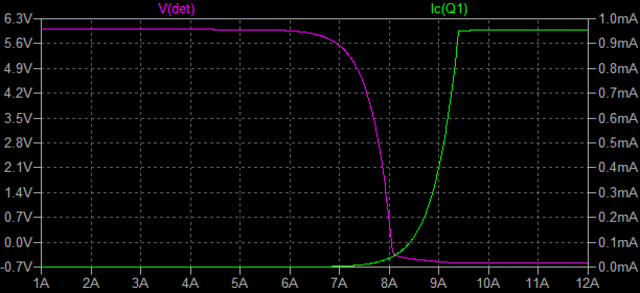

�E����łǂꂾ���̏o�͂����҂ł��邩���ς邽�߁A�Q�r�j�U�O���p���ڑ������ꍇ�̐Ó������ς�B

�E�d���d���R�U�u�ŕ��ׂW���ƂS���̏ꍇ�̃��[�h���C����_���ň����Ă���B�����W���ꍇ�ŏオ�S���̏ꍇ�B

|

|

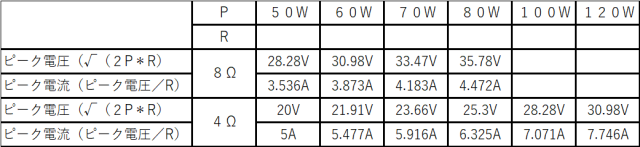

�E�E�̓p���[�A���v�̏o�͒l�ɗv����o�͂̃s�[�N�d���l�ƃs�[�N�d���l�B

�E�𗬂ł��邩��v���X�}�C�i�X�Ƃ��K�v�B

�E����Ə�̃O���t����A�ǂ̒��x�̏o�͂��邩���ς�B

|

|

�E���ׂW���̏ꍇ�A�O���t�̂W���̃��[�h���C���ŁA�o�C�A�X�d��Vg�����OV�̃��C���Ƃ̌�_�̃h���C���d���l���SA��ł��邩��A�d���s�[�N�l���SA�ȏ�ƂȂ�V�OW�ȏ�̏o�͂͂������������Ȃ��B

�E�o�͂U�OW�ł́A�K�v�s�[�N�d���l���R�D�W�V�RA�ł��邪�A���傤���o�C�A�X�d��Vg�����OV�̃��C���Ƃ̌�_�̃h���C���d���l�����̒��x�̂悤�ł��邩��A�d���I�ɂ͉\�͈̔͂����m��Ȃ��B�d���I�ɂ͂��̍ۂ̃h���C���|�\�[�X�ԓd���͂TV��ŁA�o�͂̃s�[�N�d�����R�O�D�X�WV�ł��邩��A�d���d�����R�UV�ł���A�d���I�ɂ��\�͈̔͂����m��Ȃ��B

�E����āA���ׂW���ł́A�T�OW�͓����A�U�OW�����҂ł���\��������A�ƌ������Ƃ���B

�E���ɕ��ׂS���̏ꍇ�B�o����W�����ׂ̏ꍇ�̂Q�{�̏o�͂����҂������Ƃ��낾�B

�E���A�O���t�̂S���̃��[�h���C���ŁA�o�C�A�X�d��Vg�����OV�̃��C���Ƃ̌�_�̃h���C���d���l���U�D�TA���x�ł��邩��A�d���s�[�N�l������ȏ�K�v�ƂȂ�P�O�OW��P�Q�OW�̏o�͂͂��������]�߂Ȃ��B

�E�o�͂��W�OW�ł���A�d���s�[�N�l�͂U�D�R�Q�TA�ł��邵�A���̍ۂ̃h���C���|�\�[�X�ԓd���͂P�OV��ŁA�o�͂̃s�[�N�d�����Q�T�D�RV�ł��邩��A�d���d�����R�UV�ł���A�d���I�ɂ��\�͈̔͂����m��Ȃ��B

�E�Ƃ������ƂŁA���ׂS���̏ꍇ�̍ő�o�͂́A�����Ă��W�OW�ȉ��ɂƂǂ܂�A�ƌ������Ƃ���B

�E����ɁA�d�������艻���Ă����ł͂Ȃ��̂ŁA���ۂ͏o�͑��ƂƂ��ɏo�͒i�p�d���d���͉����邩��A���@�̍ő�o�͂͂����Ɖ�����B

�E�Ȃ��A����SPICE���f���͎茳�ɂ��郉���N�T�W���Q�r�i�P�W�A�Q�r�j�U�O��͂������̂ŁA���̃����N�ɔ䂵�ĖO�a�d�����Ⴍ�A�J�b�g�I�t�d�����������m�̂悤�B�����N���Ⴆ�ΖO�a�d���A�J�b�g�I�t�d���͑啪�قȂ�悤�Ȃ̂ŁA���̏ꍇ�A�d���d�����A�v���������v������B

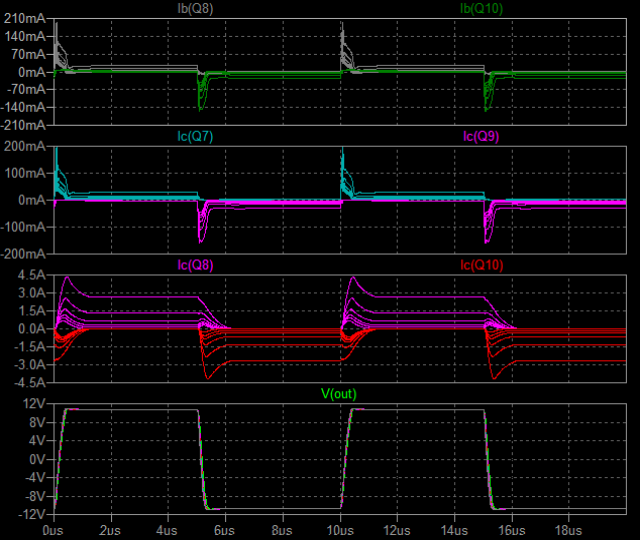

|

�E�Ƃ���ŁA�Q�r�j�V�O���p���ڑ������ꍇ�̐Ó����B�d���d���R�T�u�ŕ��ׂW���ƕ��ׂS���̏ꍇ�̃��[�h���C���������Ă���B���l�Ɋς�ƁA�W�����ׂł͂V�OW��A�S�����ׂł͂P�Q�OW��̏o�͂����҂ł��邱�Ƃ�������B

�E�Q�r�j�V�O�͂Q�r�j�U�O�ɔ䂵�āA��C���s�[�_���X���ׂł���o�͂�������������B�܂��A���������傫���̂őO�i�̓d���d�������Ⴍ�ĉB

|

|

�E�P�D�S�u���|���P�O���g�������g����͂��A�e���̓�����ς�B

|

|

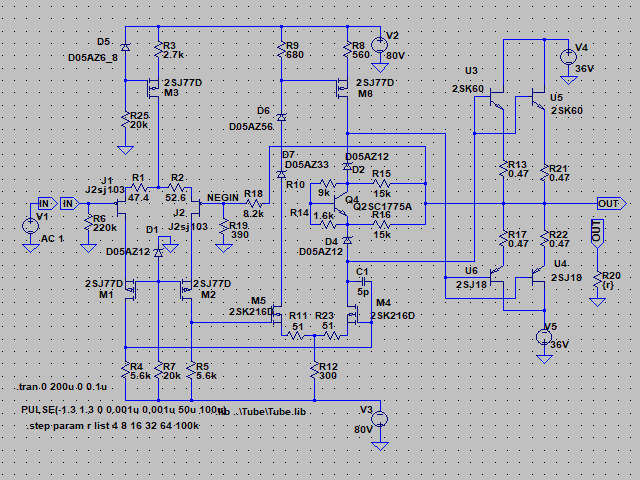

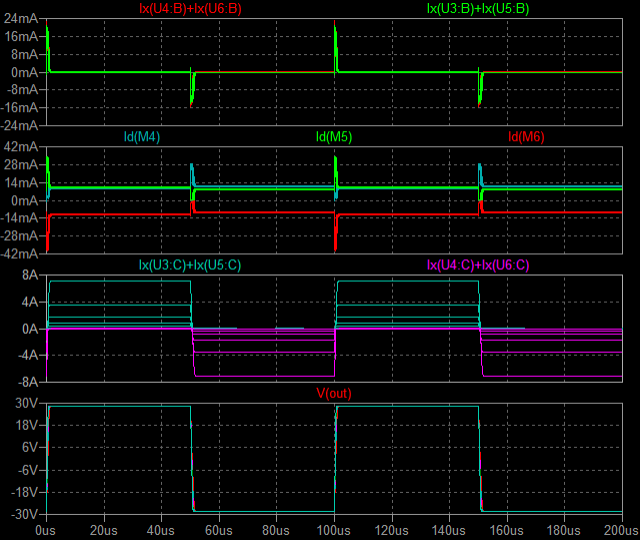

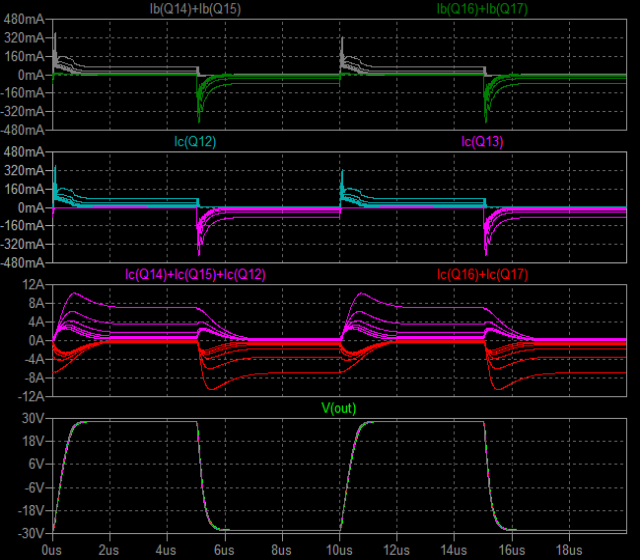

�E�ǂ���p�����g���b�N��͂ŁA�U�����傫�������畉�ׂ��S���A�W���A�P�U���A�R�Q���A�U�S���A�P�O�O�����i���J�������j�̏ꍇ�B

�E��ԉ����o�͓d�ʁi�ԁj�ƏI�i�Q�r�i�P�W�i�s���N�j�ƂQ�r�j�U�O�i�j�̃Q�[�g�d�ʁB

�E�^�́A�I�i�Q�r�i�P�W�̃p���̃h���C���d���l�i�s���N�j�ƂQ�r�j�U�O�̃p���̃h���C���d���l�i�j�B

�E������ς�ƂS�������̃s�[�N�d���l���W�`�߂��ɂȂ��Ă��邪�A��̐Ó����}�Ŋς��ʂ�A�S�����ׂłU�D�TA�ȏ�̏o�͓͂�����͂����Ȃ��A���̂S�����ׂł̌��ʂ́A����SPICE���f�������m�łȂ����Ƃɂ��t�F�C�N�ł���B�v����ɉE�ł̂S�����ׂł̌��ʂ͂ǂ���t�F�C�N�B

�E���A���ׂW���ł̌��ʂ́A�s�[�N�d���l���SA��ł���A���̍ۂ̏I�i�̃Q�[�g�d�ʂ��o�͓d�����Ă��Ȃ����Ƃ���A���x���E�o�͂�����ł��邱�Ƃ�������B�W���ȏ�̕��ׂł̌��ʂ͐M���ɑ���B���ȁB

�E��ԏ�͂Q�i�ڍ����A���v�̂ӂ��̂Q�r�j�Q�P�U�ƃJ�����g�~���[�̂Q�r�i�V�V�̃h���C���d���l�����A���͂Ȃ��B�Ȃ��A�����̃A�C�h�����O�d���l�͂P�O��A���x�Ƃ���Ȃ�ɑ傫�����Ă���B���R�́A���ɁB

�E�p���[IVC���쎞�̓����́A����܂ł̌o������قړ����Ǝv����̂ŁA�~�h���u���b�N�@�ɂ��p���[IVC���쎞�̃V�~�����[�V�����͏ȗ��B

|

|

�E���́}�P.3�u���|���̂P�O���g�����`�g�������ς�B

|

|

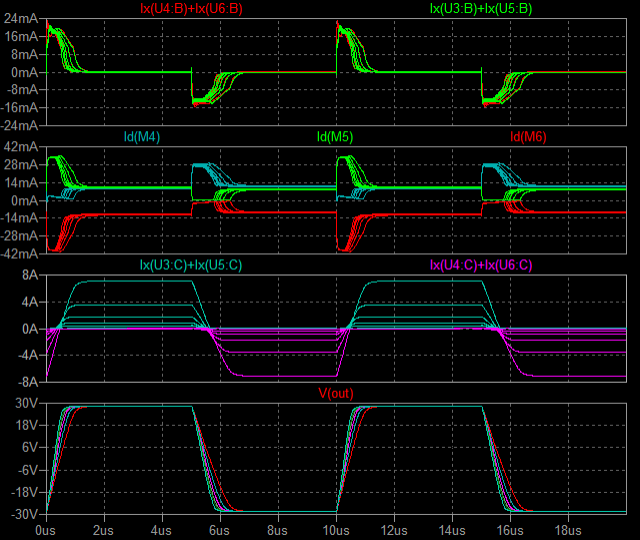

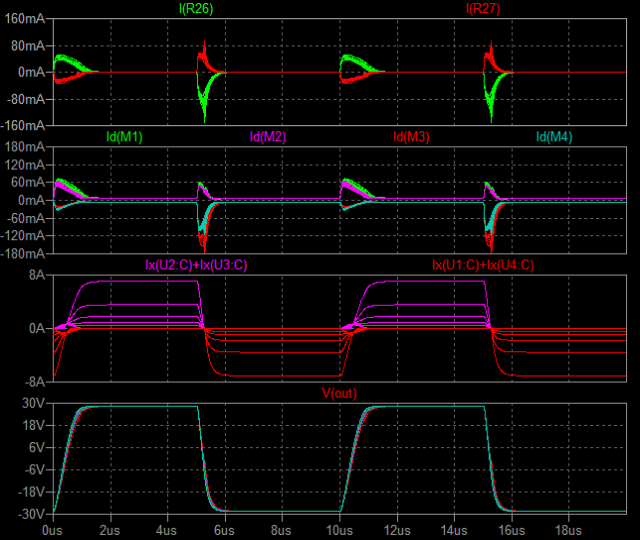

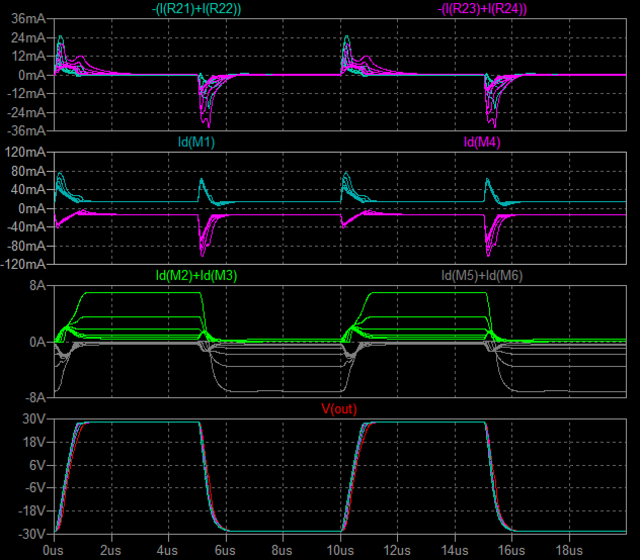

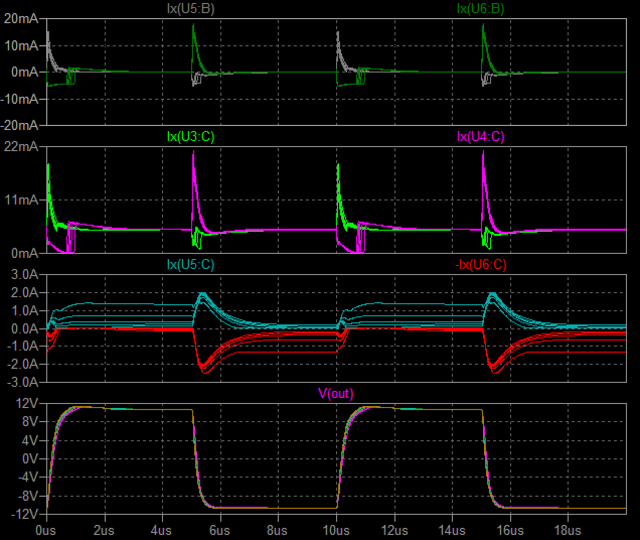

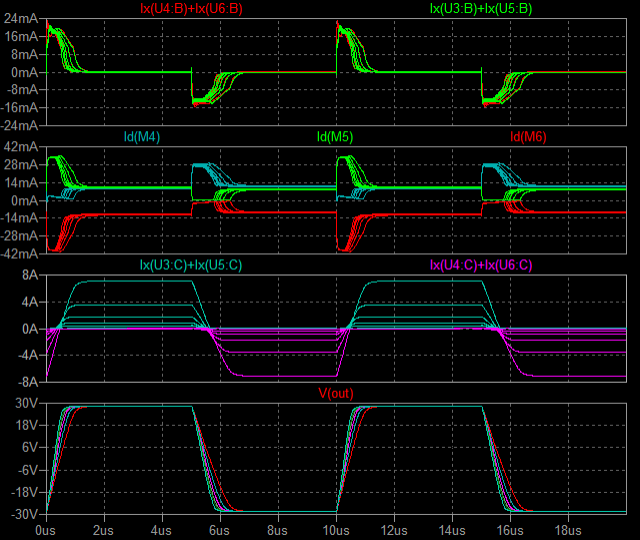

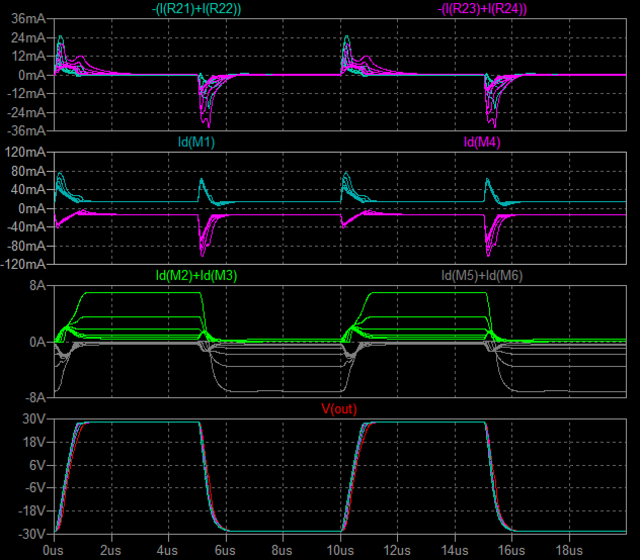

�E���ׂ��S���A�W���A�P�U���A�R�Q���A�U�S���A�P�O�O�����i���׃I�[�v�������j�Ƃ����ꍇ�̃p�����g���b�N��́B��������ׂS���̏ꍇ�̌��ʂ̓t�F�C�N�ł���B�ŁA��ԉ����o�͔g�`�����A���R�ǂ̕��ׂł����������B

�E������Q�Ԗڂ́A���̏ꍇ�̂Q�rJ�P�W�p���̍��v�h���C���d���g�`�i�s���N�j�ƂQ�rK60�p���̍��v�h���C���d���g�`�i�j�B�ǂ�����d���l���傫�������畉�ׂ��S���A�W���A�P�U���A�R�Q���A�U�S��,�P�O�O�����̏ꍇ�B

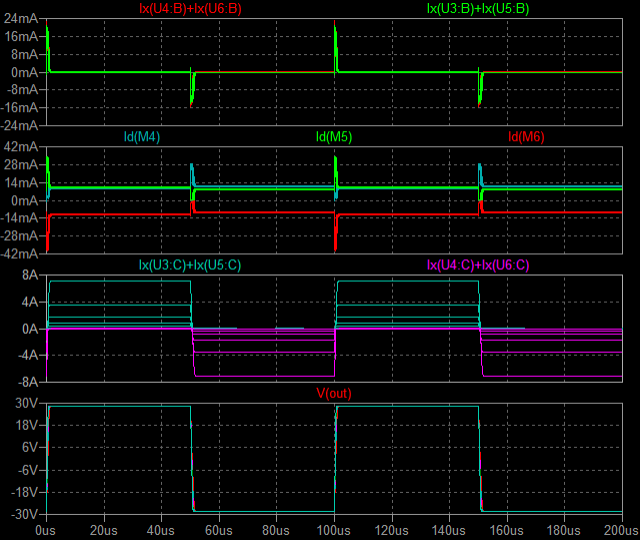

�E�ォ��Q�Ԗڂ��A�Q�i�ڍ����A���v�̂l�S�A�l�T�A�����ăJ�����g�~���[M�U���h���C���d���g�`�B���`�g�̗����オ��A�����莞��M4�AM�T�AM�U�Ƃ��Ƀp���X�d��������Ă���B

�E��ԏオ�A���̍ۂ̂Q�r�i�P�W�ƂQ�r�j�U�O�̃Q�[�g�Ɍ����ė����d���l�B�ʏ�͂O���`�����A���`�g�̗����オ��Ɨ�����̏u�ԂɁA�Q�rJ�P�W�ƂQ�rK�U�O�̃Q�[�g�Ɍ����ăp���X�d��������Ă���B�����d�Ȃ��Ă��邪�A����莞�͋��ɂQ�O���`���x�A�����莞�ɂ͋��Ɂ|�P�U���`���x����Ă���B����́A�Q�r�i�P�W�ƂQ�r�j�U�O�̓��͗e�ʓ����[���d����d���ɑ���Ȃ��B�����āA���ꂪ�Q�i�ڍ����A���v�̂l�S�A�l�T�A�����ăJ�����g�~���[M�U�ɗ����p���X�d���̐��́B

�E�J�����g�~���[�������A���v�̓���d�����e�P�O���`�Ȃ̂ŁA�����̕Е��ɗ����ő�d���͂Q�O���`�B���Ǝv���Ă����̂����A���̌��ʂ��炷��ƁA�ő�d�����S�O���`�ɂȂ��Ă���B���ہA�q�P�Q�̓d�����ڂ��ς�Ƃ��̃s�[�N���ɂS�O���`����Ă���B���̂��H�@�m��Ȃ��B

�E�T�Z�A�I�i�̂u�|�e�d�s�i�r�h�s�j�̓��͗e�ʓ����P�X�O���~�S���V�U�O���e�ƂȂ�̂ŁA�����ł̃X���[���[�g���Q�O�^�V�U�O���Q�U�D�RV�^���r������A�o�͂��|�R�O�u����{�R�O�u�܂ŗ����グ��ɂ͂U�O�^�Q�U�D�R���Q�D�Q�W���r�̎��Ԃ�v����B�ƁA�v���Ă����̂����A�S�O���`�����̂Ȃ�A�X���[���[�g���S�O�^�V�U�O���T�Q�D�U�u�^���r�A�]���āA�o�͂��U�O�u�����グ�邽�߂ɂ͂U�O�^�T�Q�D�U���P�D�P�S���r�̎��Ԃ�v����Ƃ������ƂɂȂ�B

|

|

�E���͕��`�g���P�O�O��Hz�ɂ���ƁA���̕ӂ���蕪����₷���B

�EV-FET�iSIT�j������Ȃ�ɓ��͗e�ʓ�������̂ŁA�������g���܂Ńh���C�u���悤�Ƃ���A����Ȃ�̓d���������ł���h���C�o�[���K�v�B

�E�Q�r�i�Q�OA�|�Q�r�j�V�OA �p���[�A���v���p���[�h�u�b�ł́A�Q�r�i�Q�OA�ƂQ�r�j�V�OA�̓��͗e�ʓ����Q�r�i�P�W��Q�r�j�U�O�̓��͗e�ʓ��ɔ�r����Ƃ��Ȃ�傫���̂ŁA�v�b�V���v���t�H���A�h���C�o�[�Ńh���C�u�����B

�E���A�Q�r�i�P�W�ƂQ�r�j�U�O�ł���A�p���ł����Ă��A�Q�i�ڍ����A���v�ɉ\�ȓ���d���ŁA����Ȃ�ɑ��F�̂Ȃ����������������̂ł͂Ȃ����B�v����A�J�����g�~���[���ׂQ�i�ڍ����A���v���v�b�V���v���h���C�o�[�Ƃ��ď\���ɋ@�\����̂ł͂Ȃ����B

�E�Ǝv���āA�����A���v�̕Е��ɍő�Q�O��A�����悤�ɁA�Q�i�ڍ����A���v�̓���_���P�O��A�Ƃ����̂ł���B

�E��������A�o�͂��|�R�O�u����{�R�O�u�܂ŗ����グ��ɂ͂U�O�^�Q�U�D�R���Q�D�Q�W���r�ƁA����Ȃ�̑��x�̃A���v�ɂȂ�͂��A�ƍl�����̂��B

�E���A�Q�i�ڍ����A���v�̕Е��ɂ͂S�O��A�����̂ł������B

�E���̂��H�@�m��Ȃ��B

�E���ʁA�o�͂��U�OV�����グ�邽�߂ɂU�O�^�T�Q�D�U���P�D�P�S���r�̎��Ԃ�v����Ƃ������ƂʼnE�̂悤�Ȍ��ʂɂȂ��Ă���H

�E�܂��A�������B�i���j

�E�������ꂪ�{���Ȃ�A�߂���n�����s���S�Ώ̌^�d���h���C�u�E�v�b�V���v���t�H���A�o�͒i�̗p�̃p���[�A���v�B�Ɠ��l�̑��x�̃p���[�A���v���A�v�b�V���v���t�H���A�h���C�o�[�Ȃ��ŏo�����A�Ƃ������ƂɂȂ�B

|

|

�E��r�̂��߁A

�E���l�A�Q�r�i�Q�OA�|�Q�r�j�V�OA �p���[�A���v���p���[�h�u�b�̏ꍇ�B

|

|

�E�Q�r�i�S�X�|�Q�r�j�P�R�S �p���[�A���v���p���[�h�u�b�̏ꍇ�B

|

|

�E�����āA�Q�rA�P�O�O�VA�\�Q�rC�Q�R�R�VA

�p���[�A���v���p���[�h�u�b�̏ꍇ�B

�E���`�g�̗����A�����莞�A�o�͒i���ђʓd���������Ă���B

�E�����P�O�O��Hz���`�g�����ł́A�ǂ��ς���Q�r�i�Q�OA�|�Q�r�j�V�OA �p���[�A���v���p���[�h�u�b�ł��A�Q�r�i�S�X�|�Q�r�j�P�R�S �p���[�A���v���p���[�h�u�b�ł��ђʓd���������Ă���B���A��Ԍ����Ȃ̂������Q�rA�P�O�O�VA�\�Q�rC�Q�R�R�VA �p���[�A���v���p���[�h�u�b�B����A������Q�r�i�P�W�|�Q�r�j�U�O �p���[�A���v���p���[�h�u�b���ђʓd���̋C�z�͑S���Ȃ��悤�B

�E�ŁA�Q�rA�P�O�O�VA�\�Q�rC�Q�R�R�VA �p���[�A���v���p���[�h�u�b�̏ꍇ�̊ђʓd���́A�o�͒i�㉺�p���[�g�����W�X�^�̃x�[�X�ԂɂP���e���p���ɓ���邾���łȂ��Ȃ�B

|

|

�E�����B

�E���A�ʏ킻�����������g�M���͓��͂���Ȃ��̂Ŗ����B

|

|

�E�o�b�e���[�h���C�u �Q�rA�U�S�X�|�Q�rD�Q�P�W

�p���[�A���v���p���[�h�u�b�̏ꍇ�B

�E������A���`�g�̗����A�����莞�A�o�͒i���ђʓd���������Ă���B������͂�����i�a�k�h���C�o�[�����A���܂���ʂ͂Ȃ��悤�B

�E����̏ꍇ���o�͒i�㉺�̃x�[�X�ԂɂP���e�����邾���łȂ��Ȃ�͓̂��������A����Ă��Ȃ��B

�E�Ƃ���ŁA������ɍ�����p���[�A���v���p���[�h�u�b�̃X���[���[�g���A�������Ă݂�ƍ���̂Q�r�i�P�W�|�Q�r�j�U�O

�p���[�A���v���p���[�h�u�b�Ƃقړ����B

�E�����̃X���[���[�g�́A���i�����A���v�̓���d���ƂQ�i�ڍ����A���v�̂a�|�b�i�f�|�c�j�Ԃ̈ʑ���b�ɂ���Č��܂������̂��낤�B

�E���i�̓���d���������Ȃ̂ŁA�ʑ��C���T��F���o�b�e���[�h���C�u �Q�rA�U�S�X�|�Q�rD�Q�P�W

�p���[�A���v���p���[�h�u�b����ԍ����B

�E�����́A����̂Q�r�i�P�W�|�Q�r�j�U�O

�p���[�A���v���p���[�h�u�b�̂悤�ɏI�i�̓�����Ō��܂��Ă��Ȃ��̂ŁA�����𑽏��������A����������ƍ����ɂ��邱�Ƃ͉B

�E���A�ʂɂ���ŕs���������ł��Ȃ��B�̂ŁA���̂܂܂ŗǂ��B

|

|

�E���̍ہA�]�O�̂a�|�P�^�C�v��V-FET�i�r�h�s�j���S�Ώ̌^�p���[�A���v���p���[�h�u�b�̂P�O�O��Hz���`�g�������ς�B

�EMOS-FET�����f�����O��������ƘM����D�^�C�v�ɂȂ��Ă���B

�E���͂́}�O�D�TV���|���B

�E���ׂ͂W���A�P�U���A�R�Q���A�U�S���A�P�O�O���g���̃p�����g���b�N��́B�Q�r�j�U�O�̃V���O���v�b�V���v���ł͂S�����ׂ͖����B

|

|

�E��ԉ����o�͔g�`�B

�E�܂��܂��Y��B��̕��łP�O���g�����`�g�������ς��ۂɂ́A�����A������ɂ��Ȃ�̃I�[�o�[�V���[�g�A�A���_�[�V���[�g���o�Ă������A�����MOS-FET�̃��f�����O�������������߂̂悤�B�����A����ł�����莞�ɋ͂��ɃI�[�o�[�V���[�g������B

�E������Q�Ԗڂ��o�͒i�㉺�̂Q�r�j�U�O�̓d���g�`�B����莞�͂��܂��Y��łȂ��B�����莞�ɂ͂��Ȃ�̊ђʓd��������Ă���B

�E�ォ��Q�Ԗڂ��h���C�o�[�Q�r�j�V�X�̓d���g�`�B�P�ԏオ�Q�r�j�U�O�̃Q�[�g�Ɍ����ė����d���g�`�B

�E���`�g����莞�ɂ̓h���C�o�[�ł���Q�r�j�V�X����I�i�Q�r�j�U�O�̓��͗e�ʓ��̏[�d�̂��߂̓d�����\���ɋ����������̂́A���̗����莞�ɂ͂��̕��d�̂��߂̓d�����\���ɂ͋z�����܂�Ȃ��B

�E�̂Ŋђʓd����������H

�E�V���O���t�H���A�h���C�o�[�ł͖����H

|

|

�E�P�Ȃ�V�~�����[�V�����B�M���Ă͂����Ȃ��B

|

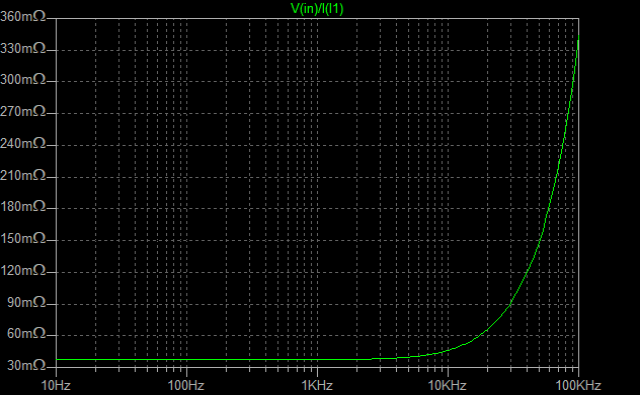

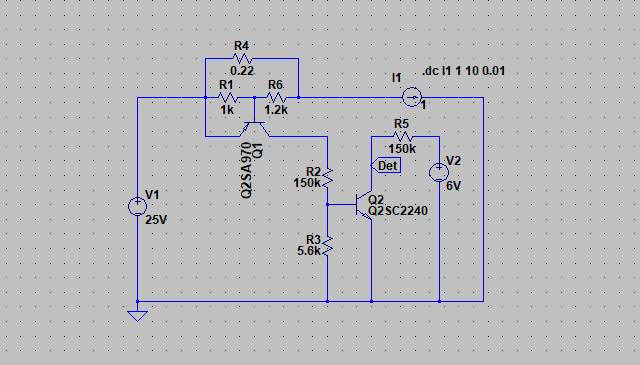

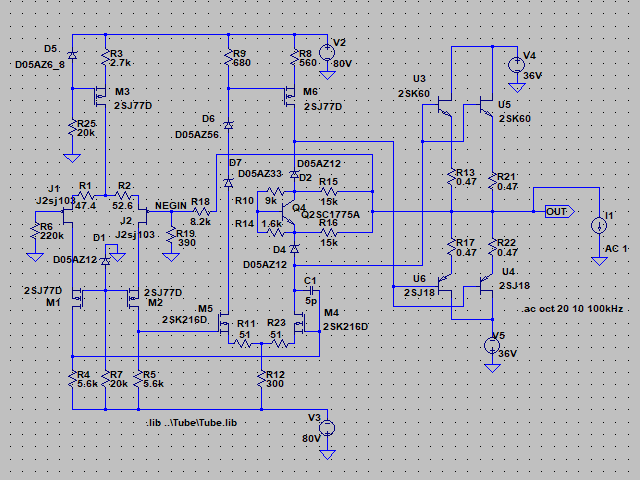

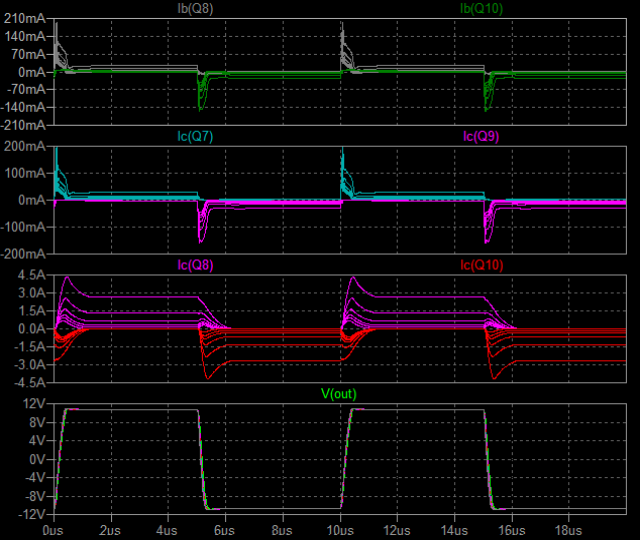

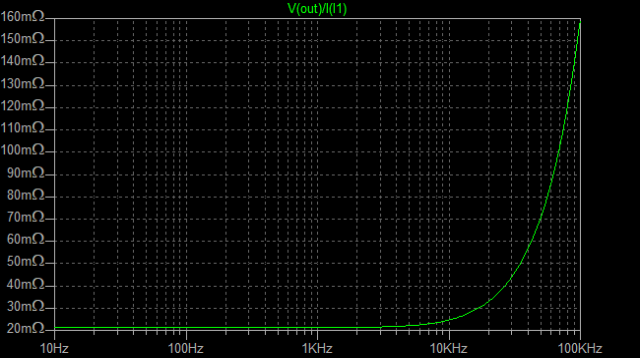

�E�d�������@�ŏo�̓C���s�[�_���X���ς�B

|

|

�E���łQ�P�����A�P�O�O���g���łP�T�X�������x�B

�E�p���[IVC���쎞�̓����͑�����ȗ����邪�A�قړ������낤�B

|

|

�E�c�����ς�B

|

|

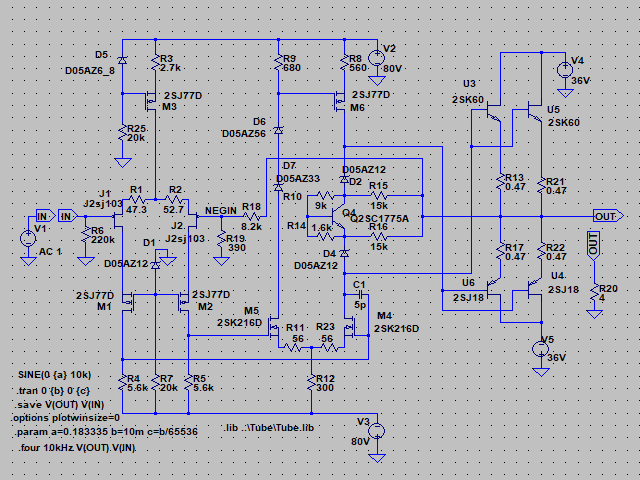

�E�P��Hz�ƂP�O��Hz�̐����g�Ō���ƁA�c���O�D�P���ȉ��łW�����ׂł͂U�S�v�A�S�����ׂł͂P�Q�W�v�̏o�͂�������悤���B���A�P�O�O��Hz�ł͂P�O��Hz�̂P�O�{�ȏ�̘c���ƂȂ��Ă���A�P���ȉ������e����W�����ׂłU�SW�A�S�����ׂłP�Q�WW�̏o�͂�������Ƃ������Ƃ���ł���B

�E�P�O�O��Hz�̃��[�v�Q�C����NFB�ʂ͂P�O��Hz�ȉ��̎��g�����T�˂Q�O��B�������A�����T��1/10�Ȃ̂ŁA�c�����T�˂P�O�{�ɂȂ�̂͗����Ȃ̂����A�P�O�{��������ƒ����Ă���̂͂��c�O�B

�E�Ƃ���ŁA��Ŋς��ʂ�A���̃A���v�͂S�����ׂłW�OW�ȏ�̏o�͂͂��������]�߂Ȃ��̂ŁA�����ł̂P�Q�OW�A�P�Q�WW�A�P�S�OW�A�P�U�OW�ł̌��ʂ̓t�F�C�N�ł���B

�E����ɁA�ǂ̓d�������艻���Ă����ł͂Ȃ��̂ŁA�o�͒i�p�d���͏o�͂ƂƂ��ɉ�����B�]���āA���@�̍ő�o�͂͂����Ə��������̂ɂȂ�B

�E���A�䂪�Ƃ̊��ł͏\�B

�E�p���[IVC���쎞�����ʂ͂قړ������낤����A����͏ȗ��B

|

|

�E�ł́A���̃t�F�C�N�ł����ʂ�������̂��H

�E����́A����SPICE���f�����A�Q�[�g�d�ʂ��\�[�X�d�ʂɑ��ď��o�C�A�X�ɂȂ����ꍇ���E�̂悤�ɂ���Ȃ�̌��ʂ������郂�f�����O�ɂȂ��Ă��邽�߂ł���B

�E���ۂ�V-FET�i�r�h�s�j�́A���o�C�A�X�̈�ł̓g�����W�X�^�I����ƂȂ�A���̓C���s�[�_���X�͋}���ɉ�����A�Q�[�g�d�����������̂ɂȂ�悤���B���ꂪ�����鎑���������B�E��̐}�̒ʂ�A���o�C�A�X�̈�ł̓Q�[�g�d�������Ȃ藬��ăh���C���d���𗬂����̂ɂȂ�B

�E����ł��A���o�C�A�X�̈�́A����̉�H�ł͑O�i�̓d�������\�͂��炵�Ďg���Ȃ��B

�E���f�����Ή����Ă��Ȃ����A��H������ɑΉ����Ă��Ȃ��̂ŁA�Q�[�g�d���𗬂��ď��o�C�A�X����Ŏg���z��͕s�B���ەs�\�B

|

|

| �@�@ |

�@�@�@ |

�E�ƁA�V�~�����[�V�������Ă��邤���ɐV����o���オ���Ă����B

|

|

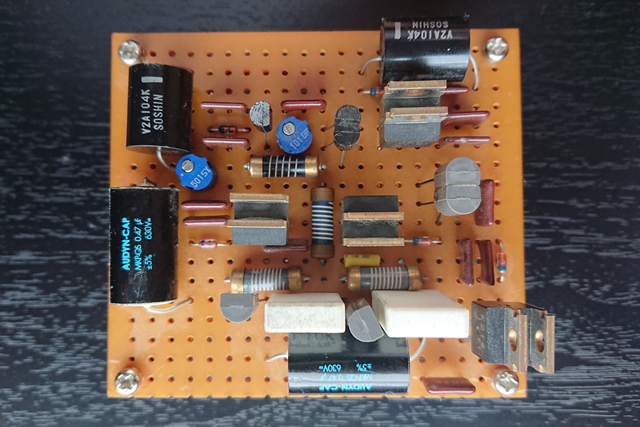

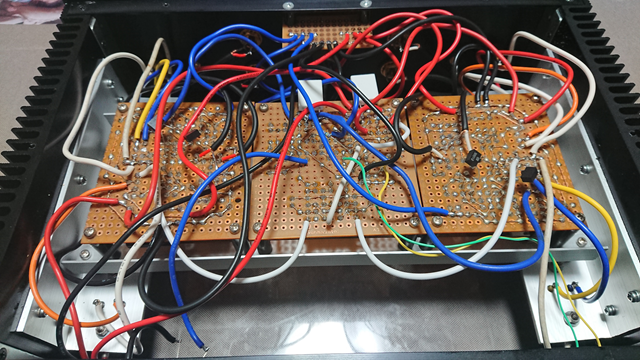

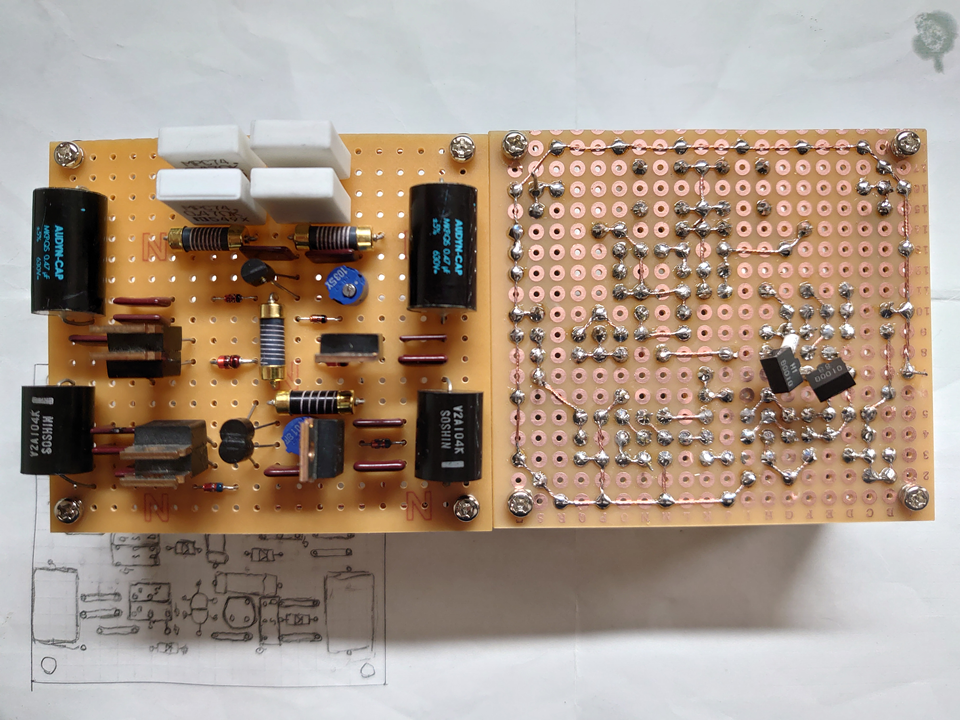

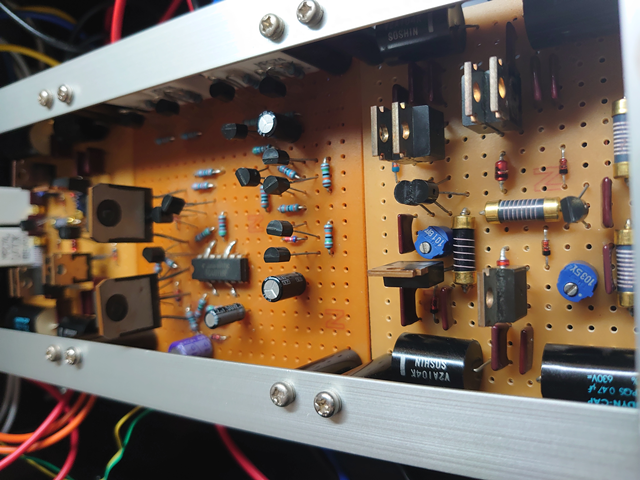

�E��H�͂����B

�E�A���v���̓V�~�����[�V�����̒ʂ�B

�E���A�I�i�̃o�C�A�X��H�̃c�F�i�[�_�C�I�[�h���P�QV�ł͏I�i�̃A�C�h�����O�d�����\���葽������邽�߁A�P�SV���PN�T�Q�S�SB�ɂ����B

�E�Q�r�i�P�W�ƂQ�r�j�U�O�̌����́A���f�������A���������O�a�d���͒Ⴍ�A�J�b�g�I�t�d���͍������̂̂悤�B

|

|

�E�d�����͏��v�̒萔�ύX�B

�E�܂��A���̍ۂȂ̂ŁA�d���X�C�b�`��NKK��S-1A����S-�R�R�QJ�ɕς��A�X�C�b�`�I�t���o�͒i�p�d���d���R���f���T�[�̓d�ׂ�f���������悤�ɂ����B

�E�O�i�p�́}�W�OV�d���ɂ��Ă��A�u���[�_��R��t���A�d���I�t����d���R���f���T�[�̓d�ׂ�����Ȃ�̊Ԃɔ����悤�ɂ����B

�@ |

|

|

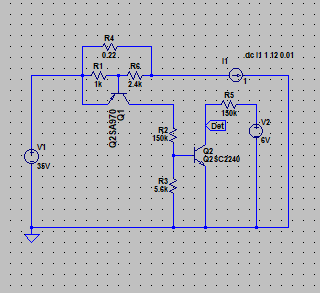

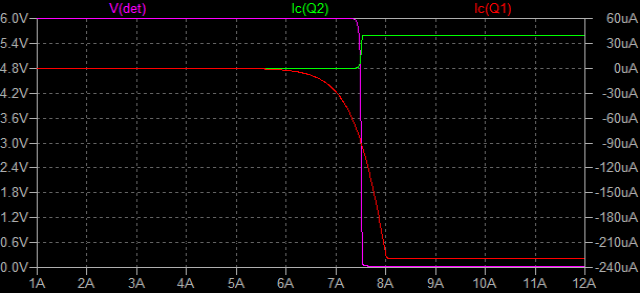

|

�E�d��������H�́A�V�D�TA���x�ŃV���b�g�_�E������悤�ݒ�B

�E�Ó�������A�S�����ׂł��W�OW���o�͌��E�Ȃ̂ŁA�d���𗬂���悤�ݒ肷��Ӗ��͂Ȃ��B�̂ŁA�f�q�̈��S�̂��߂ɂ���߂ɐݒ�B

|

|

|

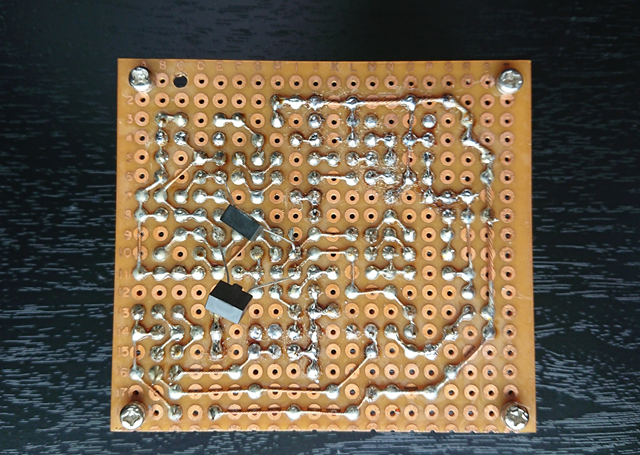

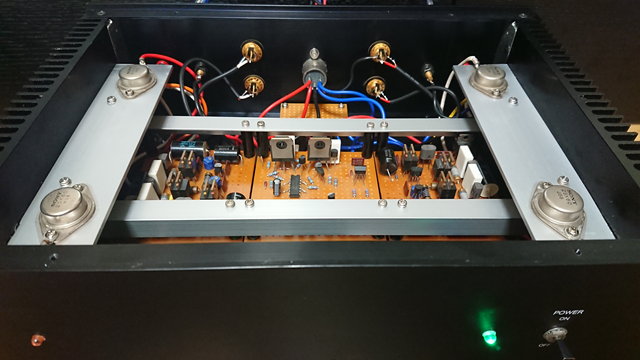

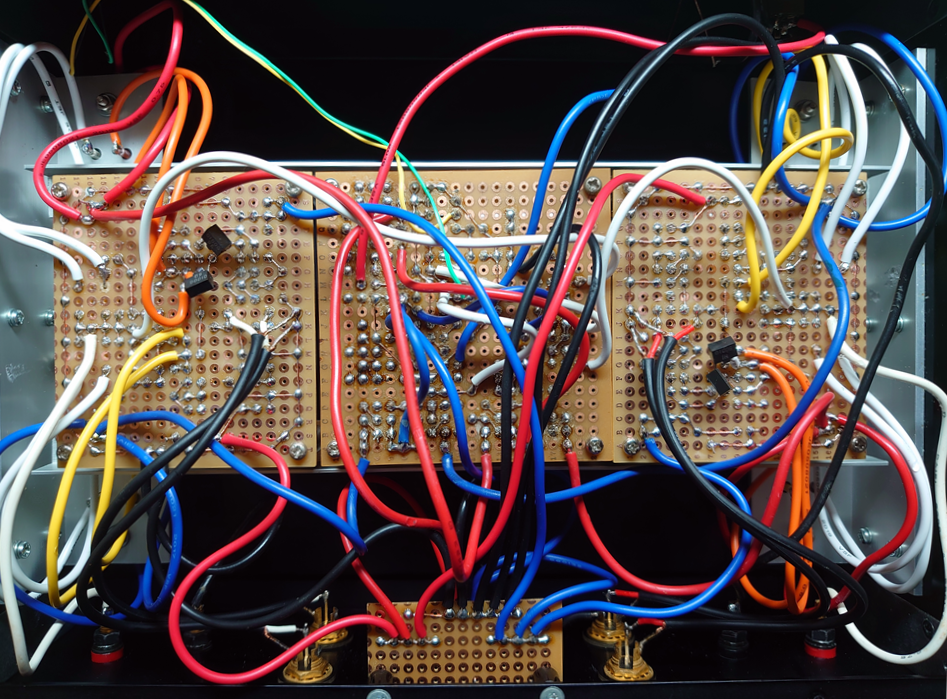

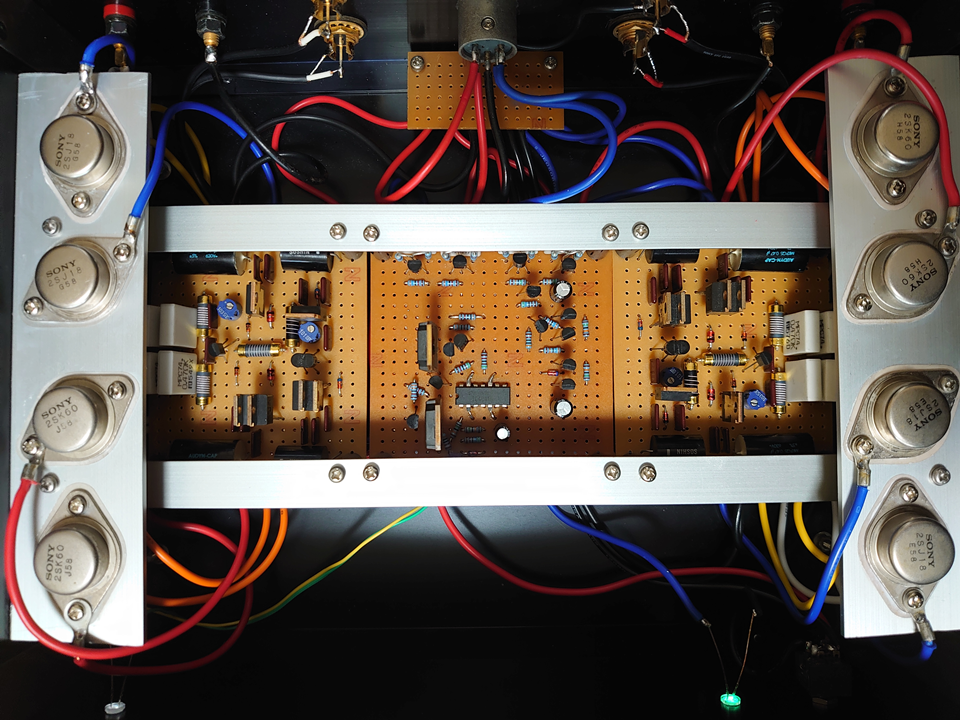

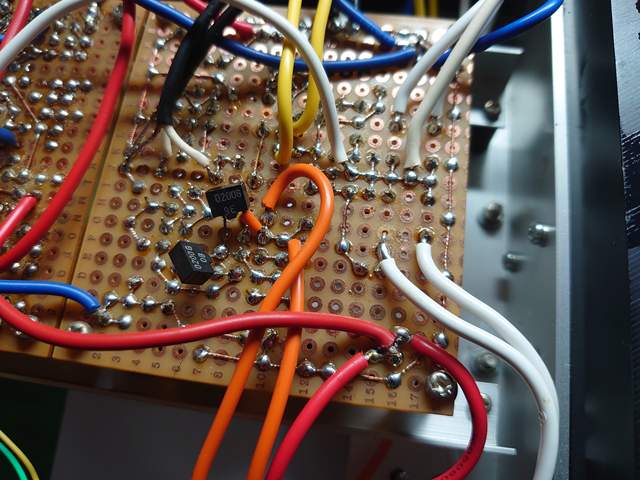

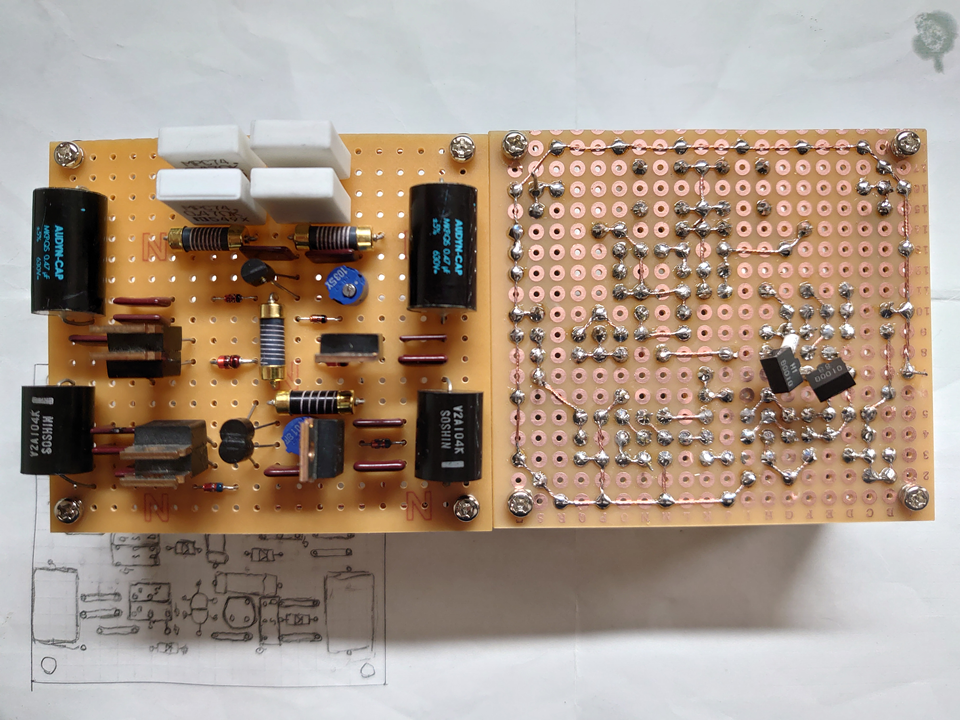

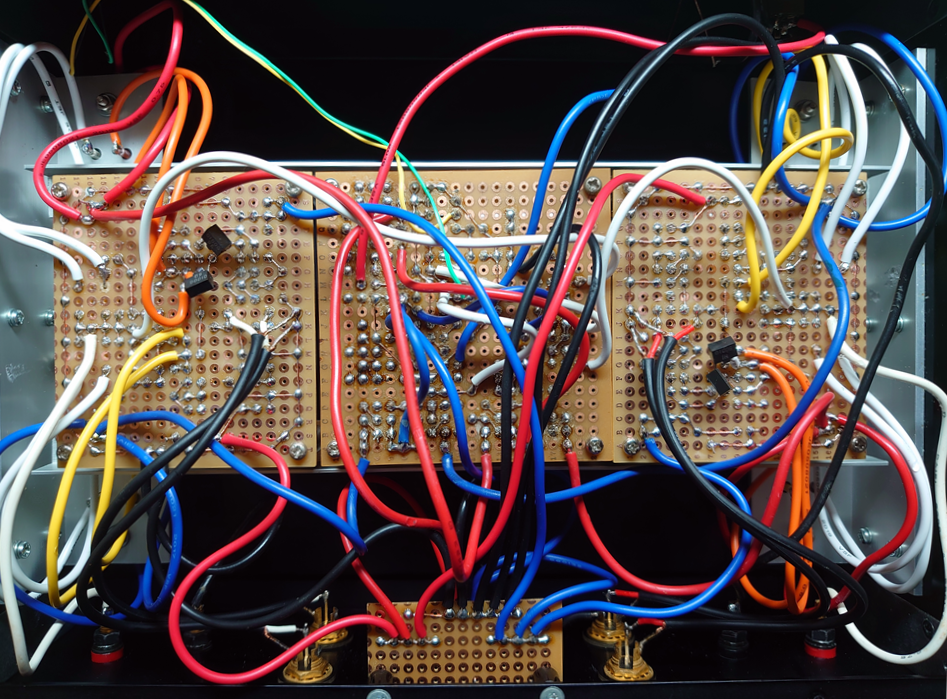

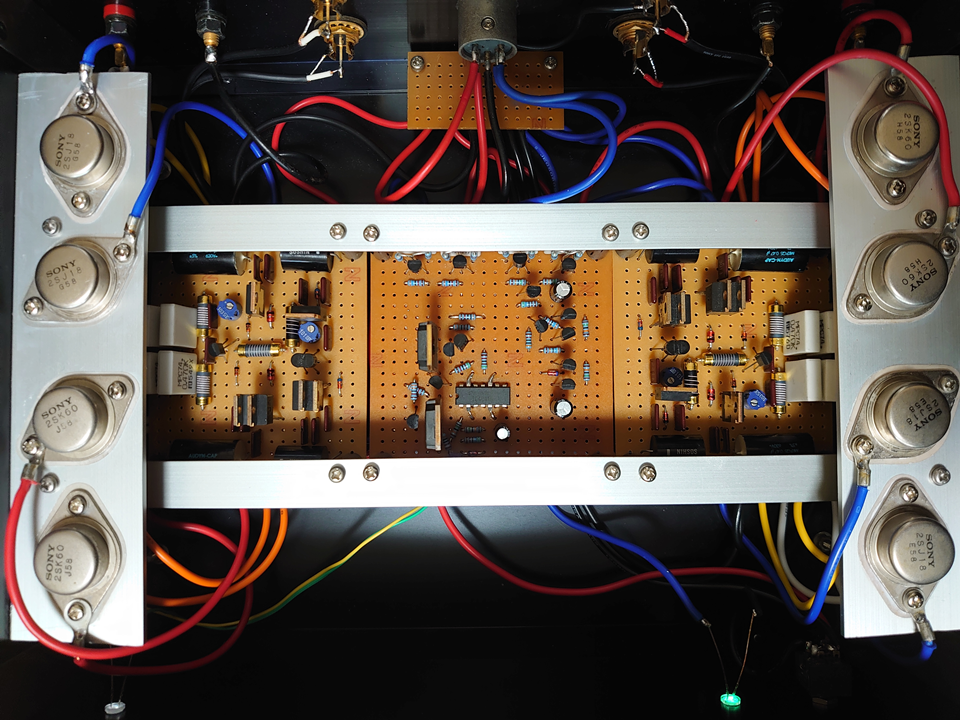

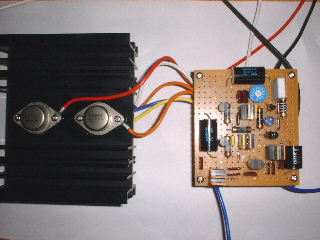

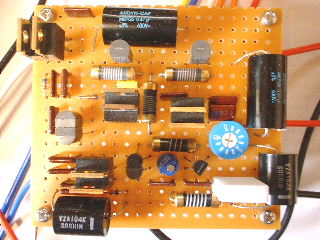

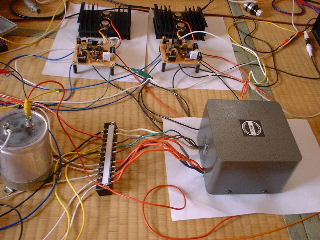

�E�A���v���́AV-FET�iSIT�j����M��ɑ��݂��A�O�����P�[�X���ēx�g�݁A���Ԃ��ĐV������t���A���v�̒��������Ȃ���z����Ƃ�����A�o���オ��B

�E�Q�r�i�P�W�ƂQ�r�j�U�O�̓d�ɔz�u�������B�d�ɒ[�q�����猩���}�Ȃ̂Ō��Ȃ��悤�B

|

|

| �@�@ |

�@�@ |

�E�������o���B

|

|

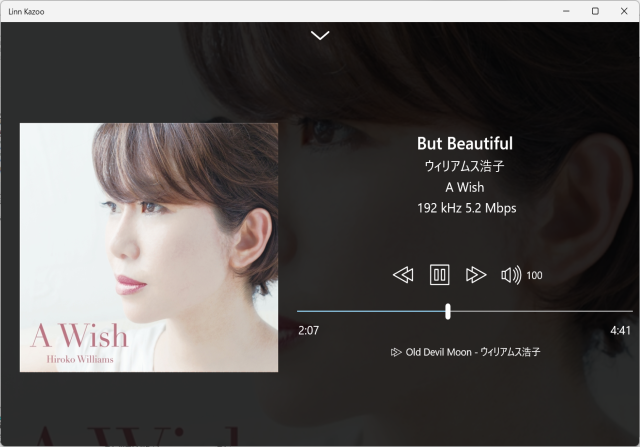

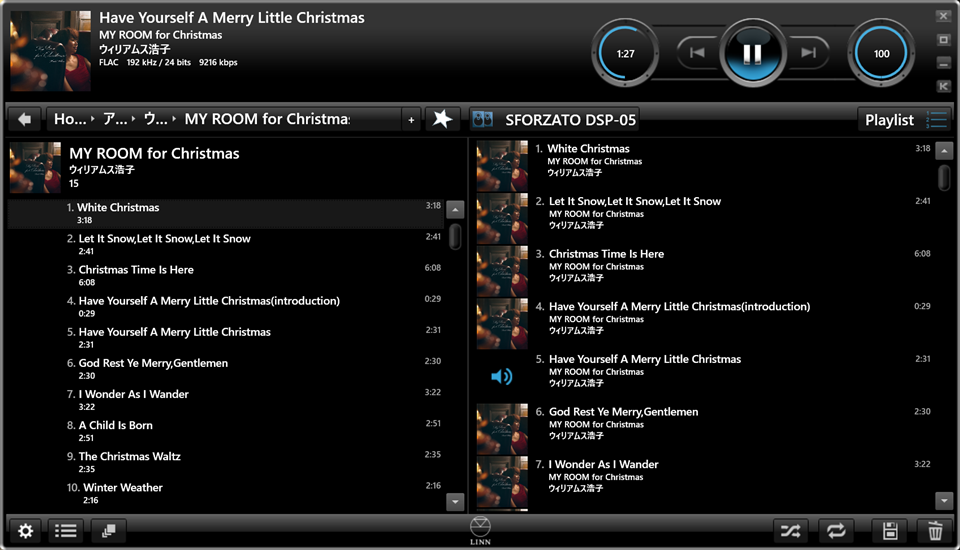

�E�E�B���A���X�_�q�B

�E���̐l�̍�i�͉����ǂ��B

�E����āX�������Q�r�i�P�W�|�Q�r�j�U�O�s���S�Ώ̌^�p���[�A���v���p���[�h�u�b�B���Ғʂ�̏���鉹�B

|

|

|

�E�̂̃A�C�h���B

�E�����������B

�E�f�r���[�R�T���N�L�O�B

�E�Z���t�J�o�[�B

�E���t�A�^���ǂ��B

�E�ς��ʐ��ŁA�ő����w�̂悤�ȏ�B�ǂ��B

|

|

�E�����啪�ɂȂ邪�ANHK�ŗL���ɂȂ��ėǂ������B

�E�������炐���܂ŁB���݂�B

|

|

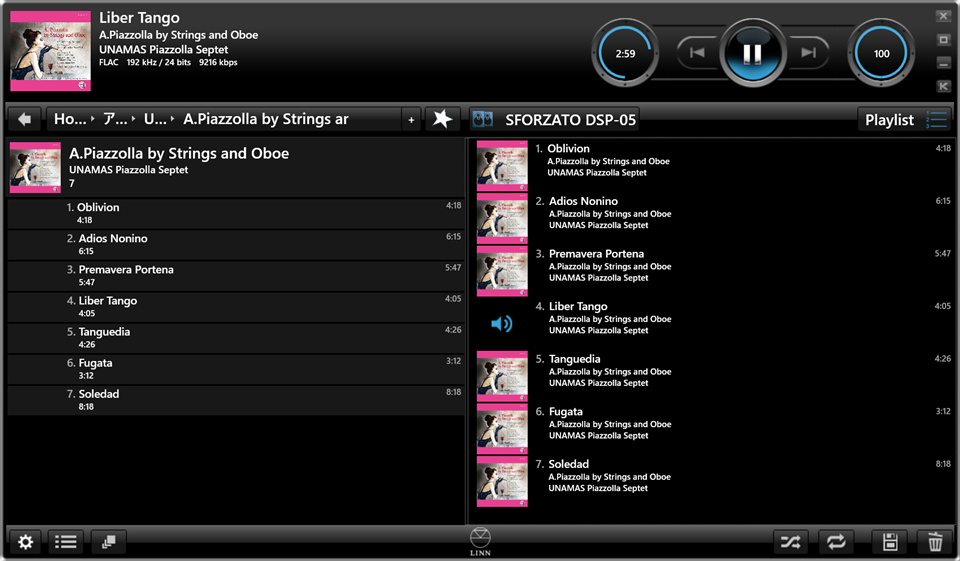

�E�������̘^����@�Ŏ��������ō��̉����A�Ƃ���UNAMASU�B

�E�R�Ȃ��B

|

|

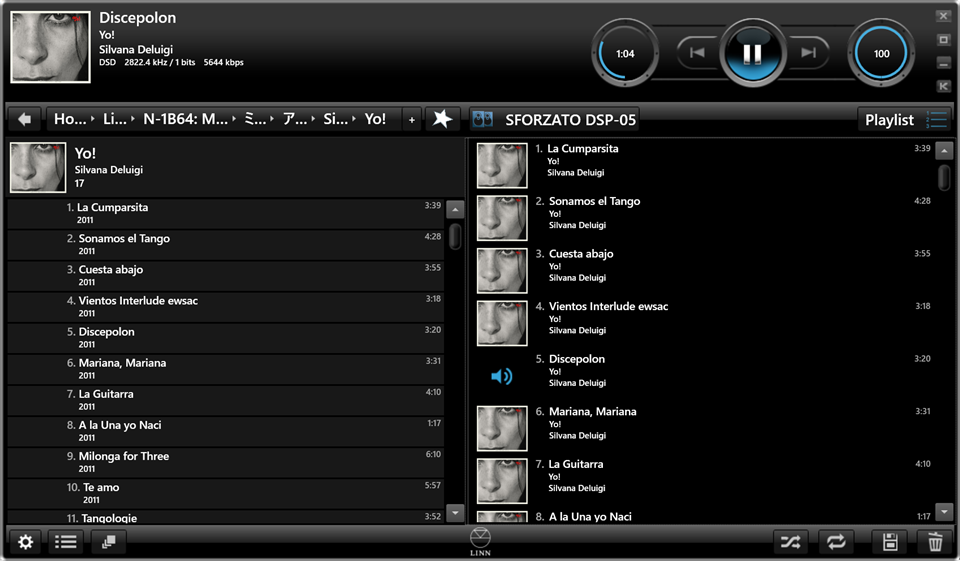

�E�m��Ȃ��l�����B

�E�f���炵���B

|

|

�E�䓛���ލ]�B

�E�f���炵���B

|

|

| �@ |

�E�āX�������Q�r�i�P�W�|�Q�r�j�U�O�s���S�Ώ̌^�p���[�A���v���p���[�h�u�b�B

�E�o�͂�DC�I�t�Z�b�g���}�P�T�O��V���x�ɂ��B����͍̂��ЂƂł���B�Q�i�ڍ����A���v�̔��M������Ȃ�ɂ��邹�����ȁB�J�X�R�[�h�A���v��t���đ������ςˁA�����A���v���̂����M�����点�Ή��P���邩���m��Ȃ��B

�E���A���̃V���v���ȉ�H�ōs���B�䂪�Ƃ̊��ł͂��̒��x�̃I�t�Z�b�g�͖��Ȃ��B

�E�ő���ɓ���Ȃ��u�|�e�d�s�i�r�h�s�j�B���̑t�ł鉹�͊��Ғʂ�B

�E������B

|

|

.jpg)

���̂u�|�e�d�s�͂��������I�[�f�B�I�p�r�łW���X�s�[�J�[���쓮����A���v�ɗp���邱�Ƃ�O��ɐv���ꂽ�悤�ŁA�Y�ޕK�v���Ȃ��y�ɒ����A���v����邱�Ƃ��o���܂��B

���̂u�|�e�d�s�͂��������I�[�f�B�I�p�r�łW���X�s�[�J�[���쓮����A���v�ɗp���邱�Ƃ�O��ɐv���ꂽ�悤�ŁA�Y�ޕK�v���Ȃ��y�ɒ����A���v����邱�Ƃ��o���܂��B.jpg)

�܂��A���R�ł��B

�܂��A���R�ł��B

���A�d���I�����̃|�b�v�m�C�Y�ɂ��ẮA���̂悤�ɂS�d���ɂ��Ă������Ȃ��̂ł����B�c�O�i�O�O�G

���A�d���I�����̃|�b�v�m�C�Y�ɂ��ẮA���̂悤�ɂS�d���ɂ��Ă������Ȃ��̂ł����B�c�O�i�O�O�G

�ǂ������P�[�X�ɂǂ��z�u���邩�\�z���܂��傤�E�E�E�A�Ȃ�Ėܘ_���܂��肽���Ȃ��P�[�X���H����ɂ��邽�߂̌�����ŁA���͍ŏ�����^�J�`�̂n�r�S�X�|�Q�U�|�R�R�a�w�ɗ�̔@�����߂悤�E�E�E�Ǝv���Ă����̂ł����B�i�O�O�G

�ǂ������P�[�X�ɂǂ��z�u���邩�\�z���܂��傤�E�E�E�A�Ȃ�Ėܘ_���܂��肽���Ȃ��P�[�X���H����ɂ��邽�߂̌�����ŁA���͍ŏ�����^�J�`�̂n�r�S�X�|�Q�U�|�R�R�a�w�ɗ�̔@�����߂悤�E�E�E�Ǝv���Ă����̂ł����B�i�O�O�G ����ł��A��₵�炭���āE�E�E

����ł��A��₵�炭���āE�E�E �Q�m�T�S�U�T�̃h���C���|�Q�[�g�Ԃ��V���[�g���[�h�Ŕj���������߁A���i�i�P�O�R�ɂh�������̌��E�d��������A���̂������i���ג�R�T�D�U�j����Q�i�ڍ����A���v�̋��ʃ\�[�X��R�̗��[�d�����Q�i�ڍ����A���v�̃J�X�R�[�h�p�c�F�i�|�O�T�y�P�W�w�̓d�����Ă��܂��A���ʂQ�i�ڂ̓d���o�����X�����S�ɕ���Ăh�u�ϊ���R�ɑS���o�C�A�X�d�����������Ȃ��Ȃ����Ƃ����̂��A����̌̏�̓��e�ł����B�ł�����I�i�Q�r�j�U�O�ɑ�d���������͓̂�����O�ŁA�����Q�T�u�d�����C���Ƀq���[�Y�����Ă��Ȃ������Ȃ�Ίm���ɂQ�r�j�U�O�͏��V���Ă����Ƃ���ł����E�E�E�B

�Q�m�T�S�U�T�̃h���C���|�Q�[�g�Ԃ��V���[�g���[�h�Ŕj���������߁A���i�i�P�O�R�ɂh�������̌��E�d��������A���̂������i���ג�R�T�D�U�j����Q�i�ڍ����A���v�̋��ʃ\�[�X��R�̗��[�d�����Q�i�ڍ����A���v�̃J�X�R�[�h�p�c�F�i�|�O�T�y�P�W�w�̓d�����Ă��܂��A���ʂQ�i�ڂ̓d���o�����X�����S�ɕ���Ăh�u�ϊ���R�ɑS���o�C�A�X�d�����������Ȃ��Ȃ����Ƃ����̂��A����̌̏�̓��e�ł����B�ł�����I�i�Q�r�j�U�O�ɑ�d���������͓̂�����O�ŁA�����Q�T�u�d�����C���Ƀq���[�Y�����Ă��Ȃ������Ȃ�Ίm���ɂQ�r�j�U�O�͏��V���Ă����Ƃ���ł����E�E�E�B ���A�A���߂��ĔM���Y���A�Ɛ\���܂��傤���i�O�O�G

���A�A���߂��ĔM���Y���A�Ɛ\���܂��傤���i�O�O�G