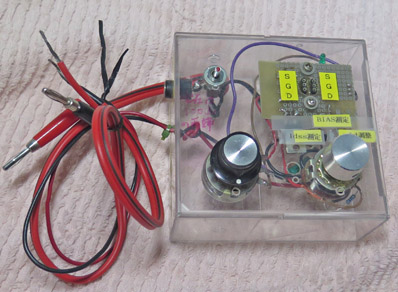

2011年に作った初代のFET checkerです。ぺるけさんの記事に準じています。 2011年に作った初代のFET checkerです。ぺるけさんの記事に準じています。

後日電源やDMMに接続するcableを追加しました。

Floppy diskのcaseに入れたのが間違いで、DUTの挿抜の際にcaseがたわむ感覚が指先に伝わり、気持ちよく測定できませんでした。 |

|

1. FET測定部 |

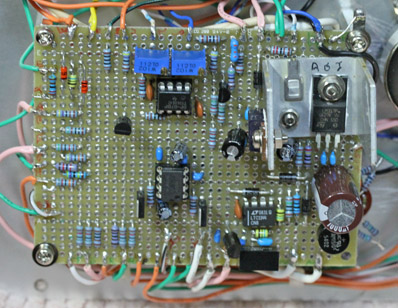

基本的な回路構成はぺるけさんのsiteに丁寧な解説がありますから、変更点だけ記述します。定電流回路をOp ampで構成しましたが、本職で初めてのヒット商品に活用した思い出深い回路です。ID(Drain current)の可変機能も組み込みました。R12はOp ampの入力端子がswitchの接触不良などで宙に浮いてしまわないための用心。類似の箇所がTransistor側にもありますが、そちらは未処置です。制御素子をMOS-FETにすればTransistor側と揃うのですが、回路を検討した時期の違いでbipolarになっています。

まるで設計者が異なるようだと自嘲気味。

基準電圧をZener diodeでなくVoltage reference ICで構成したのは在庫の消化が主目的です。

Stand aloneで使えるようにDPM(Digital panel meter)を内蔵しています。FETの印加電圧をoffしたいことが初代であったので、基準電圧回路などは通電したままFETだけoffにできるswitchを設けました。 |

|

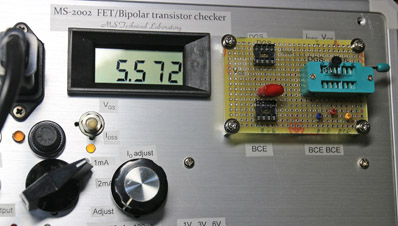

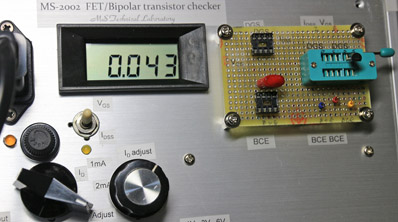

左はIDSSを測定中。DPMの小数点の桁を工夫することで、mA単位で電流値を直読できます。

印加電圧を10Vに近づけるためのLEDがswitchの下に顔を出しています。

黄色LEDの順方向電圧降下が約2Vだったので採用。

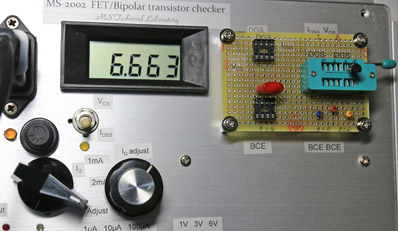

左下は、IDの可変機能を使って6.663mAに設定。

右下は、そのときのVGSを直読。IDとVGSの測定ではDPMのfull scale設定を一桁ずらしています。 |

|

|

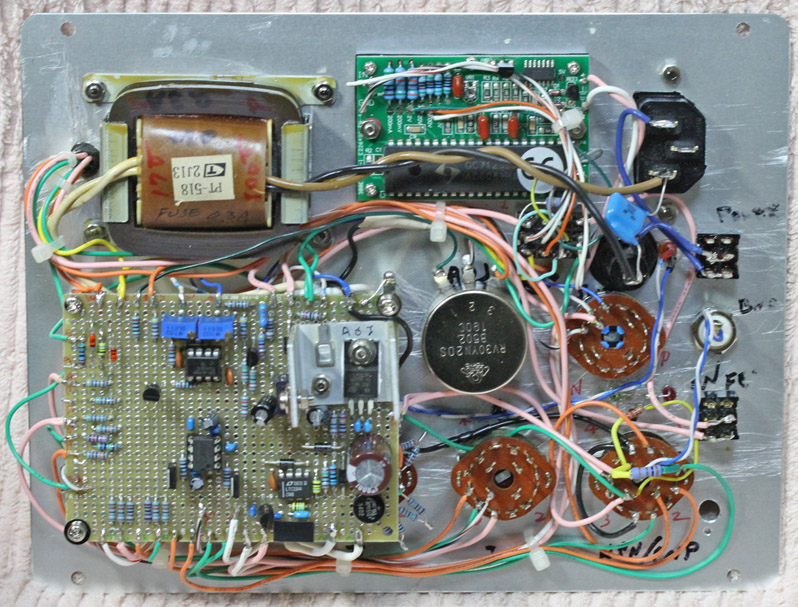

Panelの右半分に空き地が目立ち、その分左側が混雑しています。制御回路の基板とswitch類がなるべく重ならないように配置したのと、DUTの挿抜の邪魔にならないように周辺を空き地にした事情からです。

DUTのtest fixtureは上半分がFET、下半分がTransistorです。たまたま電源トランスと基板の固定寸法がほぼ同じだったので、トランス側の穴を少し削って共締めしました。 |

|

2. Transistor測定部 |

原回路に倣ってNPN/PNP切換を設けたので、大変複雑な構成になりました。VCE電圧切換部に誤配線が一カ所見つかりましたが、この程度ですんで助かりました。

原回路と大きく異なるのは、駆動電圧を供給する回路をOp ampとMOS-FETで構成したことです。ぺるけさんが解説されている通り、Bipolar transistorで駆動するとbase電流がDUTにも流れますが、MOS-FETはそれがなく100Ωの両端電圧がそのままDUTに流れる電流に対応します。ここにOp

ampを持ち出すのなら、FETの方もOp ampでとなったいきさつがあります。

Base電流を供給する回路の電圧が原回路より高いのは、手許にあった低めの電圧のZener diodeが順方向も逆方向と同じくらいの電圧降下を示したからです。順方向電圧の低いのを探して今の素子に行きつきました。10倍ずつ違うbase電流の設定は、抵抗2本の組合せで追い込みました。

この測定器は構想し始めてから1年以上経過しています。何度も回路を変更し、この方式に収束しました。どうせなら、base電流供給部にもOp ampを使うかなどと迷っているうちに、これではいつまでも完成にこぎつけられないと気づき、潔く原回路に従いました。 |

|

|

|

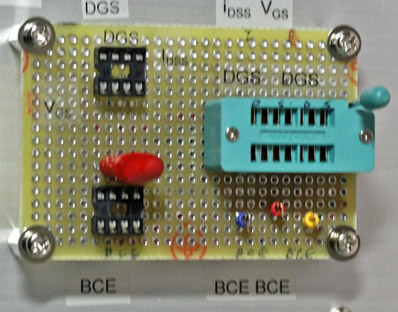

Transistorの形状はさまざまなので、clip cordsも使えるようにtest端子を各電極分実装しています。

これは、測定中にVCEやVBEを測ってみたいなどの場面で便利なことがわかりました。

FET用のDPMをこちらでも使おうとすると、何段ものrange切換が必要なので、あっさり外付けのDMMに逃げました。

ここでは表示部を一緒に撮影するために小型のDMMを置いていますが、desktopのDMMが本来の接続先になります。 |

3. 電源などの共通部 |

|

|

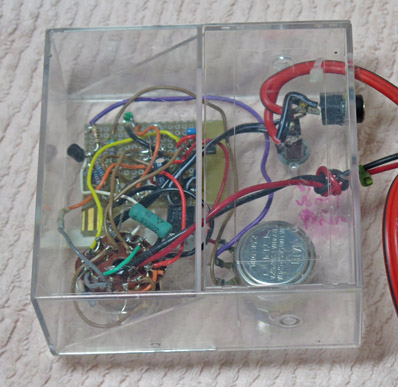

電源トランスはもらいものの機器から取り外した薄型。FET用の+12VとTransistor用の+15V(基準電圧をここから分圧して作るため精密に電圧を追い込み)を作っています。

+15VからVoltage converter ICで-15Vを生成。これはOp ampの電源用です。

+15Vから絶縁型のDC-DC converterで他とは縁の切れた15Vを生成し、3端子regulatorで9Vに落としてDPMの電源としました。R1はDC-DC

converterの出力電流が最低6mAとなっているためのbleederです。

ずいぶん面倒な工作になりましたが、部品はほとんど手許にあったもので、新規調達した半導体はMOS-FETだけでした。

Caseは,10年以上棚に眠っていたTakachiのFC8-25-20-GSでpanelにすべての部品を実装しました。他の部材はpanelを囲っているだけです。

|

| 左下の遊んでいる穴は加工ミスではなく、将来何か機能を追加したくなった場合に備えたつもりです。 |

![]()