儊僈儘儉僐儞僩儘乕儔乕偺旈枾

丂儊僈儘儉僐儞僩儘乕儔乕偼儊儌儕儅僢僷僐儞僩儘乕儔乕偲偟偰巊偊傞偲偄偆塡偁傝丅

丂儊僈儘儉僐儞僩儘乕儔乕傕儊儌儕儅僢僷傕64kB傛傝戝偒偄儊儌儕傪堦掕偺戝偒偝偺僶儞僋偵暘妱偟丄柦椷偵傛偭偰CPU偐傜尒偊傞僶儞僋傪愗傝懼偊傞婡擻傪帩偭偰偄傑偡丅偟偐偟丄儊僈儘儉僐儞僩儘乕儔乕偼儊儌儕儅僢僾僪I/O偲偄偆摿掕偺傾僪儗僗偵僨乕僞傪彂偒崬傓偙偲偵傛偭偰儊儌儕偺僶儞僋傪愗傝懼偊傞偺偵懳偟丄堦曽偱儊儌儕儅僢僷偱偼I/O億乕僩傪巊偭偰僶儞僋傪愗傝懼偊傑偡丅儊僈儘儉僐儞僩儘乕儔乕偼儊僈儘儉僎乕儉偱傛偔巊傢傟偰偄傑偡偑丄儊儌儕儅僢僷偼愱梡偺僐儞僩儘乕儔偼懚嵼偣偢丄儘僕僢僋夞楬傪慻傒崌傢偣偰嶌傞偐丄MSX杮懱偺僔僗僥儉LSI偵婡擻偑娷傑傟偰偄傞偺偑堦斒揑偱偡丅

丂偦偙偱儊僈儘儉僐儞僩儘乕儔乕傪儊儌儕儅僢僷僐儞僩儘乕儔乕偲偟偰棙梡偟傛偆偲峫偊偨曽偑偍傜傟偨傛偆偱偡丅幚嵺偵峫埬偟偨偺偼帡旕怑恖岺朳偺偮偠偐傢偝傫偱偡偑丄kal偝傫偺僒僀僩偱夞楬恾偑岞奐偝傟偰偄傑偟偨乮偑丄暵嵔偝傟偰偟傑偄傑偟偨丒丒丒乯丅

丂偙傟偩偗偱偼傛偔暘偐傜側偄偺偱丄夝愅傪偟偰傒傞偲丒丒丒丅

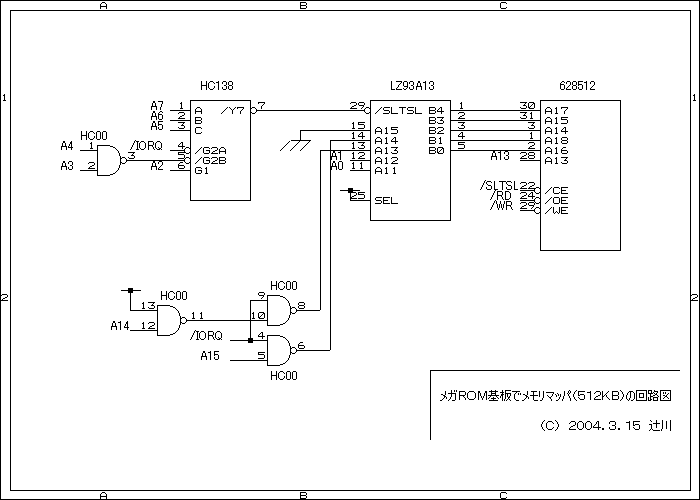

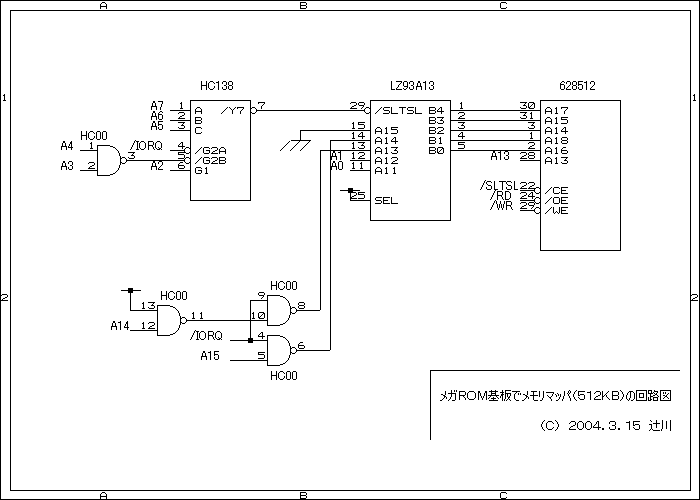

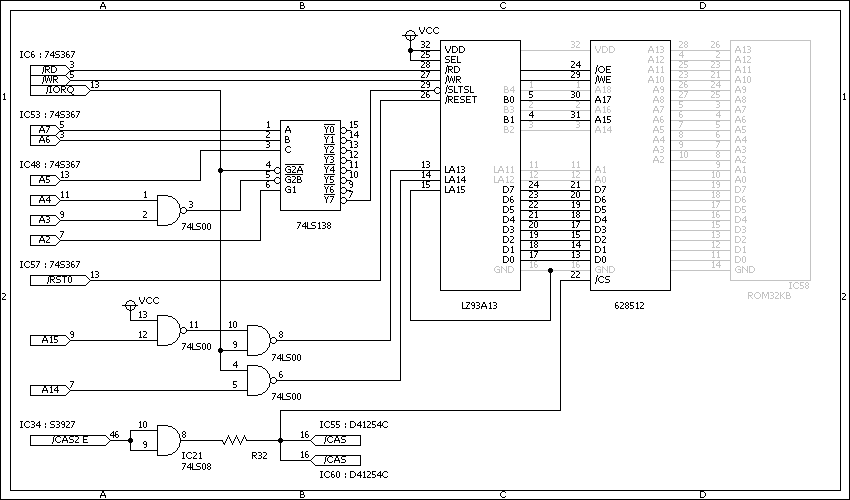

HC138偼儊僈儘儉僐儞僩儘乕儔乕乮LZ93A13乯偑傾僋僥傿僽偵側傞偨傔偺怣崋乮/SLTSL乯

傪嶌偭偰偄傑偡丅

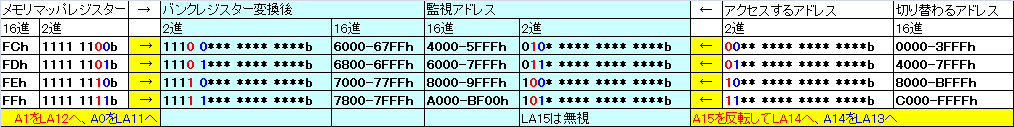

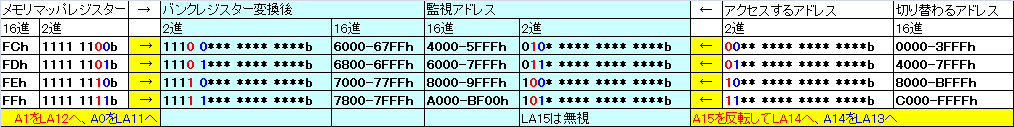

儊儌儕儅僢僷偱偼I/O億乕僩偺16恑昞婰偱FC乣FFh乮2恑昞婰偱1111 1100乣1111 1111b乯

偵抣傪彂偒崬傓偙偲偱懳墳偡傞儁乕僕偺僶儞僋傪愗傝懼偊傑偡丅

FCh丗儁乕僕侽乮0000-3FFFh丗00** **** **** ****b乯

FDh丗儁乕僕侾乮4000-7FFFh丗01** **** **** ****b乯

FEh丗儁乕僕俀乮8000-BFFFh丗10** **** **** ****b乯

FFh丗儁乕僕俁乮C000-FFFFh丗11** **** **** ****b乯

HC138偺弌椡/Y7偼I/O億乕僩傊偺傾僋僙僗傪堄枴偡傞/IORQ偑Low偱丄A7乣A2偑High偺帪丄

偡側傢偪FC乣FFh偺帪偵Low偲側傝傑偡丅

LZ93A13偺懠偺擖椡LA15乣LA11乮怣崋柤偑摨偠偱傗傗偙偟偄偺偱丄偲傝偁偊偢摢偵L傪

晅偗傑偟偨乯偼偳偆側偭偰偄傞偐尒偰傒傞偲丄LA15偼Low偱屌掕丅LA14偲LA13偼A15偲

A14偐傜嶌傜傟偰偄傑偡丅LA12偲LA11偼A1偲A0偑擖偭偰偄傑偡丅偙傟傪撉傒夝偔偲丄

/IORQ偑Low偺帪偼LA14偲LA13偼A15偲A14偲偼娭學側偔High偵側傝傑偡丅

偮傑傝丄LZ93A13偐傜傒偨傾僪儗僗偼

011(A1) (A0)*** **** ****b

(A1)偲(A0)偼忋偵彂偄偨儊儌儕儅僢僷偱偳偺儁乕僕傪慖傇偐傪慖戰偡傞bit乮FC乣FFh

偺C乣F傪寛掕偡傞嵟屻偺2bit乯偱偡丅

偮傑傝/IORQ偑Low偺帪偵A1偲A0偺慻傒崌傢偣偵傛偭偰

0110 0*** **** ****b = 6000-67FFh

0110 1*** **** ****b = 6800-6FFFh

0111 0*** **** ****b = 7000-77FFh

0111 1*** **** ****b = 7800-7FFFh

偵曄姺偝傟傞偙偲偵側傝傑偡丅

LZ93A13偺SEL怣崋偑High偱偡偺偱丄儊僈儘儉僐儞僩儘乕儔乕偼8k儌乕僪偲側傝丄僶儞僋

儗僕僗僞乕偺摥偒偼埲壓偺傛偆偵側傝傑偡丅

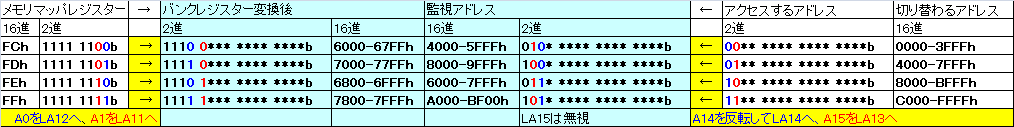

僶儞僋愗傝懼偊8kB儌乕僪帪

僶儞僋儗僕僗僞乕偺傾僪儗僗 愗傝懼傢傞傾僪儗僗

6000-67FFh 4000-5FFFh

6800-6FFFh 6000-7FFFh

7000-77FFh 8000-9FFFh

7800-7FFFh A000-BFFFh

偮傑傝丄IO億乕僩傊偺傾僋僙僗偑僶儞僋儗僕僗僞乕偺傾僋僙僗偵曄姺偝傟傞偙偲偵側傝

傑偡丅

塻偄恖偼偍婥偯偒偐偲巚偄傑偡偑丄儊儌儕儅僢僷偼0000h乣FFFFh(64kB)傪4暘妱偟偨

16kB枅偵愗傝懼偊傑偡偑丄儊僈儘儉僐儞僩儘乕儔偼4000h乣BFFFh(32kB)傪4暘妱偟偨

8kB扨埵偱愗傝懼偊傑偡丅儊僈儘儉僐儞僩儘乕儔乕偼16kB偱愗傝懼偊傞儌乕僪傕帩偭

偰偄傑偡偑丄愗傝懼偊傜傟傞傾僪儗僗偼4000乣BFFFh傪俀暘妱偡傞偩偗偱僶儞僋儗僕

僗僞乕傕2屄偵側偭偰偟傑偆偺偱崱夞偼巊偊傑偣傫丅偲傝偁偊偢僶儞僋儗僕僗僞乕偑

4屄偁傞偲偄偆偙偲偑偙偙偱偼廳梫側偺偱偡丅偱偼丄4000h乣BFFFh偱偟偐愗傝懼偊傜

傟側偄偺偵儊儌儕儅僢僷偲偟偰偳偆巊偭偰偄傞偺偐丄偲偄偆偙偲偵側傝傑偡丅

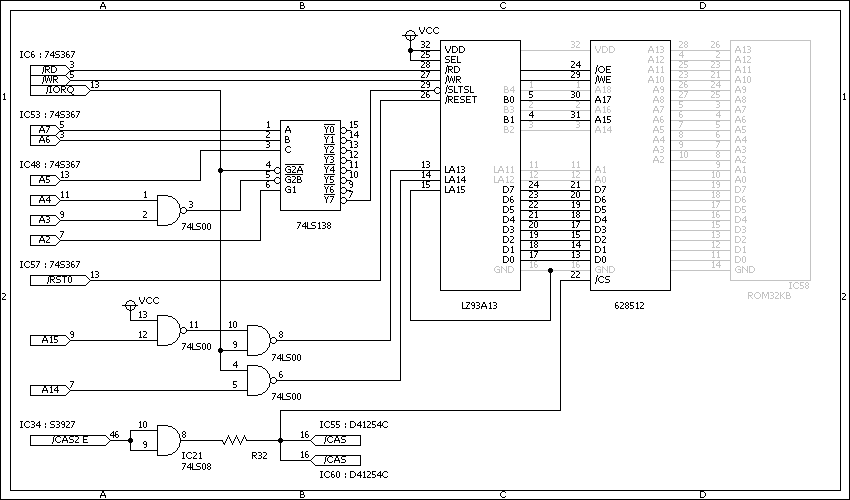

628512傪尒偰傒傞偲丄A13乮A0乣A13乯偼僗儘僢僩偐傜偺怣崋傪偦偺傑傑巊偭偰偄傑偡丅

偮傑傝16kB埲壓偺晹暘偼儊僈儘儉僐儞僩儘乕儔乕偵棅偭偰偄側偄偺偱儊僈儘儉僐儞僩

儘乕儔偐傜偺怣崋偱愗傝懼偊傜傟傞偺偼16kB扨埵偲偄偆偙偲偵側傝傑偡丅

儊僈儘儉僐儞僩儘乕儔乕偼弌椡B6-B0偱僶儞僋偺斣崋傪巜掕偟偰偄傑偡偑丄乽4屄偺

僶儞僋儗僕僗僞乕偼壗傪尦偵弌椡傪寛傔偰偄傞偐乿偲偄偆帠偵側傝傑偡丅傕偪傠傫丄

僶儞僋儗僕僗僞乕枅偵巜掕偟偨抣偼偁傞偺偱偡偑丄B6-B0偼忢偵摨偠抣傪弌偡傢偗

偱偼偁傝傑偣傫丅4000h傊偺傾僋僙僗側傜僶儞僋斣崋xx傪丄8000h傊偺傾僋僙僗側傜

僶儞僋斣崋yy傪丄偲偄偆傛偆偵傾僋僙僗偝傟偰偄傞傾僪儗僗偵傛偭偰僶儞僋傪愗傝

懼偊側偗傟偽側傝傑偣傫丅忋婰偺愗傝懼傢傞傾僪儗僗傪2恑昞婰偱峫偊偰傒傞偲

4000-5FFFh = 010* **** **** ****b

6000-7FFFh = 011* **** **** ****b

8000-9FFFh = 100* **** **** ****b

A000-BFFFh = 101* **** **** ****b

偮傑傝LA15乣LA13偑暘偐傟偽懳墳偡傞僶儞僋斣崋傪弌椡偱偒傞偙偲偵側傝傑偡丅

偙偙偱LA15偲LA14偼恀媡偺抣偱偡偺偱儘僕僇儖偵偼LA15偲LA13傕偟偔偼LA14偲

LA13偑暘偐傟偽懳墳偡傞僶儞僋斣崋傪弌椡偱偒傑偡丅傕偪傠傫幚嵺偵偳偺怣崋

傪尦偵弌椡偟偰偄傞偐偼儊僈儘儉僐儞僩儘乕儔乕撪晹偺榖偱偡丅

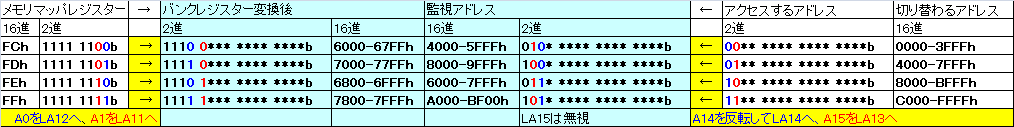

偙偙偱夞楬恾傪尒偰傒傞偲丄LA15偼Low屌掕丄捠忢偺儊儌儕傾僋僙僗帪偼/IORQ

偑High側偺偱LA14偼A15偺斀揮偟偨抣丄LA13偼A14偵側傝傑偡丅LA12偲LA11偼僶

儞僋斣崋傪弌椡偡傞嵺偵偼柍娭學偺怣崋偱偡丅LA15偑忢偵Low偲偄偆偙偲偼丄

僶儞僋斣崋偼LA14偲LA13傪尦偵寛傑傞偙偲傪慜採偵愝寁偝傟偰偄傞傛偆偱偡丅

LA14偲LA13偼幚嵺偵偼A15偺斀揮偲A14偑擖偭偰偄傑偡偺偱丄埲壓偺條偵儊儌儕

儅僢僷偺16kB扨埵偱偺傾僋僙僗偵懳墳偟偰愗傝懼偊傞偙偲偵側傝傑偡丅

00** **** **** ****b = 0000-3FFFh

01** **** **** ****b = 4000-7FFFh

10** **** **** ****b = 8000-BFFFh

11** **** **** ****b = C000-FFFFh

僨乕僞偺棳傟傪傑偲傔傞偲偙傫側僀儊乕僕偱偡丅

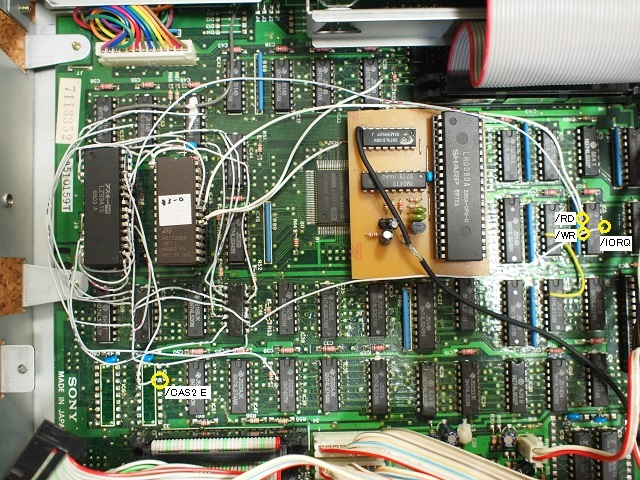

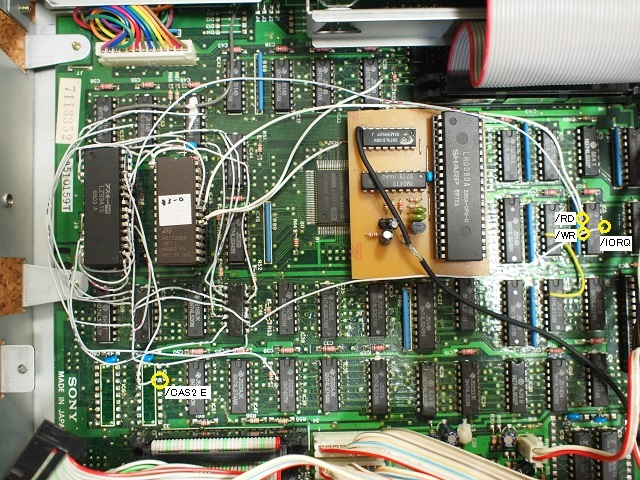

丂偱偼丄崱夞傕HB-F500傪巊偭偰摦嶌傪妋擣偟偰傒偨偄偲巚偄傑偡丅

丂HB-F500偼偙傟傑偱偺夵憿偵傛偭偰撪晹偵奼挘弌棃傞僗儘僢僩偑偁傝傑偣傫偺偱丄撪憼偡傞偨傔偵偼尦偐傜嵹偭偰偄傞DRAM偺戙傢傝嵹偣傞偟偐偁傝傑偣傫丅S3527偺僨乕僞僔乕僩傪尒傞偲丄DRAM偵棃偰偄傞/RAS偑/SLTSL偲傎傏摨偠僞僀儈儞僌偱Low偵側偭偰偄傑偟偨丅/RAS偑DRAM偺偁傞#3-2傪傾僋僙僗偡傞偲偒偵偺傒Low偵側傞偺側傜巊偊傞偐側偲巚偭偨偺偱偡偑丄寢壥偲偟偰懯栚偱偟偨丅偳偆傗傜DRAM傪傾僋僙僗偡傞丄偟側偄偵娭傢傜偢忢偵/SLTSL偲摨偠僞僀儈儞僌偱Low偵側偭偰偄傞傛偆偱偡丅幚憰偟偰偄傑偣傫偑丄#0偵傕16kB偺DRAM傪嵹偣傞偙偲偑偱偒傑偡丅偦偺DRAM傊偺傾僋僙僗帪傗DRAM偺儕僼儗僢僔儏偺僞僀儈儞僌偱傕Low偵側傞偺偱丄尦乆/SLTSL偲摨偠摦偒偱偼柍偄偺偱偡偑丅/RAS偑弌偰偄偰丄偐偮奺僗儘僢僩偺/SLTSL偑High乮偐偮#0偺DRAM傊偺/CAS偑High丄/RFSH偑High乯偺帪偵DRAM偺偁傞#3-2傊偺/SLTSL偲傒側偡儘僕僢僋傪慻傫偱傕椙偄偺偱偡偑柺搢側偺偱丄崱夞偼#3-2偺DRAM偵擖偭偰偄傞/CAS2 E傪巊偄傑偡丅嵟弶偐傜偦傟傪巊偊偽椙偐偭偨偺偱偡偑丒丒丒/CAS偑Low偵側傞偺偼/RAS偑Low偵側傞僞僀儈儞僌傛傝抶偄偺偱丄偪傚偭偲僞僀儈儞僌傪怱攝偟偰偄傑偟偨丅挷傋偰傒偨傜Z80偺僋儘僢僋偵斾傋偨傜SRAM偺摦嶌偼廫暘憗偔偰栤戣側偄傛偆偱偡丅

丂幚嵺偵偳偆幚憰偡傞偐偱偡偑丄慜夞偺夵憿偱IC49(32kB ROM)偺忋偵2抜ROM傪愊傫偱偟傑偭偨偺偱丄崱夞偼IC58(32kB ROM)偺忋偵SRAM(628512)偲儊僈儘儉僐儞僩儘乕儔乕(LZ93A13)傪愊傒忋偘傞偙偲偵偟傑偡丅奺IC偺僺儞偼埲壓偺捠傝偱偡丅

俁俀倠俛俼俷俵 俇俀俉俆侾俀 俴倅俋俁俙侾俁

+--_--+ +--_--+

A18|1 32|VDD B 4|1 32|VDD

+--_--+ A16|2 31|A15 B 3|2 31|B 5

VDD|1 28|VDD V14|3 30|A17 B 2|3 30|B 6

A12|2 27|A14 A12|4 29|/WE B 1|4 29|/SLTSL

A 7|3 26|A13 A 7|5 28|A13 B 0|5 28|/RD

A 6|4 25|A 8 A 6|6 27|A 8 /WE23|6 27|/WR

A 5|5 24|A 9 A 5|7 26|A 9 /OE23|7 26|/RESET

A 4|6 23|A11 A 4|8 25|A11 /OE01|8 25|SEL

A 3|7 22|/OE A 3|9 24|/OE /OE1|9 24|D 7

A 2|8 21|A10 A 2|10 23|A10 /OE0|10 23|D 6

A 1|9 20|/CS A 1|11 22|/CS A11|11 22|D 5

A 0|10 19|D 7 A 0|12 21|D 7 A12|12 21|D 4

D 0|11 18|D 6 D 0|13 20|D 6 A13|13 20|D 3

D 1|12 17|D 5 D 1|14 19|D 5 A14|14 19|D 2

D 2|13 16|D 4 D 2|15 18|D 4 A15|15 18|D 1

GND|14 15|D 3 GND|16 17|D 3 GND|16 17|D 0

+-----+ +-----+ +-----+

丂628512偺4乣21僺儞丄23僺儞丄25乣28僺儞偼偦偺傑傑32kB ROM偺2乣19僺儞丄21僺儞丄23乣26僺儞偵偮側偘傜傟傑偡丅

丂LZ93A13偼1乣3僺儞(B4乣B2)偼SRAM偺1乣3僺儞(A18,A16,A14)偵偮側偘傑偡丅傑偨丄11丄12僺儞(A11,A12)傕SRAM偺11丄12僺儞(A1,A0)偵偦偺傑傑偮側偘傜傑偡丅偦傟埲奜偼偒偪傫偲攝慄偡傞昁梫偑偁傝傑偡丅僺儞偺壛岺偼埲壓偺捠傝丅

俁俀倠俛俼俷俵 俇俀俉俆侾俀 俴倅俋俁俙侾俁

+--_--+ +--_--+

忋|1 32|忋 壓|1 32|VDD

+--_--+ 忋|2 31|暯3 壓|2 31|愗

VDD|1 28|VDD 忋|3 30|暯3 壓|3 30|愗

A12|2 27|A14 壓|4 29|暯3 暯3|4 29|暯3

A 7|3 26|A13 壓|5 28|壓 暯3|5 28|暯3

A 6|4 25|A 8 壓|6 27|壓 愗|6 27|暯3

A 5|5 24|A 9 壓|7 26|壓 愗|7 26|暯3

A 4|6 23|A11 壓|8 25|壓 愗|8 25|VDD

A 3|7 22|/OE 壓|9 24|暯3 愗|9 24|暯3

A 2|8 21|A10 壓|10 23|壓 愗|10 23|暯3

A 1|9 20|/CS 壓|11 22|暯3 壓|11 22|暯3

A 0|10 19|D 7 壓|12 21|壓 壓|12 21|暯3

D 0|11 18|D 6 壓|13 20|壓 暯3|13 20|暯3

D 1|12 17|D 5 壓|14 19|壓 暯3|14 19|暯3

D 2|13 16|D 4 壓|15 18|壓 GND|15 18|暯3

GND|14 15|D 3 GND|16 17|壓 GND|16 17|暯3

+-----+ +-----+ +-----+

丂"忋"偼忋偵棃傞IC乮628512偐傜LZ93A13乯偵偮側偘傞偙偲丄"壓"偼壓偵棃傞IC乮LZ93A13偐傜628512傑偨偼628512偐傜32kB ROM乯偵偮側偘傞偙偲傪堄枴偟偰偄傑偡丅"暯3"偼懌傪悈暯偵怢偽偟偰3mm掱搙傪巆偟偰愗傞偙偲傪堄枴偟偰偄傑偡丅"愗"偼巊傢側偄偺偱崻尦偐傜愗偭偰偟傑偭偰峔偄傑偣傫丅偮偠偐傢偝傫偺僆儕僕僫儖偺夞楬偐傜LZ93A13偺Bx偲SRAM偺Axx偺慻傒崌傢偣丄LZ93A13偺A11丄A12偲628512偺A0丄A1偺慻傒崌傢偣傪曄偊偰偄傑偡丅僆儕僕僫儖偺夞楬偼儊僈儘儉僐儞僩儘乕儔乕偺嵹偭偨僎乕儉婎斅傪夵憿偡傞偙偲傪慜採偵慻傑傟偨暔偱丄崱夞偼HB-F500偵撪憼偡傞偨傔偺夞楬側偺偱岺嶌偟傗偡偄傛偆偵偡傞偨傔偱偡丅Bx偲SRAM偺Axx偼偳偆慻傒崌傢偣偰傕栤戣偁傝傑偣傫偑丄Bx偼斣崋偺彫偝偄傕偺偐傜巊偆昁梫偑偁傝丄B1傪巊傢偢偵B5傪巊偆偲偄偆傛偆側巊偄曽偼NG偱偡丅

丂岺嶌偺偟傗偡偝偐傜僆儕僕僫儖偺夞楬偐傜A0偲A1傪擖傟懼偊丄偦傟偵敽偄A14偲A15傕擖傟懼偊偰偄傑偡丅僨乕僞偺棳傟偼埲壓偺捠傝偵側傝傑偡丅

丂夞楬恾偺奃怓偺晹暘偼忋偺愢柧偱"忋"傑偨偼"壓"偱偮側偑傞晹暘偱偡丅32kB ROM帺懱偼壛岺偟傑偣傫偑丄SRAM偺3乣30僺儞偑32kB ROM偺1乣28僺儞偵廳側傞傛偆偵偟傑偡丅偝傜偵忋偵LZ93A13傪廳偹傑偡丅GND偼32kB ROM偵偦偺傑傑偮側偑傝傑偡偑VDD偼LZ93A13偲SRAM摨巑傪偮側偖偩偗偱柍偔丄婎斅偺5V傑偨偼32kB ROM偺28僺儞摍偵偮側偘傞昁梫偑偁傞偺偱拲堄偟偰壓偝偄丅

丂幚嵺偵幚憰偡傞偲偙傫側姶偠偵側傝傑偡丅

丂74LS00傗74LS138偼婎斅忋偺摨偠僺儞悢偺IC偺忋偵廳偹偰丄VDD偲GND偺傒偮側偘偰偄傑偡丅偙偙偱偼偦傟偧傟IC46偲IC54偺忋偵嵹偣傑偟偨丅/RESET偼夞楬恾偱偼IC57偵偮側偘偰偄傑偡偑偙偙偱偼IC39偲偮側偘偰偄傑偡丅偳偪傜偵偮側偘偰傕摨偠偱偡丅

丂傑偨丄傕偲傕偲嵹偭偰偄偨DRAM(IC55偲IC60)偼庢傝奜偟偰偔偩偝偄丅柺搢側傜DRAM偺1僺儞(/OE)傪婎斅偐傜愗傝棧偟偰VDD偲偮側偘偰偍偔偲偄偆曽朄傕偁傝傑偡丅

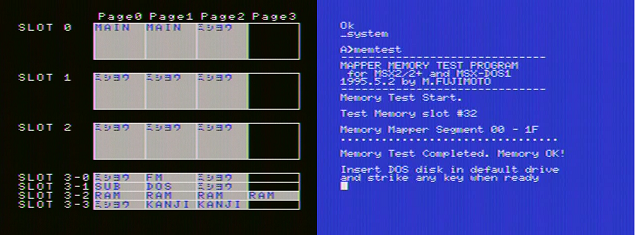

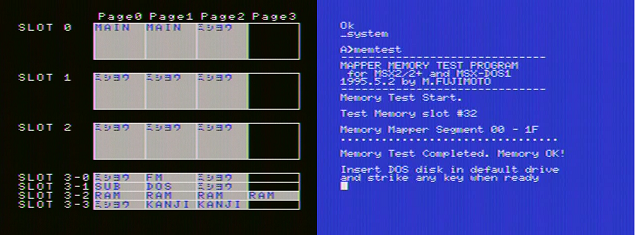

丂摗杮偝傫偺MEMTEST.COM(1MB儊儌儕僇乕僩儕僢僕惢嶌婰帠偵摨崼)偱傕摿偵儊儌儕僄儔乕偑側偔512kB偺擣幆偵惉岟偟傑偟偨丅

丂偍栺懇偱偡偑丄偙偺塡傪尒偰夵憿側偳傪峴偄屘忈傗偦偺懠栤戣偑敪惗偟偰傕愑擟偼晧偊傑偣傫丅奺帺偺愑擟偵偍偄偰忣曬傪峀偔廤傔偰峴偆偙偲傪偍偡偡傔偟傑偡丅